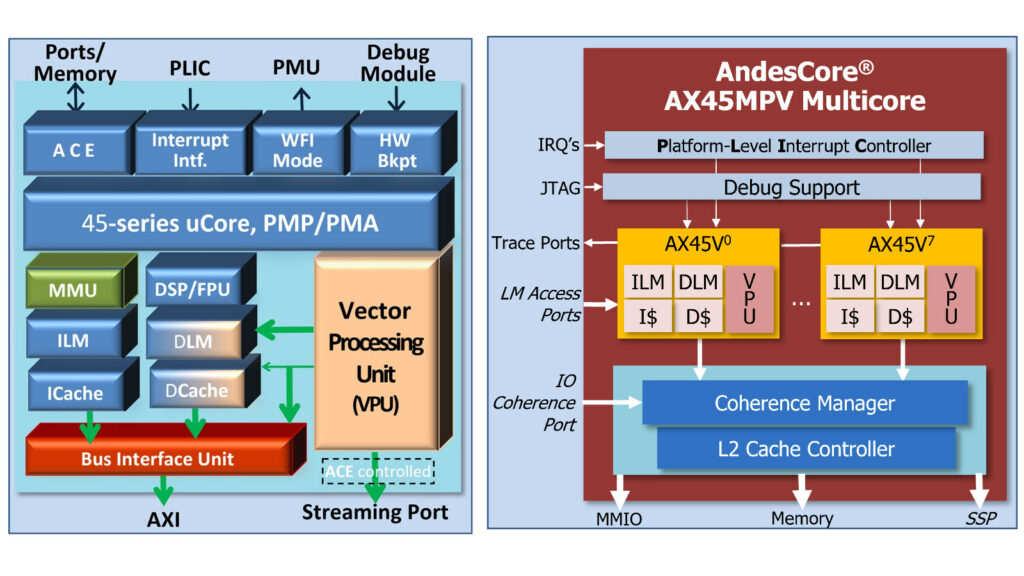

Недавно компания Andes Technology объявила о выпуске процессора AndesCore AX45MPV RISC-V, который создан на основе многоядерного процессора AX45MP и дополнен векторным расширением RISC-V 1.0.

Новое ядро ЦП RISC-V, оснащенное векторной обработкой RISC-V и возможностью параллельного выполнения, предназначено для SoC, обрабатывающего большие объемы данных для таких приложений, как ADAS, вывод и обучение искусственного интеллекта, AR/VR, мультимедиа, робототехника и обработка сигналов.

Ключевые особенности и характеристики AX45MPV:

- 64-разрядное 8-ступенчатое процессорное ядро двойного назначения с 1024-разрядным блоком векторной обработки (VPU) – совместимо с RISC-V V-extension (RVV) 1.0 + пользовательскими расширениями

- Поддерживает кластеры до 8 ядер.

- Поддержка кэша L2 и согласованности

- Векторная локальная память с высокой пропускной способностью (HVM)

- Архитектура набора команд AndeStar V5 (ISA)

- Совместимость с расширениями RISC-V GCBPV.

- Расширение производительности Andes

- Расширение Andes CoDense для дальнейшего уменьшения размера кода

- Отдельно лицензируемое расширение Andes Custom Extension (ACE) для индивидуальных скалярных и векторных инструкций.

- 64-разрядная архитектура для объема памяти более 4 ГБ

- Определение ветвления для ускорения работы управляющего кода

- Модуль управления памятью (MMU), защита физической памяти (PMP) и программируемый атрибут физической памяти (PMA)

- Усовершенствованный Andes контроллер прерываний на уровне платформы (PLIC) для системных событий и производительности в реальном времени.

- Поддержка контроллера прерываний на уровне платформы (PLIC) с организацией вытесняющих прерываний.

- ECC или проверка четности для защиты от ошибок SRAM

- Настраиваемая длина вектора VPU (VLEN) и длина пути передачи данных (DLEN)

- Аппаратное обеспечение StackSafe, помогающее измерить размер стека и обнаружить переполнение/недополнение во время выполнения.

- Универсальные конфигурации для достижения компромисса между размером ядра и требованиями к производительности.

- PowerBrake и WFI (ожидание прерывания) для различных случаев энергосбережения

Andes предоставит несколько инструментов разработки для ядер AX45MPV, включая AndeSight IDE на базе Eclipse, платы разработки AndeShape FPGA, инструмент автоматизации COPILOT для Andes Custom Extension, анализатор и визуализатор конвейера процессора AndesClarity, а также библиотеку AndeSoft NN, оптимизированную для RISC-V DSP/ расширения SIMD и Vector.

Несколько клиентов из Азии и Северной Америки уже приобрели лицензию на AX45MPV, и хотя нам неизвестно, какие именно, микропроцессор Renesas RZ/Five RISC-V с поддержкой Linux использует более раннее ядро AX45MP, и, не удивительно, если в скором времени появится продолжение AX45MPV, использующего расширение RISC-V для рабочих нагрузок искусственного интеллекта.

Andes говорит, что стандартный пакет AX45MPV доступен уже сейчас, но более продвинутый пакет с поддержкой Linux будет доступен только в четвертом квартале 2023 года. В любом случае, мы полагаем, что AX45MPV SoC появится не раньше 2024 года. Более подробную информацию можно найти на странице продукта и в пресс-релизе.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.