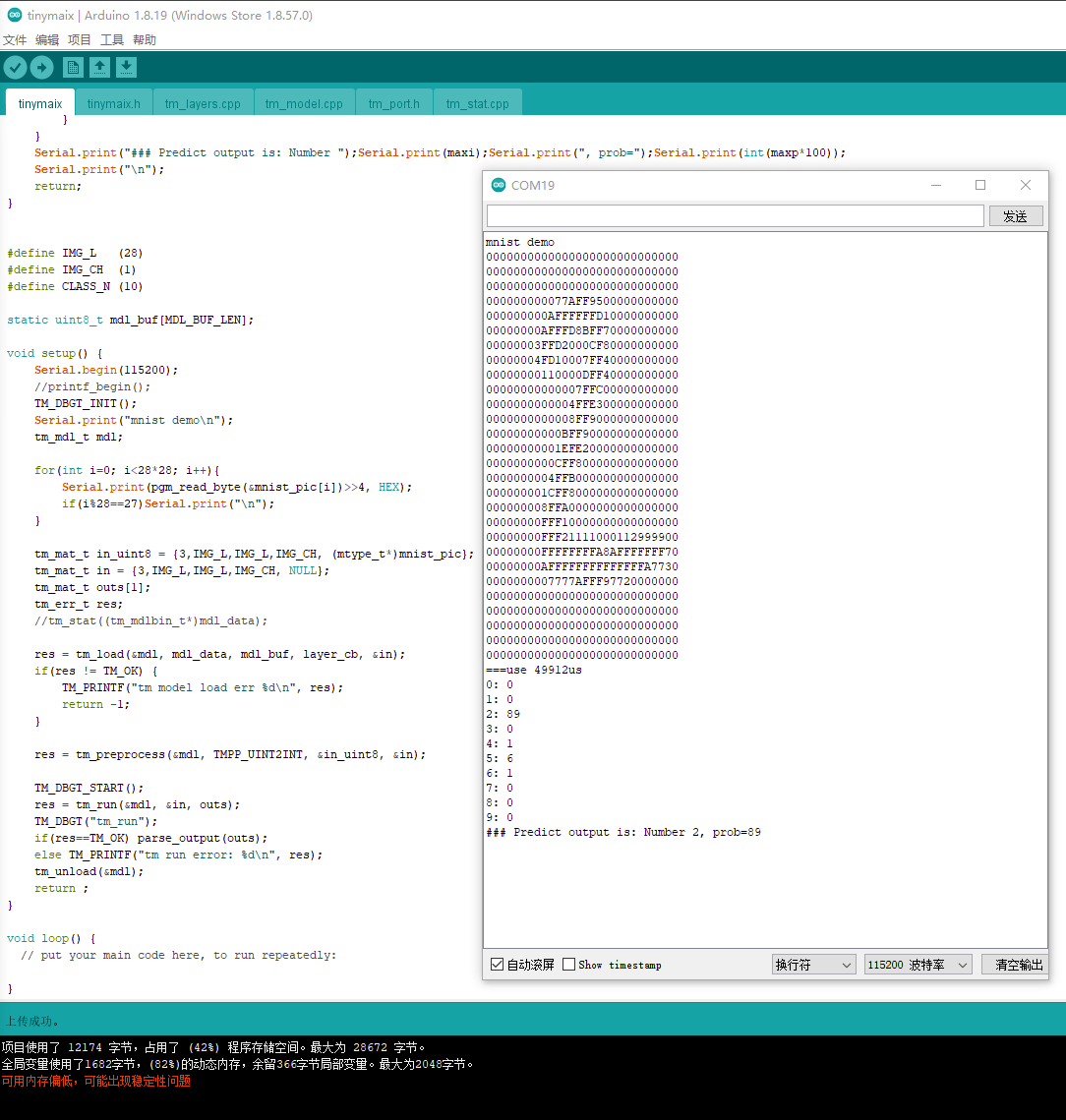

Библиотека машинного обучения с открытым исходным кодом Sipeed TinyMaix разработана для микроконтроллеров и достаточно легкая, чтобы работать на микроконтроллере Microchip ATmega328, установленном на плате Arduino UNO и ее многочисленных клонах.

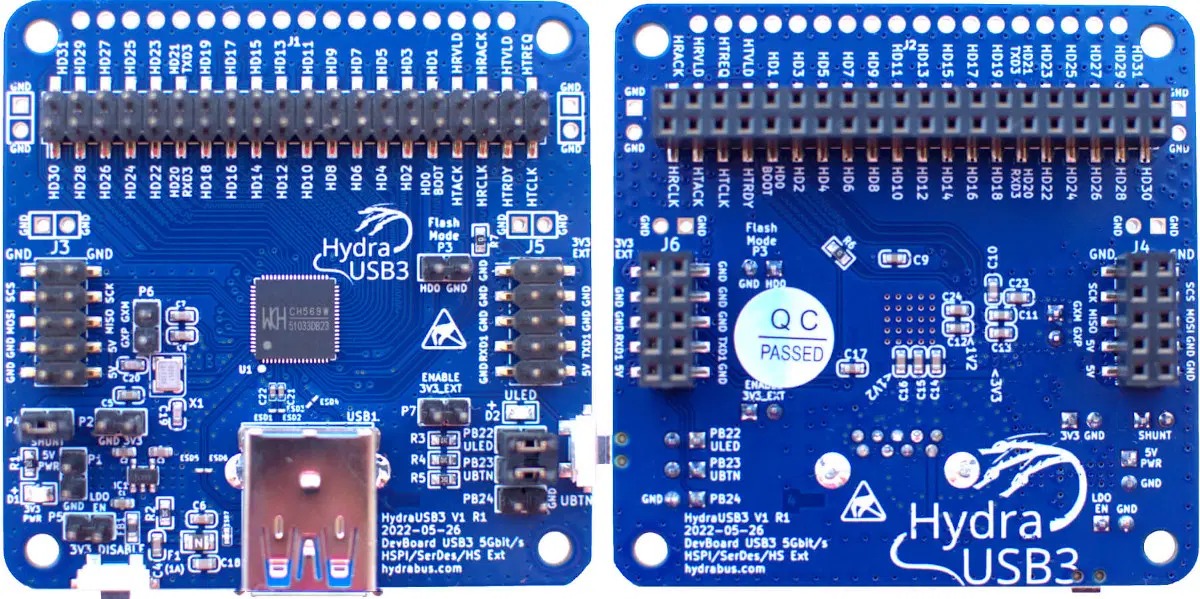

Читать далее «TinyMaix — это легкая библиотека машинного обучения для микроконтроллеров.»Плата HydraUSB3 RISC-V MCU сочетает в себе USB 3.0 с высокоскоростными интерфейсами HSPI и SerDes.

Benjamin VERNOUX выпустил плату HydraUSB3 V1 на базе микроконтроллера WCH CH569 RISC-V в качестве платформы для разработчиков, позволяющей экспериментировать с высокоскоростными протоколами, такими как HSPI и SerDes, через интерфейс USB 3.0.

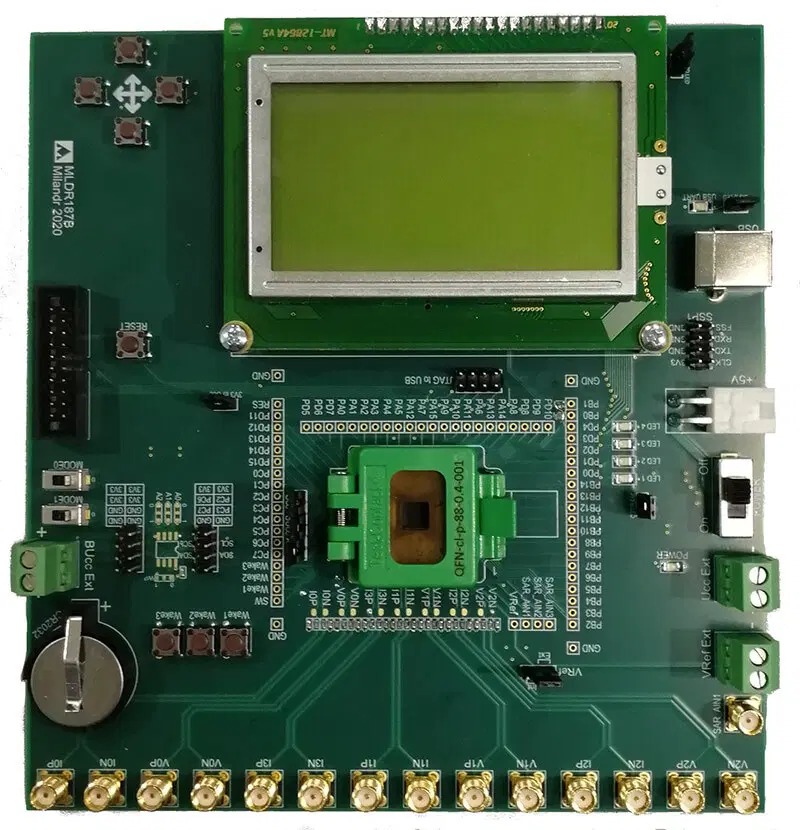

Читать далее «Плата HydraUSB3 RISC-V MCU сочетает в себе USB 3.0 с высокоскоростными интерфейсами HSPI и SerDes.»Milandr MDR32F02FI — микроконтроллер RISC-V для (российских) счетчиков электроэнергии

В прошлом году мы писали о российском микроконтроллере Mikron MIK32 RISC-V с функциями, аналогичными STM32L0 Arm Cortex-M0+, а недавно стало известно, что первые полностью упакованные образцы ожидаются в конце осени.

Но оказывается, есть еще одна российская компания, которая производит микроконтроллеры RISC-V, и, например, Milandr MDR32F02FI имеет ядро BM-310 RISC-V MCU с открытым исходным кодом и специально разработан для счетчиков электроэнергии. Это второе поколение микроконтроллера, первое из которых основано на ядре Arm Cortex-M0 и производится более 5 лет.

Читать далее «Milandr MDR32F02FI — микроконтроллер RISC-V для (российских) счетчиков электроэнергии»Паяльник Pinecil V2 получил микроконтроллер BL706 Bluetooth LE RISC-V, поддержку USB PD EPR

PINE64 собирается выпустить паяльник Pinecil RISC-V второго поколения с Pinecil V2, оснащенный новым микроконтроллером Bouffalo Lab BL706 RISC-V с возможностью подключения Bluetooth LE, оптимизацией для более высоких уровней мощности, а также предварительной поддержкой нового стандарта USB PD EPR (расширенный диапазон мощности), работающего при напряжении до 28 В.

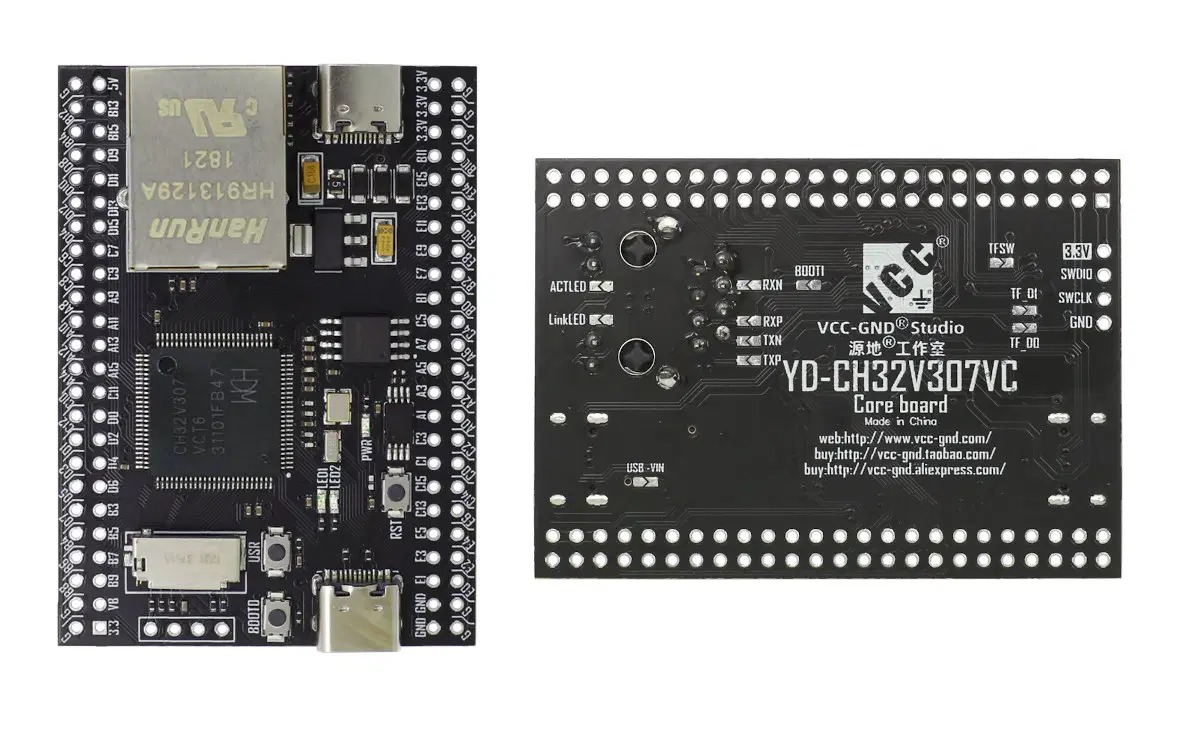

Читать далее «Паяльник Pinecil V2 получил микроконтроллер BL706 Bluetooth LE RISC-V, поддержку USB PD EPR»Плата микроконтроллера YD-CH32V307VCT6 RISC-V поставляется с Ethernet и большим количеством входов/выходов.

В начале года мы писали о микроконтроллере WCH CH32V307 RISC-V и макетной плате с 8х портами UART, управляемыми по Ethernet. Теперь нам сообщили о похожем устройстве, но гораздо более компактном VCC-GND Studio под названием «YD-CH32V307VCT6».

Помимо микроконтроллера RISC-V с частотой 144 МГц, плата оснащена портом Ethernet 10 Мбит/с, двумя портами USB Type-C, флэш-памятью SPI, EEPROM, разъемом для карты microSD и четырьмя рядами по 24 контакта в каждом, всего 96 контактов, открывающих все контакты из корпуса LQFP100.

Читать далее «Плата микроконтроллера YD-CH32V307VCT6 RISC-V поставляется с Ethernet и большим количеством входов/выходов.»Seeed Studio выпускает плату XIAO ESP32C3 за 5 долларов с WiFi и BLE, поддержкой батареи

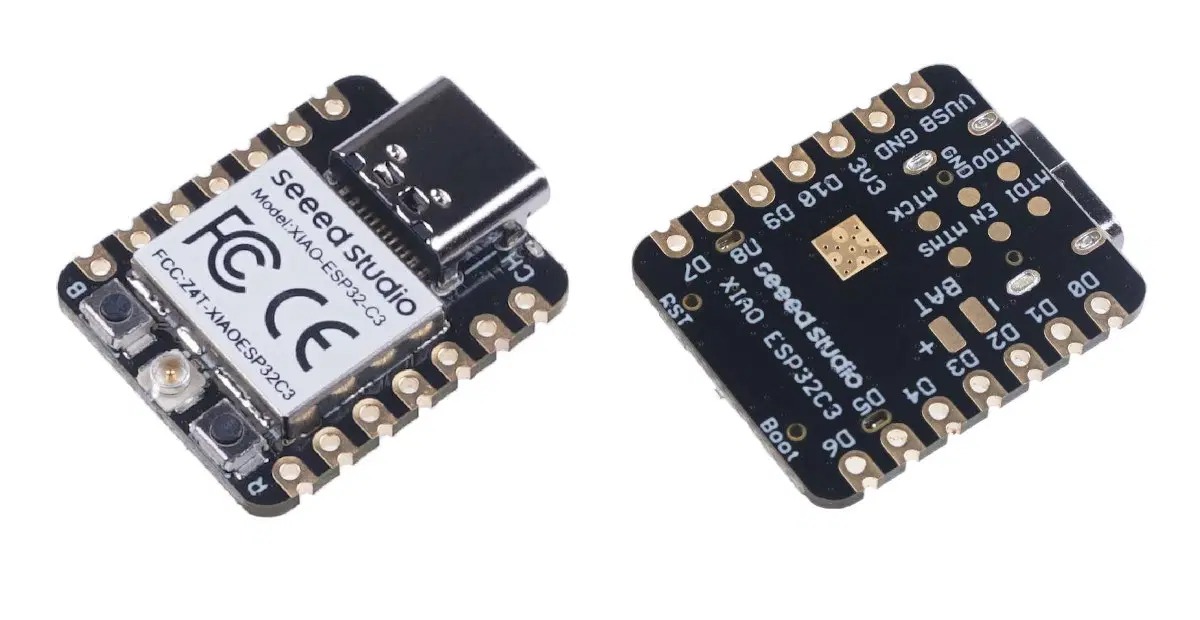

Семейство миниатюрных плат MCU XIAO от Seeed Studio расширяется еще одной платой XIAO ESP32C3, оснащенной микроконтроллером ESP32-C3 WiFi и Bluetooth LE (BLE), поддержкой аккумуляторов LiPo и тем же форм-фактором 21 x 17,5 мм.

Если мы правильно умеем считать, то это уже пятая плата после оригинальной платы XIAO на базе микроконтроллера Microchip SAMD21G18 Cortex-M0+, XIAO RP2040 и плат XIAO BLE и XIAO BLE Sense на базе nRF52840, которые мы тестировали с помощью Edge Impulse.

Читать далее «Seeed Studio выпускает плату XIAO ESP32C3 за 5 долларов с WiFi и BLE, поддержкой батареи»Ноутбук ROMA на базе Linux с четырехъядерным процессором с архитектурой RISC-V, поддержкой Web3, NFT, криптовалют и т. д.

ROMA — это ноутбук на базе операционной системы Linux, оснащенный неназванным четырехъядерным процессором с архитектурой RISC-V, графическим процессором и NPU, до 16 ГБ ОЗУ, 256 ГБ памяти, в первую очередь предназначенный для разработчиков программного обеспечения с интеграцией технологии Web3.

Читать далее «Ноутбук ROMA на базе Linux с четырехъядерным процессором с архитектурой RISC-V, поддержкой Web3, NFT, криптовалют и т. д.»В ближайшее время могут появиться ноутбук RISC-V или мини-ПК с производительностью класса Rockchip RK3588

Марк Химельштейн (Mark Himelstein), главный технический директор RISC-V International, и доктор Филипп Томсич (Dr. Philipp Tomsich), главный технолог и основатель VRULL GmbH, намекнули, что мы можем увидеть ноутбук RISC-V в 2022 году в презентации под названием « От технологии к продукту — развитие экосистем RISC-V» на одном из слайдов был показан прототип ноутбука RISC-V, и The Register подозревал, заподозрил, что он может быть создан Институтом программного обеспечения Китайской академии наук (ISCAS), поскольку он планировал построить 2000 ноутбуков RISC-V к концу 2022 года..

Читать далее «В ближайшее время могут появиться ноутбук RISC-V или мини-ПК с производительностью класса Rockchip RK3588»