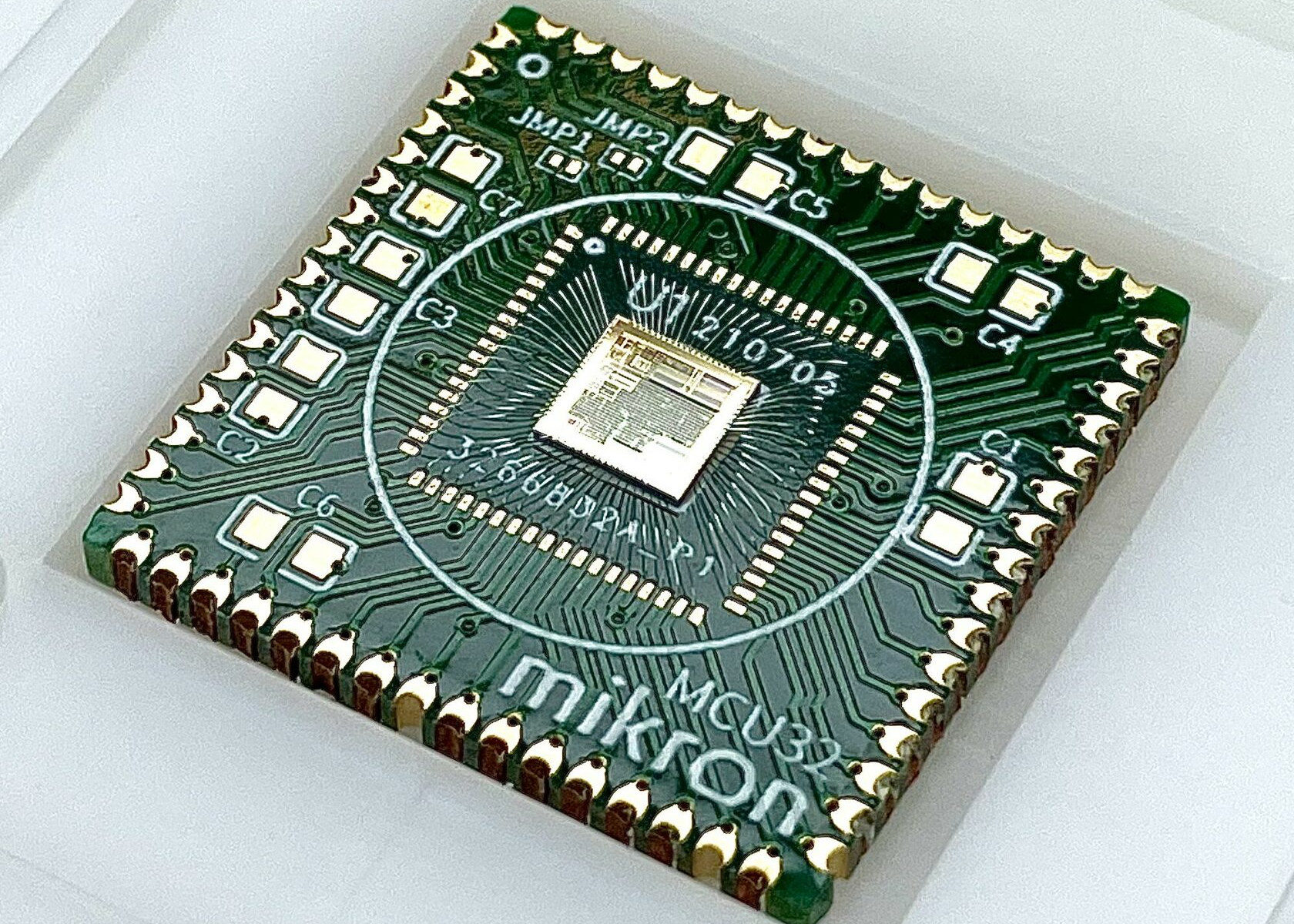

Mikron MIK32 – это 32-битный микроконтроллер RISC-V российского производства с функциями, аналогичными MCU STMicro STM32L0 Cortex-M0 +, который показывает, как архитектура с открытым исходным кодом RISC-V может позволить большему количеству компаний разрабатывать свои собственные чипы.

Микроконтроллер MIK32 имеет процессорный IP от Syntacore, базирующегося в Санкт-Петербурге, в соответствии с профилем RV32IMC. MCU с тактовой частотой 32 МГц поставляется с интерфейсами I2C, UART, SPI, ADC, DAC, а также различными таймерами, контроллером прерываний и многим другим.

Читать далее «Mikron MIK32 – сделанный в России 32-битный микроконтроллер RISC-V предлагает функции, аналогичные микроконтроллеру STM32L0»