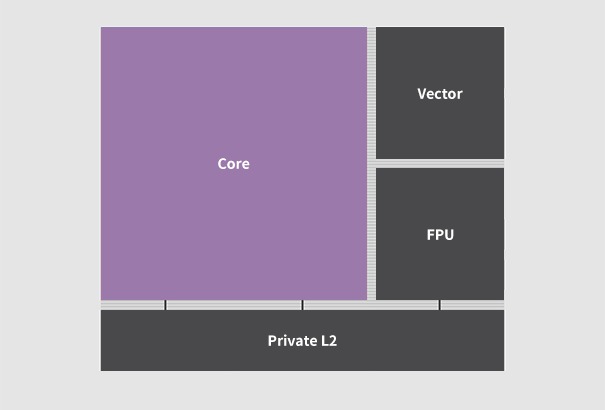

На днях компания StarFive анонсировала поставку клиентам 64-битного ядра RISC-V Dubhe на основе RV64GC ISA плюс битовые манипуляции, прерывания на уровне пользователя, а также новейшие инструкции Vector 1.0 (V) и Hypervisor (H).

Читать далее «64-битное ядро RISC-V StarFive Dubhe можно будет встретить в 12-нм процессорах с тактовой частотой 2 ГГц»Процессоры Sifive Essential 6-Series RISC-V нацелены на Linux и приложения реального времени

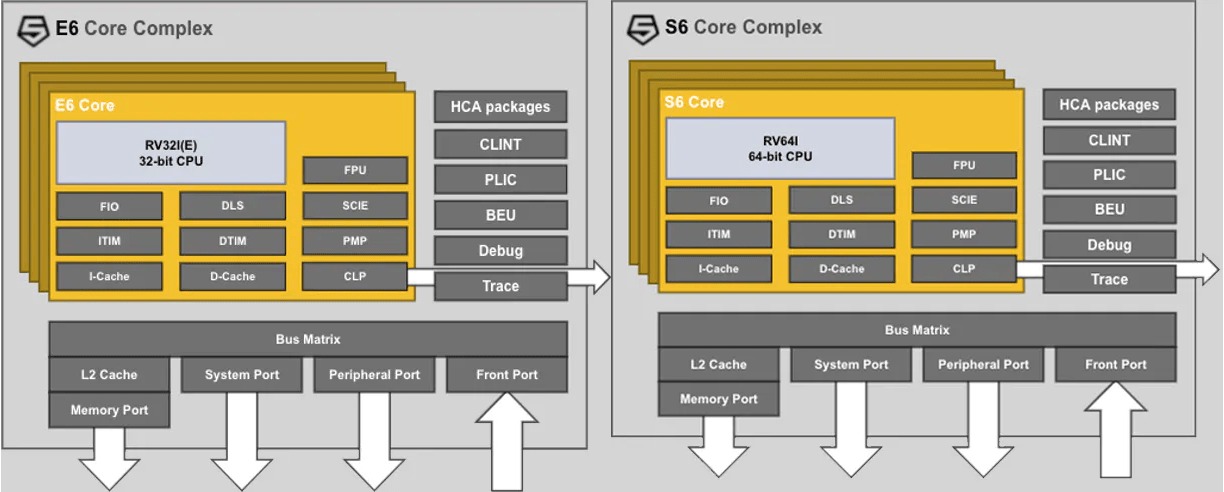

Всего через несколько дней после анонса SiFive Performance P650 компания SiFive анонсировала семейство процессоров SiFive Essential 6-Series RISC-V, включающее четыре 64-битных/32-битных ядра реального времени и два ядра приложений с поддержкой Linux, а также SiFive 21G3 с различными улучшениями существующих семейств.

Читать далее «Процессоры Sifive Essential 6-Series RISC-V нацелены на Linux и приложения реального времени»Стартовали официальные продажи одноплатного компьютера StarFive VisionFive, ускоряющего развитие экосистемы RISC-V

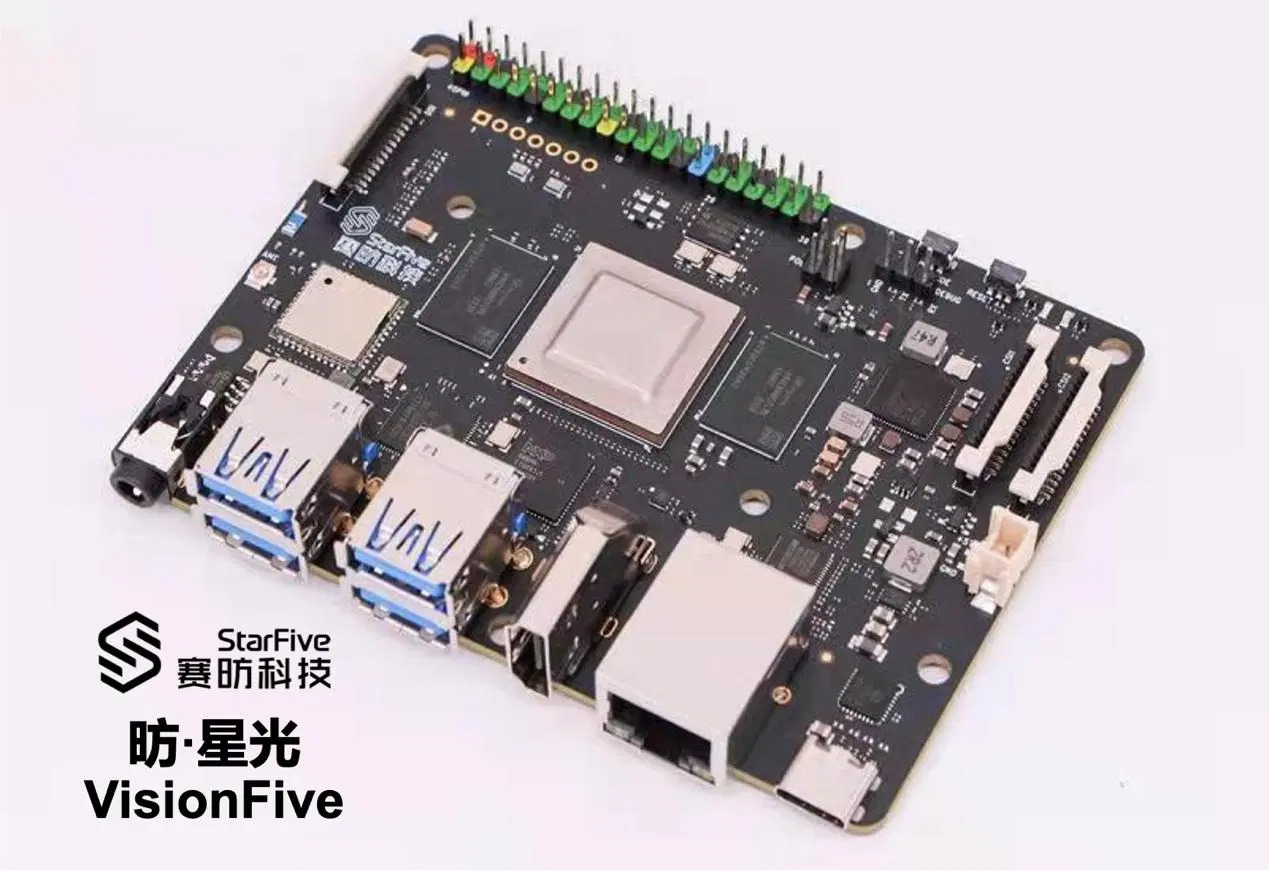

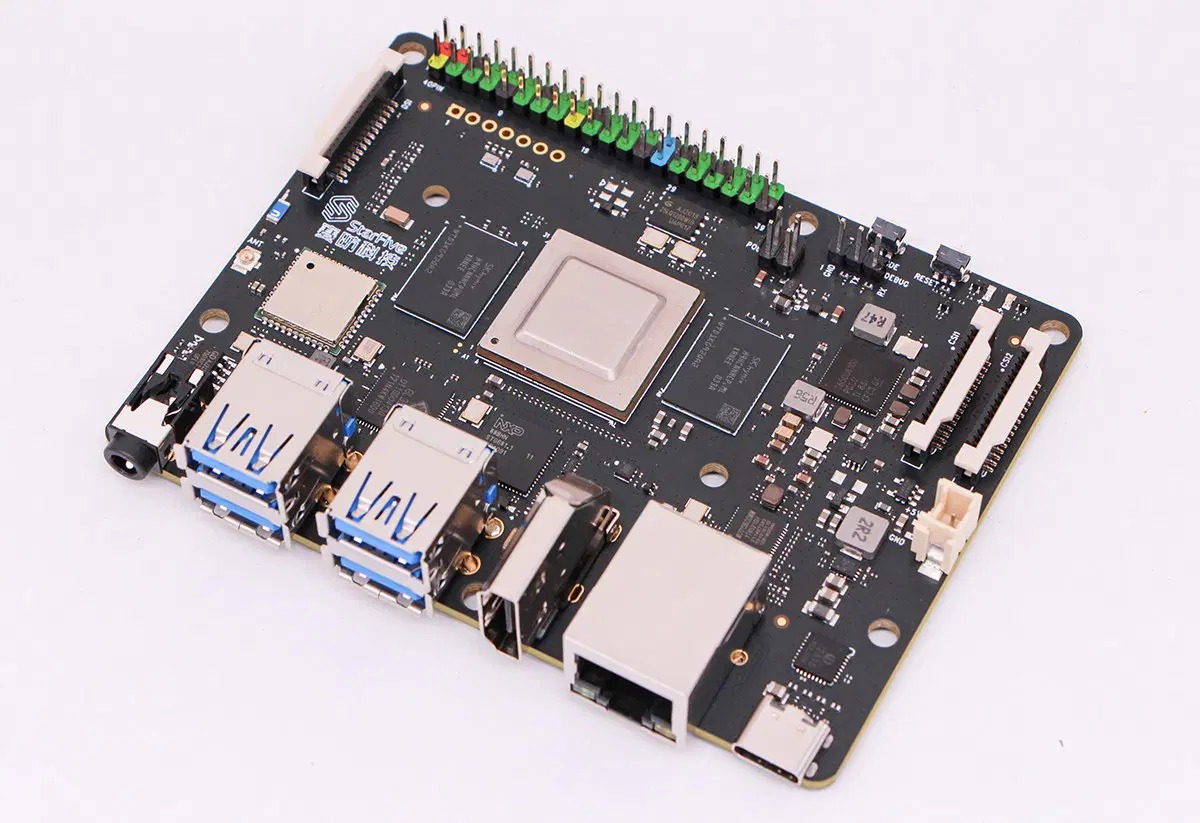

Сан-Франциско, США — 8 декабря 2021 г. — на саммите RISC-V 2021 компания StarFive Technology Co., Ltd. (далее «StarFive»), лидер экосистемы программного и аппаратного обеспечения RISC-V в Китае, объявила о официальном старте продаж одноплатного компьютера «VisionFive». Доступность VisionFive означает прорыв в оборудовании RISC-V для высокопроизводительных приложений, помогающего ускорить внедрение инноваций в глобальной индустрии RISC-V и способствовать совершенствованию и развитию экосистемы программного обеспечения с открытым исходным кодом для стимулирования реализации более инновационных приложений RISC-V верхнего уровня.

Читать далее «Стартовали официальные продажи одноплатного компьютера StarFive VisionFive, ускоряющего развитие экосистемы RISC-V»Imagination представляет ядра ЦП Catapult RISC-V

Как и ожидалось, компания Imagination Technologies, после своей предыдущей неудачной попытки с архитектурой MIPS, особенно с семейством Aptiv, делает еще одну попытку выйти на рынок ЦП с ядрами ЦП Catapult RISC-V.

Читать далее «Imagination представляет ядра ЦП Catapult RISC-V»Модуль ESP 32-C3 AWS IoT Express Link и комплект разработчика направлены на упрощение подключения к сервисам AWS IoT

Amazon и Espressif, прошлым летом сотрудничающие по запуску модуля ESP32-PICO-V3-ZERO Alexa Connect Kit, запустили еще один беспроводной модуль вместе с комплектом средств разработки – модуль ESP32-C3 AWS IoT ExpressLink, поддерживающие готовое подключение к AWS IoT.

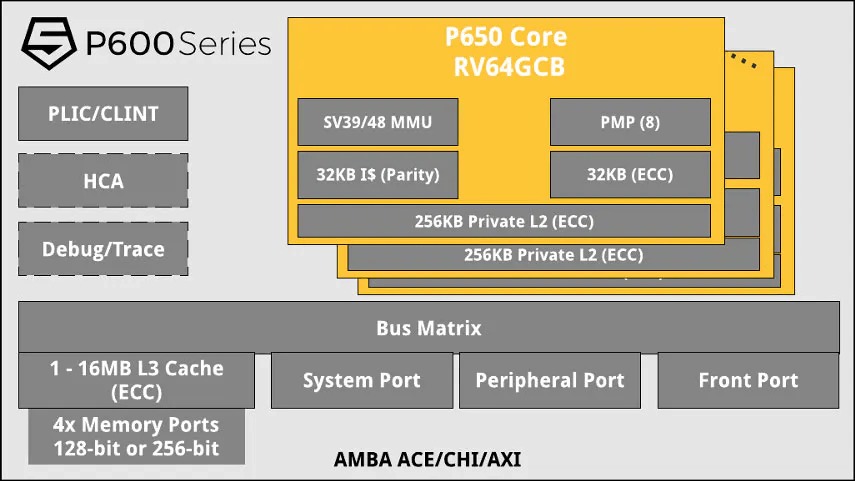

Ядро SiFive Performance P650 RISC-V превосходит Arm Cortex-A77 по производительности на мм2

Около шести месяцев прошло с тех пор SiFive анонса Performance P550 «быстрый 64-битный RISC-V процессор», и теперь компания представила еще более быстрый RISC-V ядро с Performance P650, который, как ожидается, соответствует производительности Cortex-A77.

Читать далее «Ядро SiFive Performance P650 RISC-V превосходит Arm Cortex-A77 по производительности на мм2»VisionFive V1 RISC-V Linux SBC возрождает одноплатный компьютер BeagleV

Прошлым летом мы сообщили, что BeagleV StarFive RISC-V SBC не будет производиться, но не все потеряно, поскольку StarFive будет сотрудничать с Radxa, чтобы создать новый одноплатный компьютер на базе их двухъядерного 64-битного процессора RISC-V JH7100.

Читать далее «VisionFive V1 RISC-V Linux SBC возрождает одноплатный компьютер BeagleV»Sipeed LicheeRV — плата Allwinner D1 Linux RISC-V за 16,90 долларов США

Наконец-то! Теперь есть гораздо более доступная плата Allwinner D1 RISC-V Linux — Sipeed LicheeRV Nezha CM SBC, продаваемая на Aliexpress по цене 16,90 долларов и выше, это намного меньше, чем 100 долларов, запрошенные за Nezha SBC, это невероятно дешево, как мы увидим из спецификации ниже.

Читать далее «Sipeed LicheeRV — плата Allwinner D1 Linux RISC-V за 16,90 долларов США»