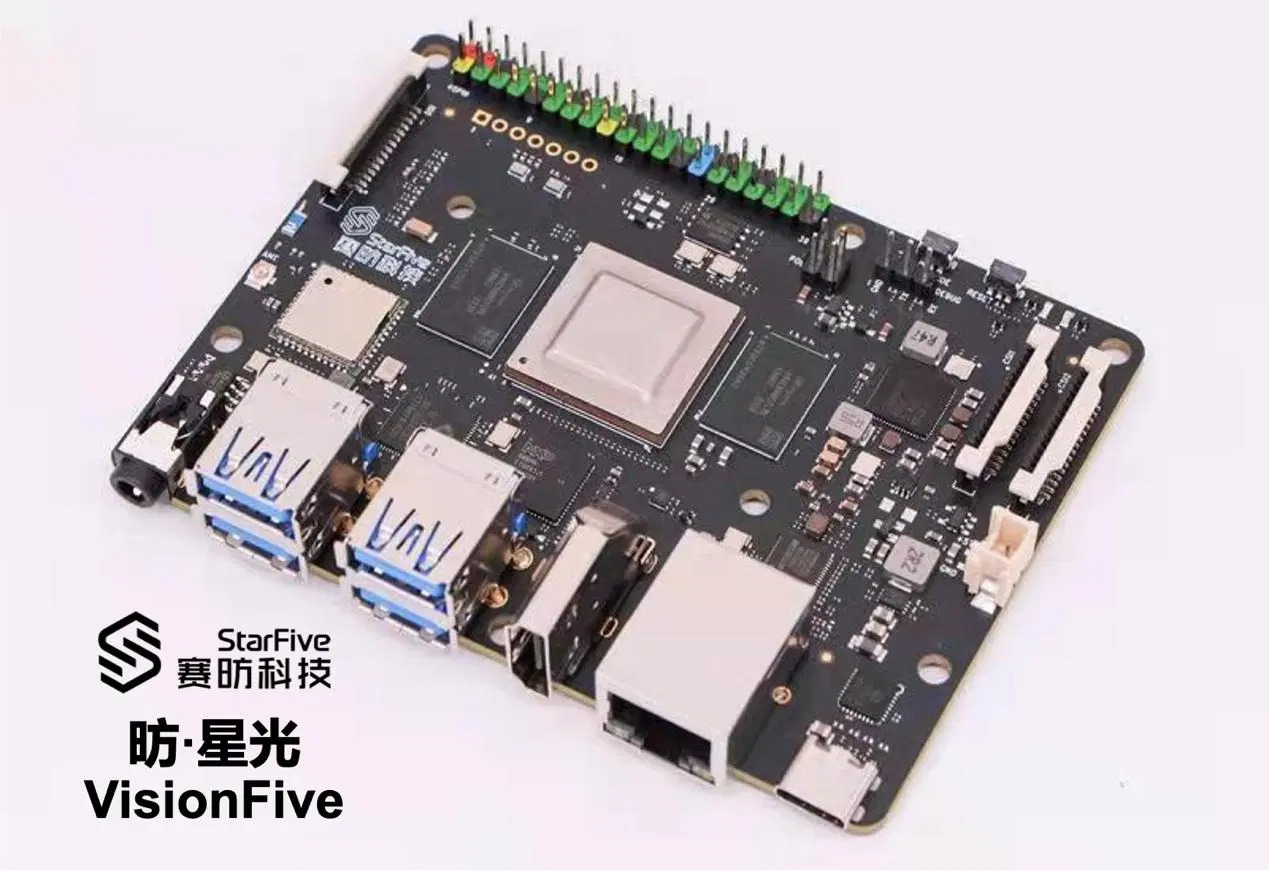

Сан-Франциско, США — 8 декабря 2021 г. — на саммите RISC-V 2021 компания StarFive Technology Co., Ltd. (далее «StarFive»), лидер экосистемы программного и аппаратного обеспечения RISC-V в Китае, объявила о официальном старте продаж одноплатного компьютера «VisionFive». Доступность VisionFive означает прорыв в оборудовании RISC-V для высокопроизводительных приложений, помогающего ускорить внедрение инноваций в глобальной индустрии RISC-V и способствовать совершенствованию и развитию экосистемы программного обеспечения с открытым исходным кодом для стимулирования реализации более инновационных приложений RISC-V верхнего уровня.

Читать далее «Стартовали официальные продажи одноплатного компьютера StarFive VisionFive, ускоряющего развитие экосистемы RISC-V»Imagination представляет ядра ЦП Catapult RISC-V

Как и ожидалось, компания Imagination Technologies, после своей предыдущей неудачной попытки с архитектурой MIPS, особенно с семейством Aptiv, делает еще одну попытку выйти на рынок ЦП с ядрами ЦП Catapult RISC-V.

Читать далее «Imagination представляет ядра ЦП Catapult RISC-V»Модуль ESP 32-C3 AWS IoT Express Link и комплект разработчика направлены на упрощение подключения к сервисам AWS IoT

Amazon и Espressif, прошлым летом сотрудничающие по запуску модуля ESP32-PICO-V3-ZERO Alexa Connect Kit, запустили еще один беспроводной модуль вместе с комплектом средств разработки – модуль ESP32-C3 AWS IoT ExpressLink, поддерживающие готовое подключение к AWS IoT.

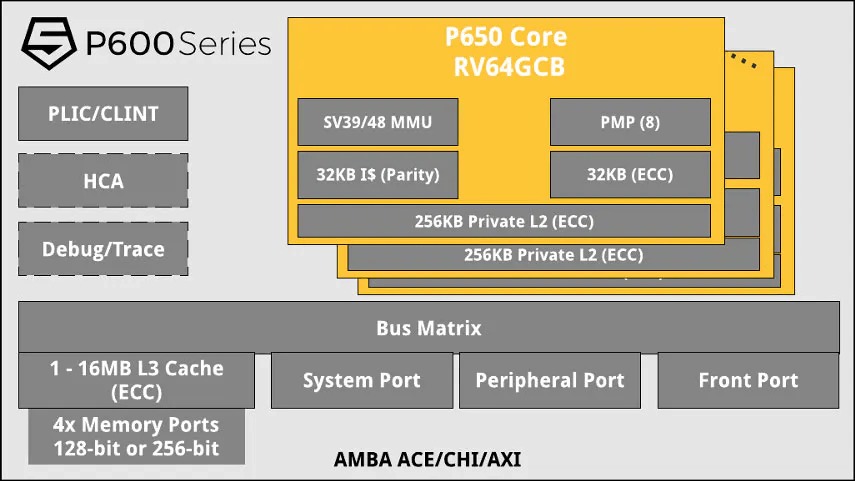

Ядро SiFive Performance P650 RISC-V превосходит Arm Cortex-A77 по производительности на мм2

Около шести месяцев прошло с тех пор SiFive анонса Performance P550 «быстрый 64-битный RISC-V процессор», и теперь компания представила еще более быстрый RISC-V ядро с Performance P650, который, как ожидается, соответствует производительности Cortex-A77.

Читать далее «Ядро SiFive Performance P650 RISC-V превосходит Arm Cortex-A77 по производительности на мм2»VisionFive V1 RISC-V Linux SBC возрождает одноплатный компьютер BeagleV

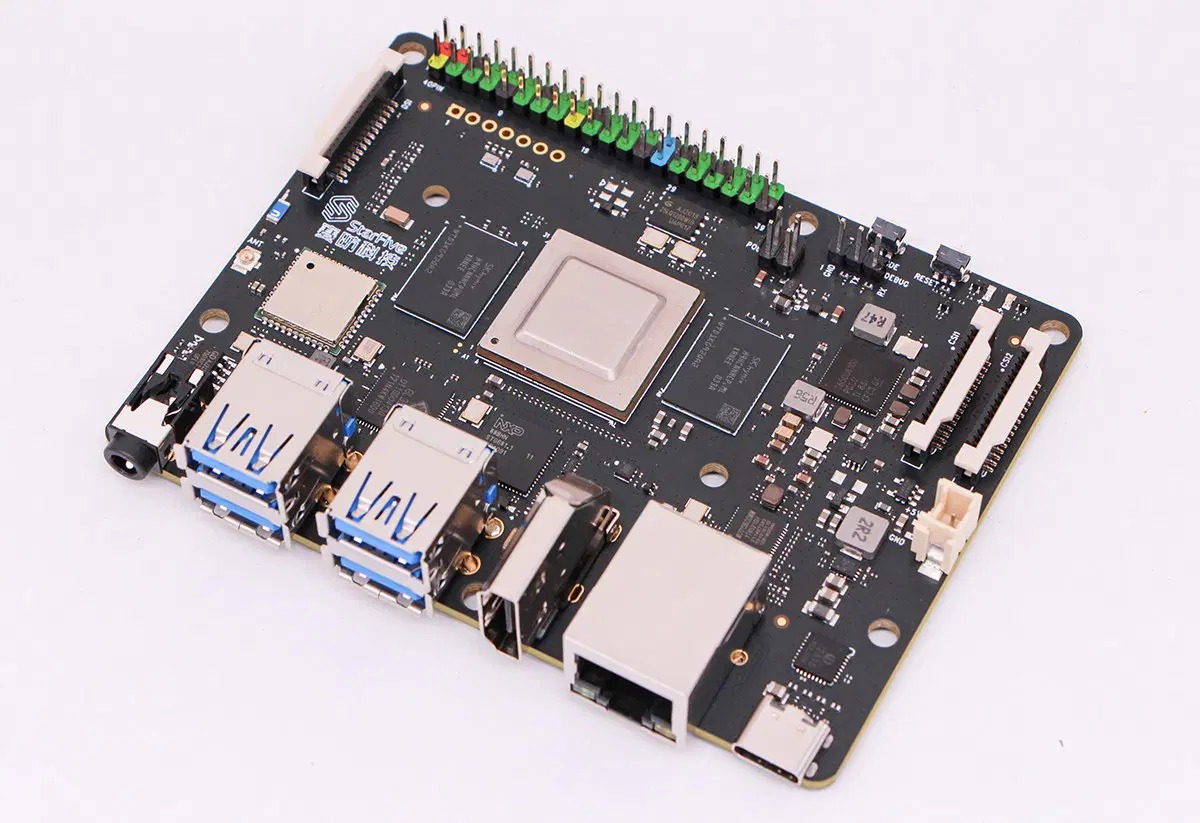

Прошлым летом мы сообщили, что BeagleV StarFive RISC-V SBC не будет производиться, но не все потеряно, поскольку StarFive будет сотрудничать с Radxa, чтобы создать новый одноплатный компьютер на базе их двухъядерного 64-битного процессора RISC-V JH7100.

Читать далее «VisionFive V1 RISC-V Linux SBC возрождает одноплатный компьютер BeagleV»Sipeed LicheeRV — плата Allwinner D1 Linux RISC-V за 16,90 долларов США

Наконец-то! Теперь есть гораздо более доступная плата Allwinner D1 RISC-V Linux — Sipeed LicheeRV Nezha CM SBC, продаваемая на Aliexpress по цене 16,90 долларов и выше, это намного меньше, чем 100 долларов, запрошенные за Nezha SBC, это невероятно дешево, как мы увидим из спецификации ниже.

Читать далее «Sipeed LicheeRV — плата Allwinner D1 Linux RISC-V за 16,90 долларов США»Встречайте сверхмалые модули ESP-C3-M1 и ESP-C3-M1-I серии ESP32-C3 mini

Полгода назад Ai-Thinker выпустил новые модули серии ESP32-C3, которые полностью совместимы по выводам с ESP8266, а именно ESP-C3-12F, ESP-C3-32S, ESP-C3-01M, ESP-C3-13, ESP-C3-13U. Через несколько месяцев компания получила дополнительные требования к модулям, особенно в отношении размера. Итак, исходя из спроса, Ai-Thinker дополнила семейство серией ESP-C3 mini, начав с двух модулей: ESP32-C3-M1 и ESP-C3-M1-I размером 16,6 × 13,2 мм и 12,5 × 13,2 мм, соответственно.

Читать далее «Встречайте сверхмалые модули ESP-C3-M1 и ESP-C3-M1-I серии ESP32-C3 mini»Автомобильный микроконтроллер Renesas RH850 / U2B оснащен параллельным сопроцессором на основе RISC-V

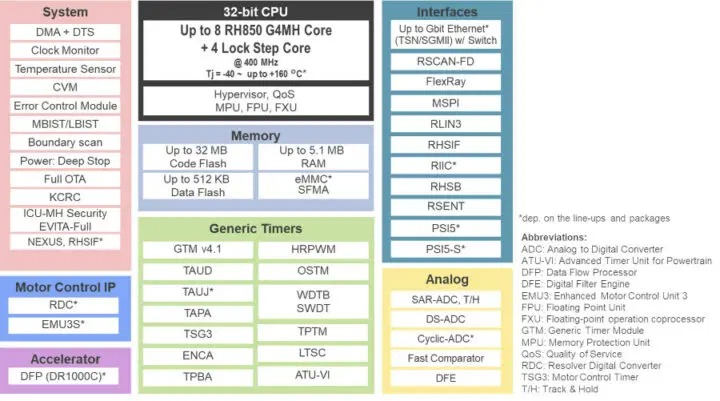

Renesas Electronics RH850 / U2B — это автомобильный микроконтроллер, предназначенный для электронного блока управления (ECU), который используется для гибридных ICE и тяговых двигателей (инверторов) xEV, высокопроизводительного управления зонами, подключенных шлюзов и применениях для движения транспортных средств.

Процессор включает в себя до восьми 32-битных производительных RISC-ядер RH850 с частотой 400 МГц, четыре из которых имеют архитектуру lockstep для соответствия стандартам ASIL-D и ASIL-B, а также параллельный сопроцессор DR1000C на основе RISC-V (процессор потока данных) с векторным расширением (DFP) от NSITEXE, который предназначен для поддержки “быстрого выполнения сложных математических алгоритмов”. Читать далее «Автомобильный микроконтроллер Renesas RH850 / U2B оснащен параллельным сопроцессором на основе RISC-V»