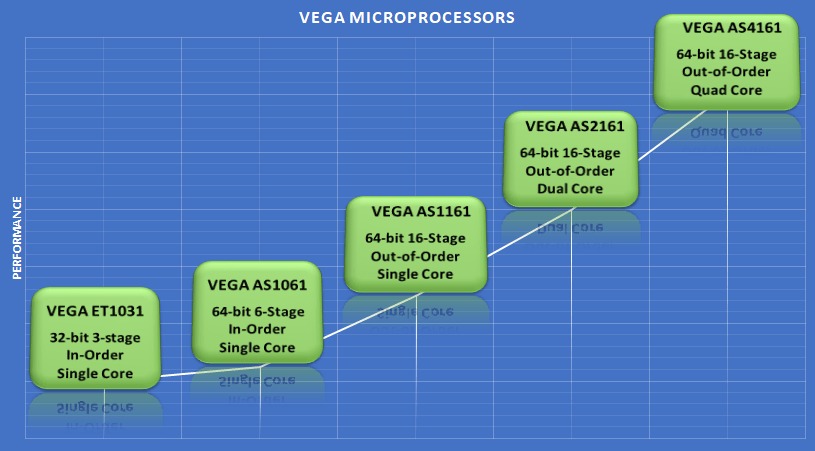

Одно из основных преимуществ архитектуры RISC-V заключается в том, что она открыта, поэтому любая организация с нужными навыками может разрабатывать свои собственные ядра, и правительство Индии воспользовалось этой возможностью, разработав Программу развития микропроцессоров (MDP), которая помогает разрабатывать ядра VEGA RISC-V на местном уровне.

Читать далее «Индия переходит на архитектуру RISC-V с процессорами VEGA»