Arm Cortex-M52 — это новое ядро микроконтроллера с технологией Arm Helium, предназначенное для реализации возможностей искусственного интеллекта в меньших по размеру и более дешевых IoT-устройствах, чем это уже возможно с процессоре на базе ядра Arm Cortex-M55.

Ключевые особенности и характеристики Arm Cortex-M52:

- Архитектура — Armv8.1-M

- Интерфейсы шины

- 32-разрядная основная системная шина AMBA 5 AXI или 32-разрядная системная шина AMBA 5 AHB

- 32-разрядная периферийная шина AMBA 5 AHB

- 32-разрядная шина доступа TCM AMBA 5 AHB (подчиненный порт)

- Pipeline – 4-ступенчатый pipeline

- Безопасность

- Технология Arm TrustZone (дополнительно) с дополнительным блоком атрибуции безопасности (SAU) до 8 регионов. Проверка лимита стека.

- Дополнительная поддержка расширения PACBTI (аутентификация указателя, идентификация цели ветки)

- Защита памяти — дополнительные модули защиты памяти (MPU) для изоляции процессов с использованием до 16 регионов MPU и фонового региона — если реализована TrustZone, могут быть защищенные и незащищенные MPU.

- Расширение DSP – 32-битное расширение DSP/SIMD

- Дополнительный однобитовый Helium, поддерживающий до

- 1x 32-битный MAC/цикл

- 2x 16-битных MAC/цикл

- 4x 8-битных MAC/цикл

- Модуль с плавающей запятой (FPU) — дополнительный FPU с поддержкой операций с плавающей запятой половинной точности (fp16), одинарной точности (fp32) и двойной точности (fp64).

- Поддержка ускорителя

- Дополнительный интерфейс сопроцессора (64-разрядный), поддерживающий до 8 блоков сопроцессора для пользовательских ускорителей вычислений.

- Дополнительные инструкции по изготовлению руки

- Кэш инструкций – до 64 КБ с ECC (опционально)

- Кэш данных – до 64 КБ с ECC (опционально)

- Инструкция TCM (ITCM) — до 16 МБ с ECC (опция)

- Данные TCM (DTCM) — до 16 МБ с ECC (опция)

- Прерывания — Встроенный Nested Vectored Interrupt Controller (NVIC), поддерживающий до 480 прерываний + Non-maskable interrupt (NMI). Количество уровней приоритета настраивается от 8 до 256.

- Wake-up Interrupt Controller (WIC) — внутренний и/или внешний (дополнительно) WIC для пробуждения процессора после отключения питания с сохранением состояния или при остановке всех тактовых импульсов.

- Поддержка низкого энергопотребления

- Архитектурно определенные режимы сна и глубокого сна.

- Встроенные инструкции ожидания события (WFE) и ожидания прерывания (WFI) с функцией сна при выходе.

- Сигналы индикации сна и глубокого сна

- Несколько доменов питания с дополнительной поддержкой сохранения памяти и логики

- Эффективность производительности: 4,3 CoreMark/МГц и 1,6 DMIPS/МГц.

- Отладчик

- Аппаратные и программные точки останова

- Performance Monitoring Unit (PMU)

- Trace

- Дополнительная трассировка инструкций со встроенной модулем ETM (Embedded Trace Macrocell), трассировкой данных (DWT) (выборочная трассировка данных) и трассировкой приборов (ITM) (программная трассировка)

- Надежность

- ECC для кэша инструкций, кэша данных, TCM инструкций, TCM данных (опционально)

- Двухъядерный шаг блокировки (опционально)

- Защита интерфейса шины (опция)

- PMC-100 (программируемый контроллер MBIST, опционально)

- Расширение надежности, доступности и удобства обслуживания (RAS)

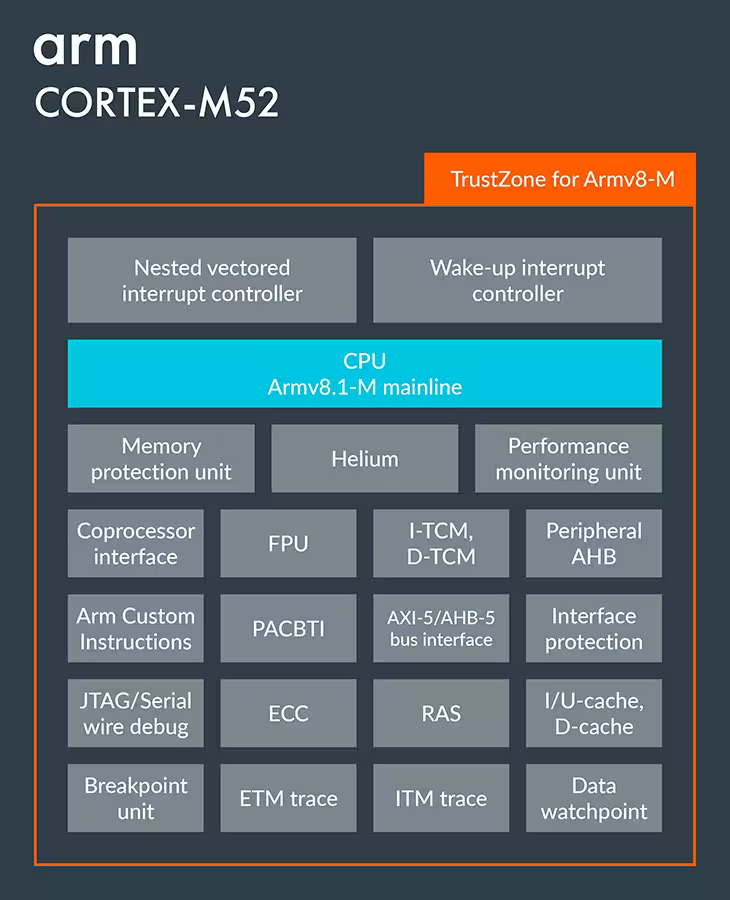

Структурная схема Cortex-M52 практически идентична блок-схеме Cortex-M55, за исключением того, что вместо блока DSP отображается блок PACBTI, строка “AXI-5 master” заменена на “AXI-5/AHB-5 bus interface”. Так что, похоже, различий не так уж много, но Arm предоставляет сравнительную таблицу для всех процессоров Arm Cortex-M, которую мы воспроизвели с ядрами Armv8 и Cortex-M7, чтобы лучше понять различия (пользователи смартфонов могут захотеть повернуть свой телефон в альбомном режиме, чтобы прочитать таблицу).

| Особенность | Cortex- M33 | Cortex- M35P | Cortex-M52 | Cortex-M55 | Cortex-M7 | Cortex-M85 |

|---|---|---|---|---|---|---|

| Архитектура набора команд | Armv8-M Mainline | Armv8-M Mainline | Armv8.1-M Mainline | Armv8.1-M Mainline | Armv7-M | Armv8.1-M Mainline |

| TrustZone для Armv8-M | Да (опция) | Да (опция) | Да (опция) | Да (опция) | Нет | Да |

| Helium (векторное расширение M-профиля) | Нет | Нет | Однотактный (опция) | Двойной ритм (опция) | Нет | Двойной ритм (опция) |

| Расширение PACBTI | Нет | Нет | Да (опция) | Нет | Нет | Да (опция) |

| Модуль с плавающей запятой (FPU) | СП (опция) | СП (опция) | HP, SP, DP (опция) | HP, SP, DP (опция) | СП, ДП (опция) | HP, SP, DP (опция) |

| Цифровая обработка сигналов (DSP) | Да (опция) | Да (опция) | Да | Да | Да | Да |

| Аппаратное разделение | Да | Да | Да | Да | Да | Да |

| Пользовательские инструкции Arm | Да (опция) | Нет | Да (опция) | Да (опция) | Нет | Да (опция) |

| Интерфейс сопроцессора | Да (опция) | Да (опция) | Да (опция) | Да (опция) | Нет | Да (опция) |

| DMIPS/МГц | 1,54 | 1,50 | 1,60 | 1,69 | 2.31 | 3.13 |

| CoreMark/МГц | 4.10 | 4.10 | 4.30 | 4.40 | 5.29 | 6.28 |

| Максимальное количество внешних прерываний | 480 | 480 | 480 | 480 | 240 | 480 |

| Области с максимальным MPU | 16 | 16 | 16 | 16 | 16 | 16 |

| Основная шина | AHB (32-разрядная версия) | AHB (32-разрядная версия) | AXI (32-разрядная версия) или AHB (32-разрядная версия). | AXI (64-разрядная версия) | AXI (64-разрядная версия) | AXI (64-разрядная версия) |

| Кэш инструкций | Нет | 2-16 КБ | 0–64 КБ | 0–64 КБ | 0–64 КБ | 0–64 КБ |

| Кэш данных | Нет | Нет | 0–64 КБ | 0–64 КБ | 0–64 КБ | 0–64 КБ |

| Инструкция ТСМ | Нет | Нет | 0-16 МБ | 0-16 МБ | 0-16 МБ | 0-16 МБ |

| Данные ТКМ | Нет | Нет | 0-16 МБ | 0-16 МБ | 0-16 МБ | 0-16 МБ |

| Конфигурация с двухъядерным шагом блокировки (DCLS) | Нет | Да | Да (опция) | Да (опция) | Да (опция) | Да (опция) |

Мы действительно можем увидеть еще несколько различий между Cortex-M52 и Cortex-M55: первый поддерживает однобитовый Helium против двухбитового Helium для последнего, а основная шина для новой части является 32-битной, а Cortex-M55 — M55 поддерживает 64-битную шину AXI. Это может объяснить, почему Arm утверждает, что Cortex-M52 обеспечивает упрощенный путь перехода от Cortex-M33 и Cortex-M4 для AIoT-приложений в автомобильном и промышленном управлении, профилактическом обслуживании и объединении носимых датчиков.

Cortex-M52 обеспечивает более высокую эффективность, меньшую занимаемую площадь и более низкую цену по сравнению с ядрами Cortex-M55 и Cortex-M85 за счет более низкой производительности. Но компания по-прежнему утверждает, что «разработчики могут получить выгоду от повышения производительности как ML, так и DSP: до 5,6-кратного повышения производительности для ML и до 2,7-кратного повышения производительности для цифровой обработки сигналов по сравнению с предыдущими поколениями Cortex-M», мы предполагаем, что это вышеупомянутые ядра Cortex-M33/Cortex-M4.

Arm Cortex-M52 заменит традиционные (очень) периферийные решения искусственного интеллекта, состоящие из CPU, DSP и NPU, для которых требуются три отдельные цепочки инструментов, компиляторы, отладчики и т. д., и позволит разработчикам писать с единым потоком разработки с помощью одной цепочки инструментов и другие инструменты разработки для традиционных рабочих нагрузок, DSP и ML. Он также остается полностью программно совместимым с ядрами Cortex-M55 и Cortex-M85. Поскольку до того, как настоящий чип станет доступен, может пройти некоторое время, Cortex-M52 вскоре будет доступен на виртуальном оборудовании Arm, что позволит заранее начать разработку программного обеспечения.

Прежде чем микроконтроллеры Arm Cortex-M52 появятся на рынке, может пройти некоторое время, и мы ожидаем, что анонсы начнутся в 2025 году. Более подробную информацию можно найти на странице продукта и в объявлении.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.