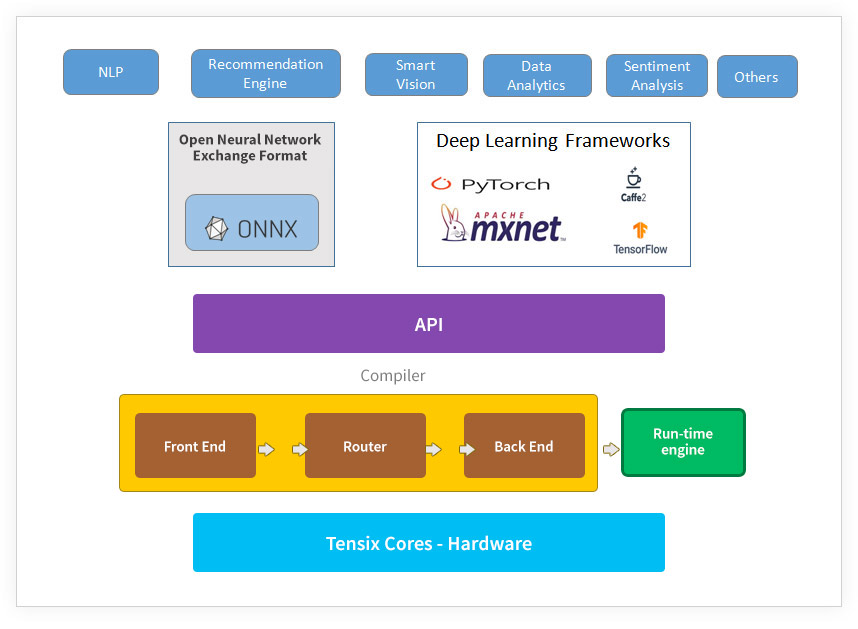

SiFive объявила, что стартап Tenstorrent, занимающийся микросхемой искусственного интеллекта, лицензирует новый 64-битный процессор SiFive Intelligence X280 для своих ядер Tensix, а Renesas будет использовать SiFive Intelligence для своих автомобильных процессоров.

Читать далее «Платформа SiFive Intelligence, используемая Tenstorrent и Renesas»Выпуск SiFive Core IP 21G1 улучшает обработку битов, модуль с плавающей запятой, уменьшает объем кода

Поскольку SiFive имеет ряд ядер с архитектурой RISC-V от маломощных E2-серии до высокопроизводительных U8-ядер с производительностью, аналогичной ядрам Cortex-A7x, компания какое-то время не выпускала новые ядра, а вместо этого сосредоточилась на улучшение их текущих ядер RISC-V.

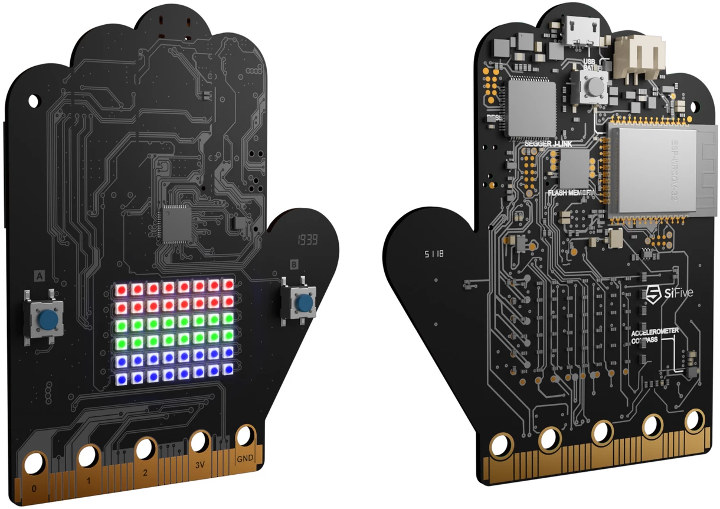

Читать далее «Выпуск SiFive Core IP 21G1 улучшает обработку битов, модуль с плавающей запятой, уменьшает объем кода»Комплект BBC Doctor Who “HiFive Inventor” предназначен для обучения детей программированию для IoT

BBC, Tynker и SiFive только что анонсировали комплект BBC Doctor Who “HiFive Inventor”, который включает в себя плату MCU с WiFi & Bluetooth и обучающие уроки для детей, которые научат их программировать для IoT проектов.

Плата HiFive Inventor основана на базе микроконтроллера SiFive FE310 RISC-V (тот же чип, что и на плате HiFive1) и модуле ESP32 Solo для подключения WiFi 4 и Bluetooth 4.x / 5.x. Как и плата BBC Micro:bit, HiFive Inventor предоставляет удобный для детей краевой (edge) разъем с вводом-выводом, светодиодной матрицей, датчиками и многим другим. Читать далее «Комплект BBC Doctor Who “HiFive Inventor” предназначен для обучения детей программированию для IoT»

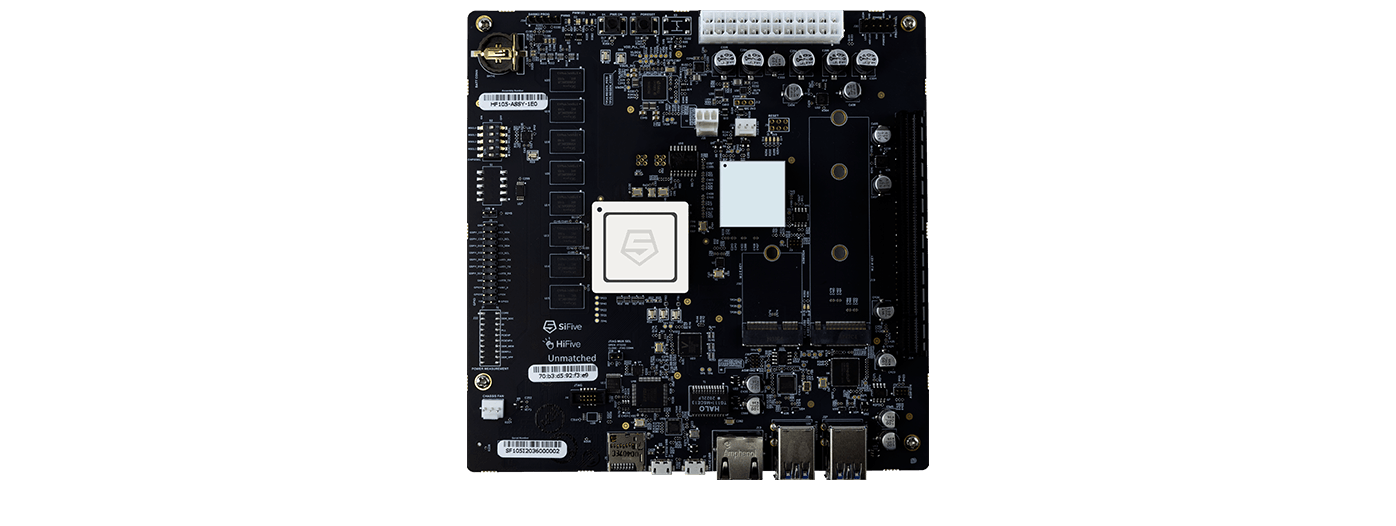

SiFive запускает материнскую плату HiFive Unmatched в форм-факторе mini-ITX для ПК с микроархитектурой RISC-V

Что касается SoC на основе RISC-V, SiFive всегда был эталоном в экосистеме RISC-V. 29 октября 2020 года SiFive подтвердила первый в истории ПК с архитектурой RISC-V.

Возросший спрос на микроархитектуру RISC-V, ориентированную на все приложения искусственного интеллекта, Интернет вещей, высокопроизводительные вычисления, привел к тому, что теперь представлен настольный ПК с микроархитектурой RISC-V. Материнская плата HiFive Unmatched mini-ITX с питанием от SiFive Freedom U740 поставляется с полной средой разработки, которая позволяет разработчикам создавать приложения на основе RISC-V, начиная с голого железа и заканчивая системами на базе Linux.

SiFive представит ПК для разработчиков с архитектурой RISC-V, на базе процессора нового поколения Freedom U740

В последние годы люди обсуждали необходимость иметь ПК или рабочие станции на базе Arm, чтобы разработчики могли работать непосредственно с целевым оборудованием, и теперь есть несколько вариантов, включая 24-ядерный ПК SynQuacer E-Series, 64-битную рабочую станцию Arm Ampere eMAG, и рабочая станция HoneyComb LX2K с 16 ядрами.

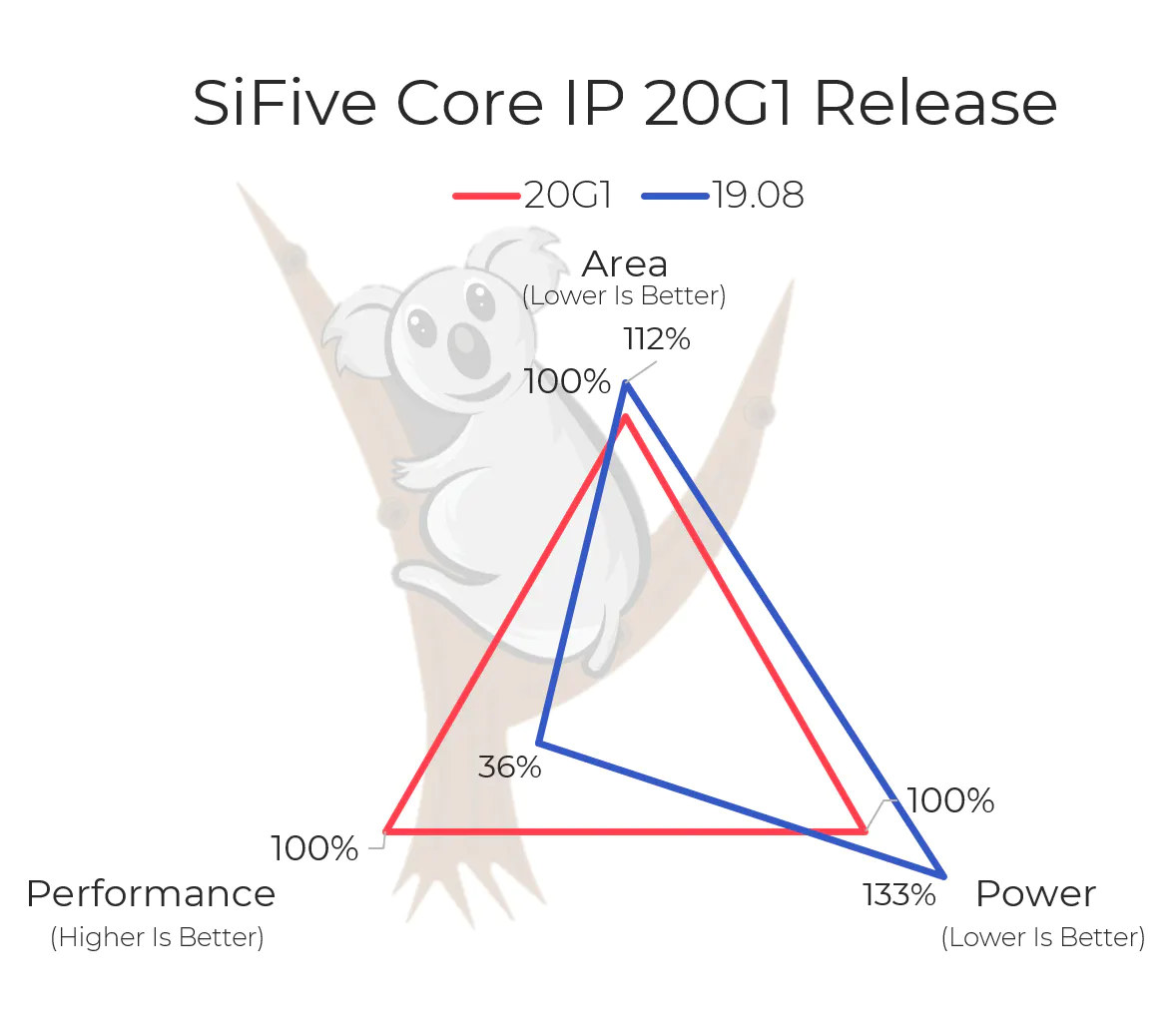

Читать далее «SiFive представит ПК для разработчиков с архитектурой RISC-V, на базе процессора нового поколения Freedom U740»SiFive выпускает ядро 20G1 на базе RISC-V , позволяющий повысить производительность и эффективность, при этом уменьшив занимаемую площадь

Ассортимент ядер SiFive RISC-V варьируется от 32-разрядных IoT-процессоров с низким энергопотреблением до более мощных 64-разрядных ядер RISC-V с поддержкой Linux, таких как новейшие ядра SiFive U84/U87, конкурирующие с ядрами Arm Cortex-A7x.

Выпуск SiFive Core IP 20G1 дополнительно расширяет существующие ядра компании RISC-V при этом повышая производительность, эффективности и уменьшая занимаемую площадь.

Читать далее «SiFive выпускает ядро 20G1 на базе RISC-V , позволяющий повысить производительность и эффективность, при этом уменьшив занимаемую площадь»SiFive Learn Inventor — это комплект для разработки беспроводных систем RISC-V, созданный на основе BBC Micro:bit

SiFive Learn Inventor — это RISC-V плата для обучения, частично созданная на основе платы BBC Micro:bit с удобным для подсоединения крокодилов (зажимов) edge разъемом и с светодиодной матрицей. Плата также полностью подходит для работы с операционной системой реального времени Amazon FreeRTOS.

Сделанная в форме руки плата оснащена процессором SiFive FE310 RISC-V, который можно встретить на плате SiFive HiFive1, а также на WiFi + Bluetooth модуле ESP-WROOM-32. Читать далее «SiFive Learn Inventor — это комплект для разработки беспроводных систем RISC-V, созданный на основе BBC Micro:bit»

IP-ядро SiFive U8-Series Out-of-Order RISC-V составит конкуренцию ядру Arm Cortex-A72

Ранее на этой неделе мы писали об открытой платформе безопасности SiFive Shield, которая является эквивалентом технологии безопасности Arm TrustZone. Но, на этой неделе у компании было еще одно важное объявление — выпуск IP-ядра SiFive U8-Series Out-of-Order (OoO) RISC-V со значительно более высокой производительностью, чем ядро компании U7-серии, ставшее конкурентом ядру Arm Cortex A72.

Читать далее «IP-ядро SiFive U8-Series Out-of-Order RISC-V составит конкуренцию ядру Arm Cortex-A72»