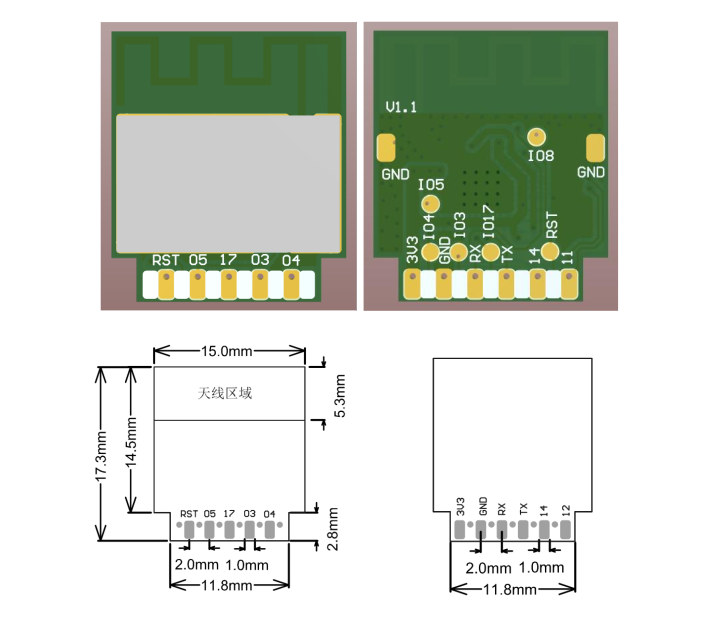

Постепенно появляется все больше оборудования на базе процессора ESP32-C3 RISC-V , а LILYGO T-32C3 – это компактный модуль на базе процессора WiFi и Bluetooth LE, который включает в себя 4-мегабайтную флеш-память и антенну на печатной плате.

Мы полагаем, что T-32C3 можно будет встретить в умных часах и платах для разработки компании, и он присоединится к другим модулям ESP32-C3 от AI Thinker.

Читать далее «LILYGO T-32C3 — небольшой модуль ESP32-C3 WiFi и BLE IoT с 4 МБ флэш-памяти»