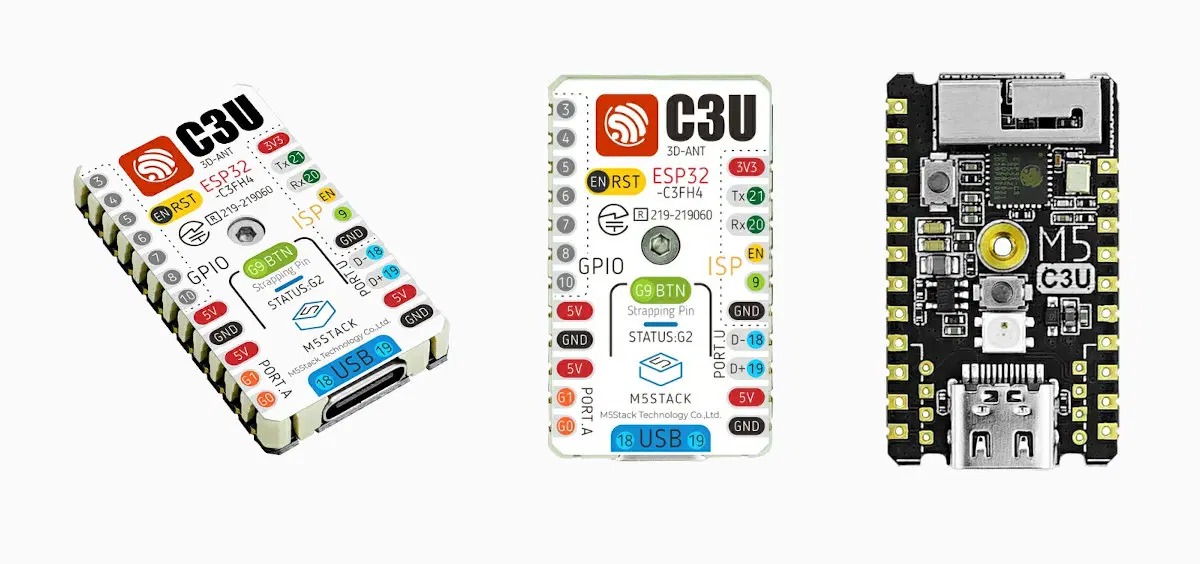

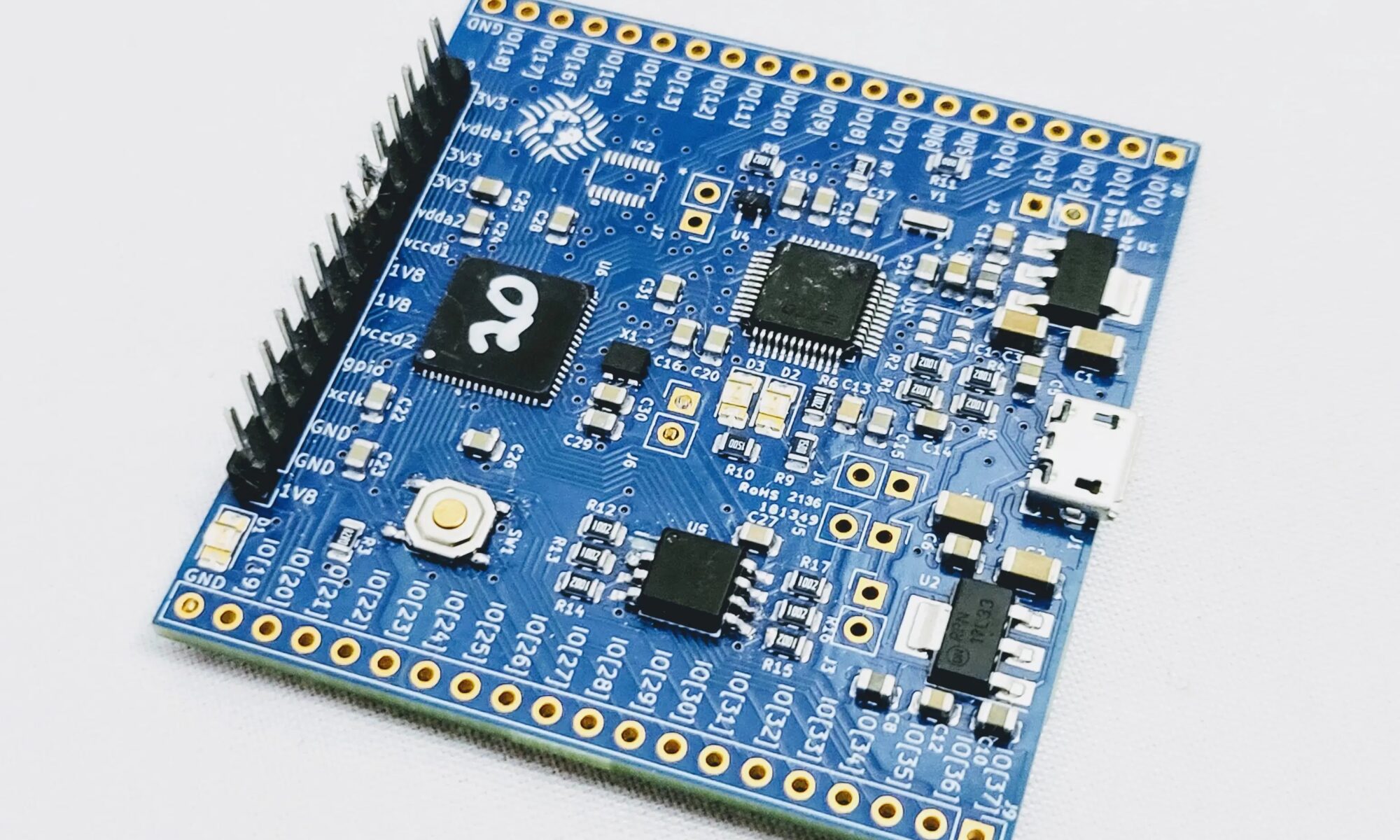

M5Stamp C3U — это обновленная версия RISC-V IoT модуля M5Stamp C3 с термостойкой крышкой, поддержкой WiFi 4 и Bluetooth 5.0, в котором был убран чип CH9102 USB -TTL, а вместо этого используется внутренний USB-интерфейс процессора ESP32-C3 для программирования и получения дополнительного вывода GPIO.

Хотя некоторые процессоры ESP32 поставляются со встроенным интерфейсом USB, многие платы по-прежнему используют внешний чип USB-TTL, такой как CH340 или CP2102, для работы с последовательным интерфейсом, который используется для отладки и прошивки, вероятно, из-за ограничений при использовании ESP32-C3 ( последовательный USB / JTAG), но компания M5Stack, вероятно, посчитала их работоспособными, а небольшое снижение затрат выгодной. Читать далее «IoT модуль M5Stamp C3U использует собственный USB-интерфейс ESP32-C3 для программирования и отладки»