Компания Achronix Semiconductor недавно объявила об общедоступной Speedster7t AC7t1500 FPGA, предназначенной для приложений ускорения сетей, хранения и вычислений (AI/ML).

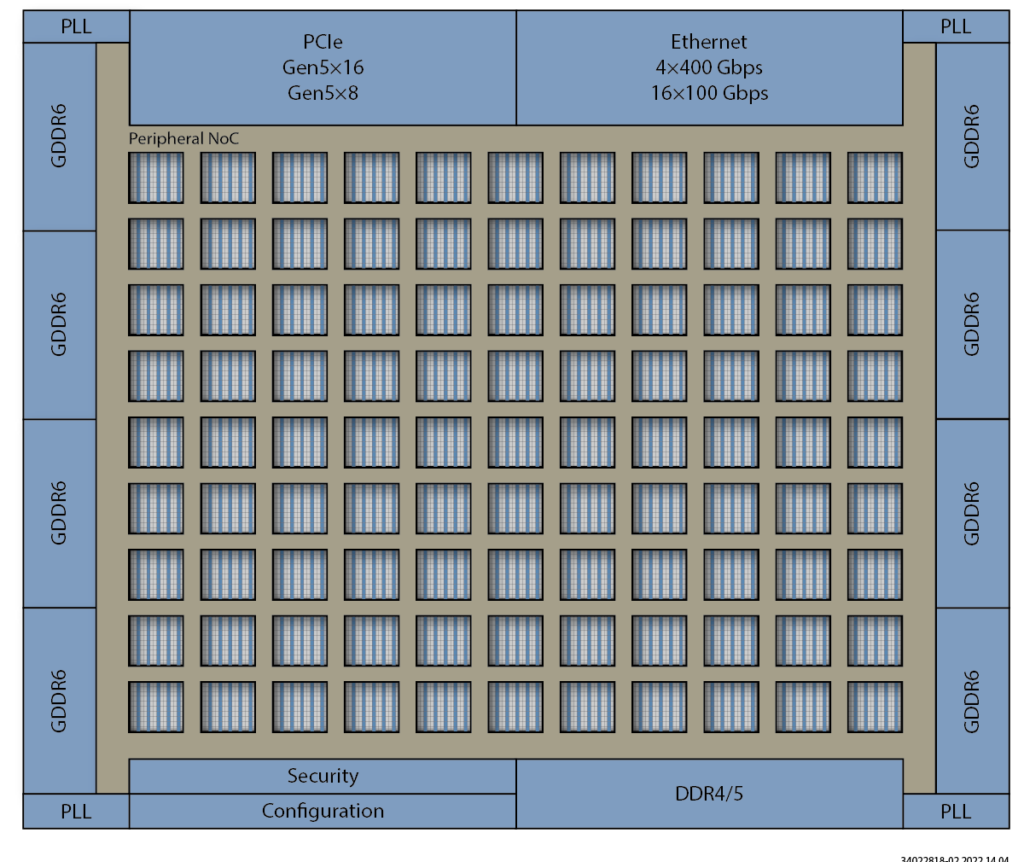

Семейство 7-нм Speedster7t FPGA предлагает порты PCIe Gen5 и интерфейсы памяти GDRR6 и DDR5/DDR4, обеспечивает скорость до 400 Гбит/с на портах Ethernet и включает в себя 2D-сеть на кристалле (2D NoC), которая может обрабатывать 20 Тбит/с общей пропускной способности.

Особенности Achronix Speedster7t:

- Двумерная сеть на кристалле (2D NoC), обеспечивающая передачу данных с высокой пропускной способностью через матрицу FPGA и между контроллерами и интерфейсами жесткого ввода-вывода и памяти.

- Блоки MLP (процессоры машинного обучения) с массивами множителей, деревом сумм, аккумуляторов и поддержкой как операций с фиксированной, так и с плавающей запятой, включая прямую поддержку формата Tensorflow bfloat16 и блочного формата с плавающей запятой (BFP).

- Несколько портов PCIe Gen5

- Высокоскоростные приемопередатчики SerDes, поддерживающие модуляцию 112 Гбит/с PAM4 и 56 Гбит/с PAM4/NRZ, а также более низкие скорости передачи данных

- Жесткие MAC-адреса Ethernet, поддерживающие скорость до 400 Гбит/с

- Контроллеры и интерфейсы GDDR6 и DDR5 SDRAM (Примечание: Speedster7t AC7t1500 поддерживает DDR4, а не DDR5)

- Безопасность

- Двунаправленный криптографический движок на базе коммутационной сети (Speedster7t AC7t1550)

- Двунаправленный криптографический движок (Speedster7t AC7t800 и другие)

- Логическая архитектура с 6-входными LUT (6LUT), 8-разрядными ALU, триггерами и режимом переформулированного умножения LUT (MLUT), основанным на модифицированном алгоритме Бута, который удваивает производительность умножения на основе LUT.

- Маршрутизация коммутационной сети улучшена за счет маршрутизации выделенной шины и активного мультиплексирования шины.

- Блоки памяти 72 КБ BRAM и 2 КБ LRAM

- GPIO, поддерживающий несколько стандартов ввода/вывода

- PLL и DLL для поддержки нескольких встроенных деревьев часов

- Несколько типов программных интерфейсов

- Частичная реконфигурация фабрики FPGA

- Удаленное обновление матрицы FPGA

- Функции безопасности для шифрования и аутентификации битовых потоков

- Поддержка отладки через Achronix Snapshot

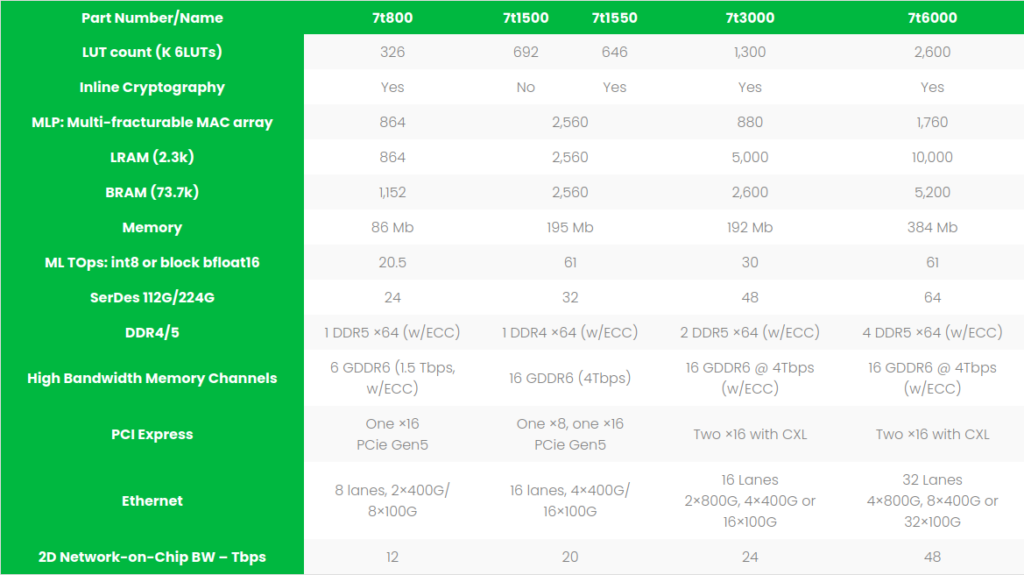

В матрице продуктов Speedster7t есть пять частей: 7t1500 с 692 000 LUT сейчас находится в массовом производстве, а 7t800 начального уровня с 326 LUT на днях был добавлен в Achronix Tool Suite. Детали более высокого класса 7t3000 и 7t6000 должны быть запланированы на будущее, поскольку они еще не указаны в техническом описании.

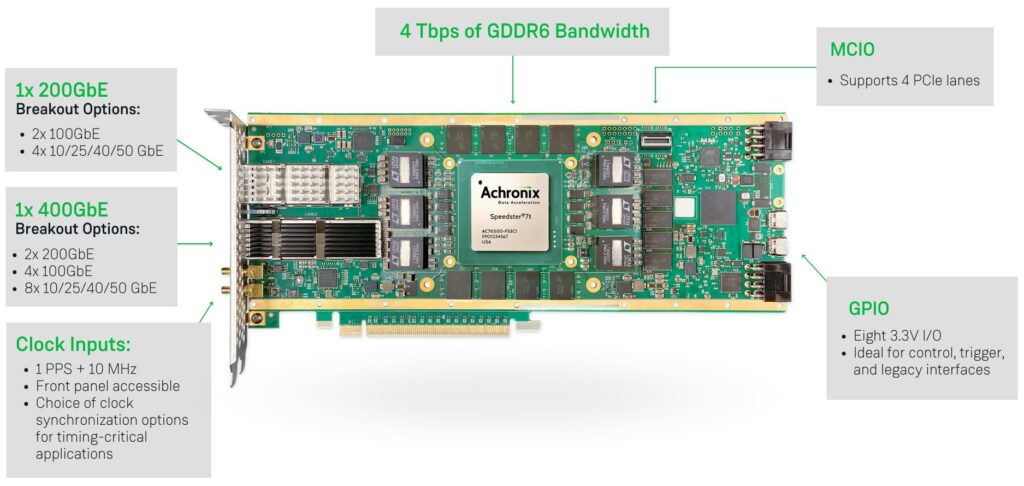

Нам не удалось найти типичную отладочную плату для Speedster7t FPGA, но компания предоставляет ускорительную плату VectorPath S7t-VG6 на базе 7t1500 FPGA. Он предназначен для разработки высокопроизводительных вычислений и функций ускорения для приложений искусственного интеллекта (ИИ), машинного обучения (МО), сетей и центров обработки данных.

Основные интерфейсы и характеристики:

- FPGA — Speedster7t AC7t1500 FPGA

- Системная память

- GDDR6 — 16 ГБ, 8 банков с двумя независимыми 16-битными каналами на банк

- Один блок памяти DDR4 — 2666 МГц с ECC, до 4 ГБ (×72)

- Хранилище — флэш-память для загрузки FPGA

- Сертификация PCI SIG для поддержки хост-интерфейса PCIe Gen4 x16

- 1х модуль QSFP-DD — 1x 400GbE, 2x 200GbE, 4x 100GbE или 8x 10/25/40/50 GbE

- 1х модуль QSFP56 — 1x 200GbE, 2x 100GbE или 4x 10/25/40/50 GbE

- 8x GPIO

- MCIO — подключен к FPGA через четыре трансивера, поддерживающих скорость передачи данных до PCIe Gen5.

Achronix Tool Suite используется для всех FPGA Achronix и IP-решений eFPGA и поставляется с инструментами проектирования ACE и Synopsys Synplify-Pro для синтеза проектов FPGA. Библиотеки моделирования Achronix поддерживаются Mentor Graphics ModelSim, Synopsys VCS и Aldec Riviera-PRO, а пакет также включает инструмент отладки проектирования в реальном времени Snapshot Debugger. Процесс проектирования должен быть простым для разработчиков FPGA, привыкших работать с конкурирующими FPGA с поддержкой входных данных VHDL и Verilog, а также моделированием в соответствии с отраслевыми стандартами.

Дополнительную информацию можно найти на странице продукта и в пресс-релизе.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.