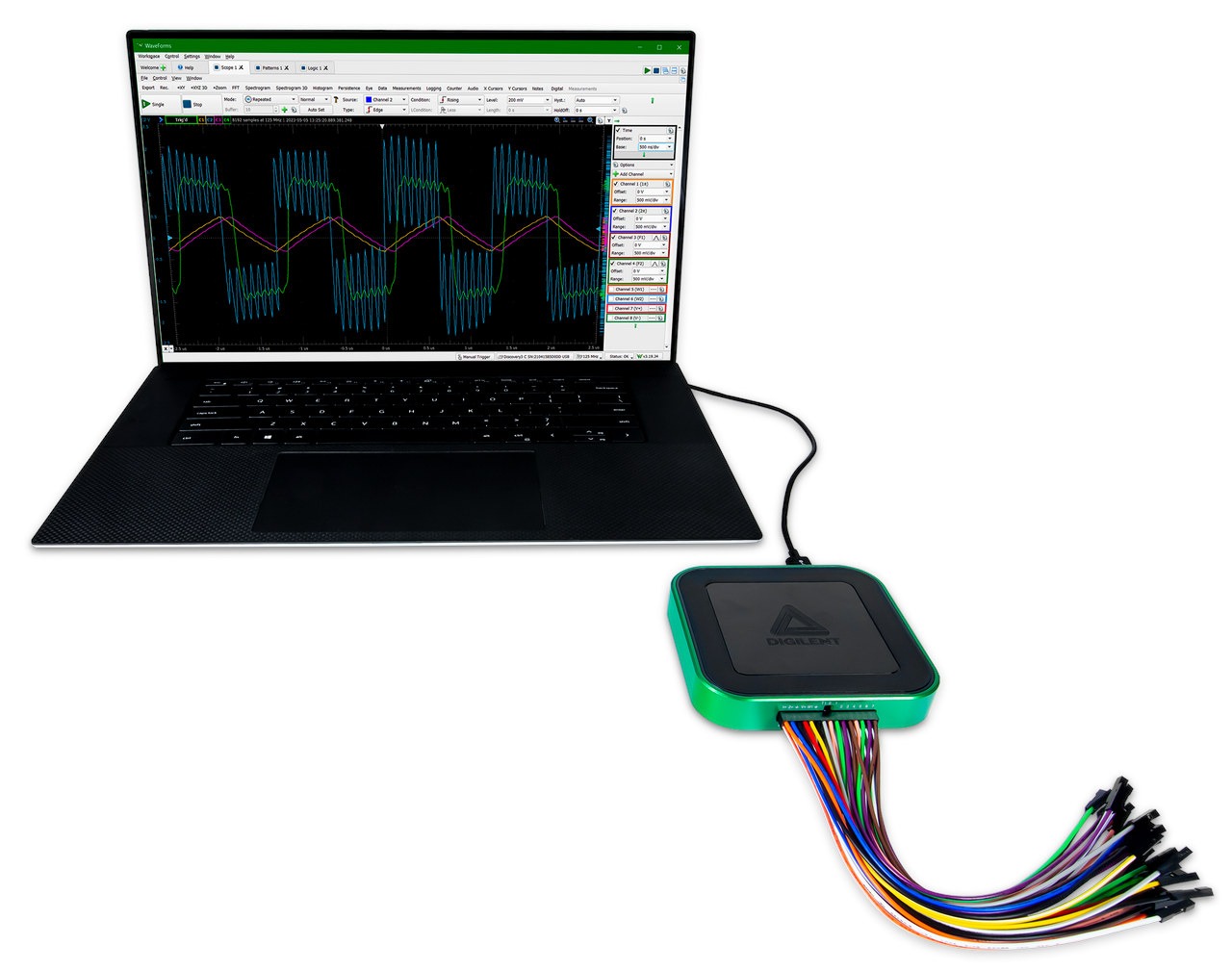

Digilent Analog Discovery 3 — это USB-осциллограф с частотой дискретизации до 125 Мвыб/с, который также можно использовать в качестве генератора сигналов, логического анализатора и/или регулируемого источника питания до 5 В.

Также, благодаря его программному обеспечению, доступны другие функции — осциллограф USB-C также может выступать в качестве анализатора спектра, анализатора сети, анализатора импеданса, анализатора протокола, регистратора данных, вольтметра и поддерживает сценарии в приложении.

Читать далее «Analog Discovery 3 — USB-осциллограф со скоростью 125 Мвыб/с, генератор сигналов, логический анализатор и регулируемый источник питания.»