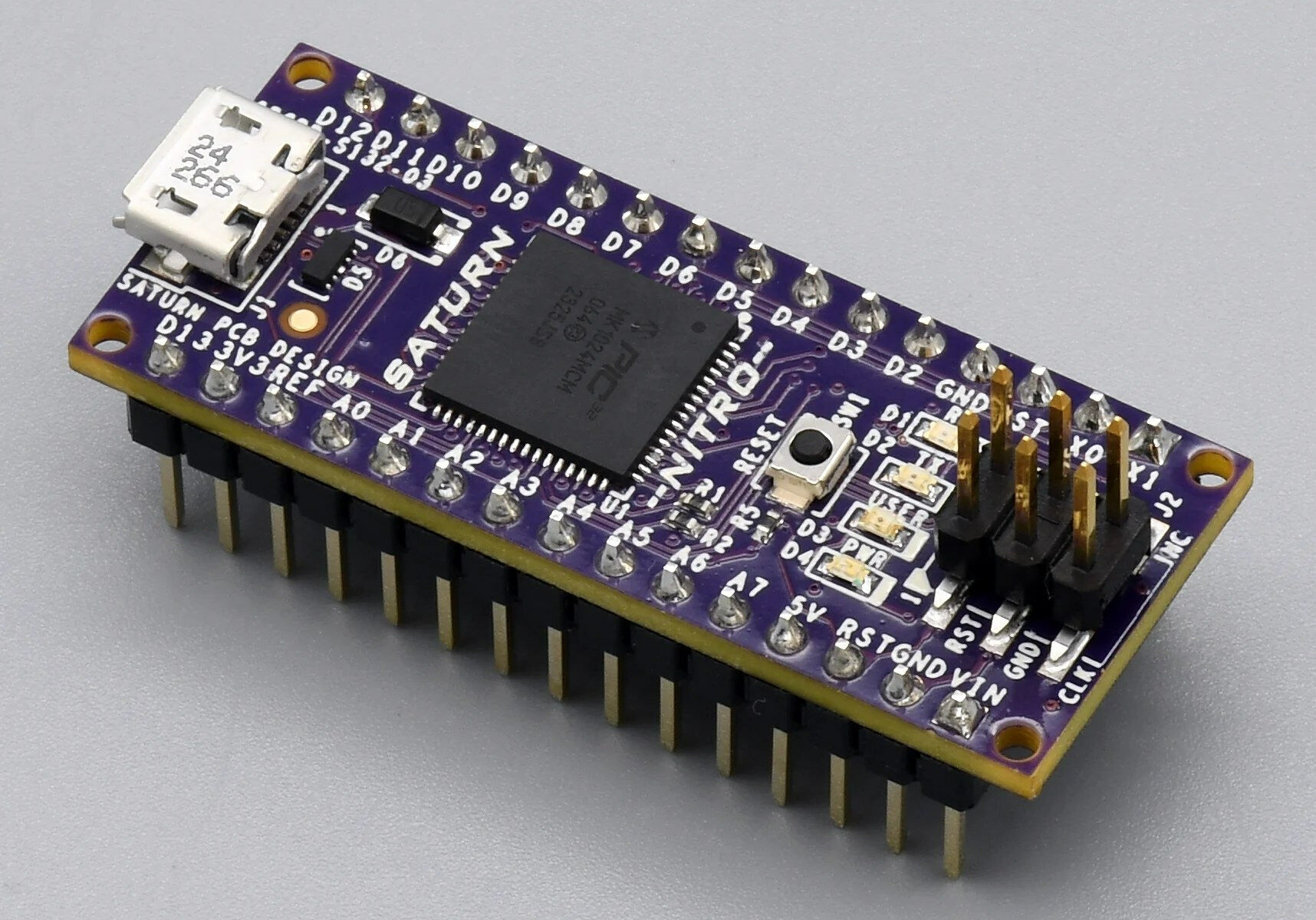

Хотя Microchip регулярно выпускает микроконтроллеры PIC32 и оценочные комплекты, мы не видели большого количества плат разработки PIC32 от сторонних производителей. SATURN NITRO является исключением, а плата разработки, вдохновленная Arduino Nano, оснащена 120 МГц PIC32MK общего назначения и управления двигателем 32-битным MIPS-микроконтроллером с 256 КБ SRAM, 1024 КБ флэш-памяти и 4 КБ EEPROM.

Читать далее «SATURN NITRO – плата разработки Microchip PIC32MK с форм-фактором Arduino Nano»Выпуск Linux 6.14 – Основные изменения, архитектуры Arm, RISC-V и MIPS

Линус Торвальдс только что объявил о выпуске Linux 6.14 на LKML:

Раннее утро понедельника (ну, раннее для меня, я не жаворонок), и хотелось бы найти хорошее оправдание, почему релиз 6.14 не состоялся вчера по обычному воскресному расписанию.

Читать далее «Выпуск Linux 6.14 – Основные изменения, архитектуры Arm, RISC-V и MIPS»

Шлюз HaLowLink 1 Wi-Fi HaLow превращает устаревшие устройства в клиентов Wi-Fi HaLow через Ethernet, USB или Wi-Fi 2,4 ГГц

Morse Micro в сотрудничестве с GL.iNet недавно продемонстрировала шлюз HaLowLink 1 Wi-Fi HaLow , который компания называет эталонной платформой проектирования и оценки Wi-Fi HaLow, разработанной для беспроводного подключения на большие расстояния с низким энергопотреблением для IoT-приложений. Созданный на основе модуля AzureWave AW-HM593 с кремнием Morse Micro MM6108, он поддерживает полосы пропускания 1/2/4/8 МГц.

Выпуск Linux 6.13 – Основные изменения в архитектурах Arm, RISC-V и MIPS

Линус Торвальдс объявил о выпуске Linux 6.13 в списке рассылки Linux Kernel Mailing List :

На прошлой неделе не произошло ничего ужасного или неожиданного, поэтому я пометил и выпустил финальную версию 6.13.

Читать далее «Выпуск Linux 6.13 – Основные изменения в архитектурах Arm, RISC-V и MIPS»

MIPS P8700 — 64-битный процессор RISC-V с внеочередным выполнением операций, предназначенный для автомобильных приложений

В 2022 году компания MIPS впервые представила IP-ядра серии MIPS P8700 и многопроцессорные IP-ядра I8500, а теперь компания объявила о широкой доступности 64-разрядного RISC-V ядра P8700. Многопроцессорная система MIPS P8700 (MPS), созданная для работы с передовыми системами помощи водителю (ADAS), ML и автомобильными приложениями на основе программного обеспечения, масштабируется до 64 разнородных кластеров вышедших из строя многопоточных многоядерных процессоров MIPS.

Читать далее «MIPS P8700 — 64-битный процессор RISC-V с внеочередным выполнением операций, предназначенный для автомобильных приложений»Промышленный модуль IoT Quectel BG770A-SN обеспечивает спутниковую связь 5G, NB-IoT и NTN

Недавно Quectel выпустила промышленный IoT-модуль BG770A-SN, который поставляется в сверхкомпактном форм-факторе и поддерживает как NTN, так и TN, а также оснащен GNSS для позиционирования. Этот готовый к 5G модуль также поддерживает iSIM и использует спутниковую группировку GEO для покрытия по всему миру. Кроме того, модуль предлагает интегрированные элементы безопасности (ISE) и может работать в промышленном диапазоне температур от -40°C до +85°C.

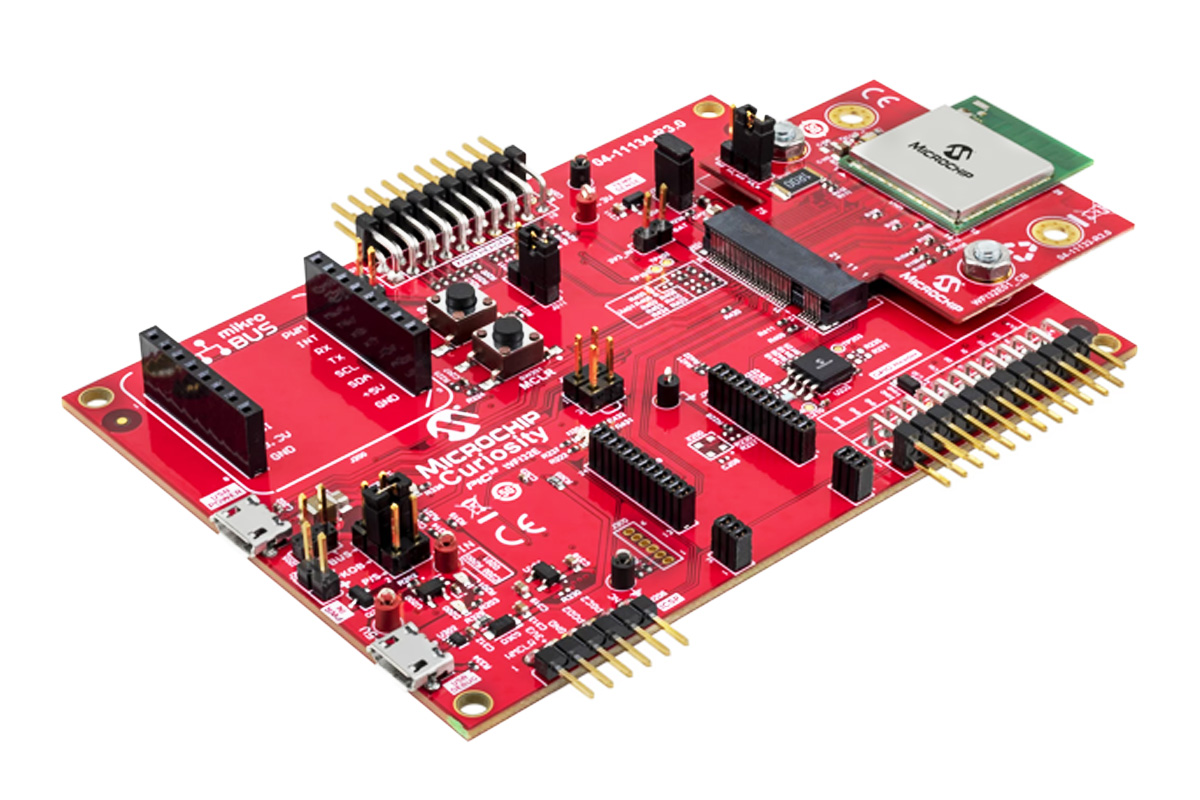

Читать далее «Промышленный модуль IoT Quectel BG770A-SN обеспечивает спутниковую связь 5G, NB-IoT и NTN»Microchip PIC32MZ-W1 — это 32-битный MIPS WiFi-микроконтроллер с более чем 60 GPIO, USB, CAN Bus, Ethernet и другими интерфейсами.

Недавно Microchip выпустила беспроводной микроконтроллер PIC32MZ-W1 вместе с 20 другими компонентами WiFi, включая WiFi-микроконтроллеры, контроллеры связи, сетевые контроллеры и модули plug-and-play. Среди них беспроводной микроконтроллер PIC32MZ-W1 является самым интересным из-за его 32-битного ядра MIPS microAptiv M-class, работающего на частоте до 200 МГц, расширенных функций аппаратной безопасности и интегрированной платформы Microchip Trust для безопасной облачной аутентификации.

Читать далее «Microchip PIC32MZ-W1 — это 32-битный MIPS WiFi-микроконтроллер с более чем 60 GPIO, USB, CAN Bus, Ethernet и другими интерфейсами.»Выпуск Linux 6.11 – Основные изменения, архитектуры Arm, RISC-V и MIPS

Выпущена версия Linux 6.11, о чем сообщил Линус Торвальдс в рассылке разработчиков ядра Linux (LKML):

«В настоящее время я снова в поездке вне своего обычного часового пояса, но здесь, в Вене, воскресный день, и версия 6.11 выпущена.

Читать далее «Выпуск Linux 6.11 – Основные изменения, архитектуры Arm, RISC-V и MIPS»