В 2022 году компания MIPS впервые представила IP-ядра серии MIPS P8700 и многопроцессорные IP-ядра I8500, а теперь компания объявила о широкой доступности 64-разрядного RISC-V ядра P8700. Многопроцессорная система MIPS P8700 (MPS), созданная для работы с передовыми системами помощи водителю (ADAS), ML и автомобильными приложениями на основе программного обеспечения, масштабируется до 64 разнородных кластеров вышедших из строя многопоточных многоядерных процессоров MIPS.

Архитектура RISC-V процессора RISC-V серии P8700

P8700 — первый RISC-V IP от MIPS. Он реализует архитектуру набора инструкций RISC-V RV64GCZba_Zbb. Это позволяет MPS выполнять атомарные операции, операции с плавающей запятой одинарной и двойной точности и включает в себя расширения для манипулирования битами, которые упрощают задачи обработки данных. Эта возможность использования сжатых инструкций с помощью расширения RISC-V C (RVC) обеспечивает многопоточность при сбоях в работе.

Нестандартная многопоточность и гетерогенная кластеризация серии P8700

Многопоточность с нарушением порядка выполнения просто означает, что MPS обрабатывает несколько инструкций одновременно, не соблюдая порядок. Таким образом, MPS может обрабатывать даже взаимозависимые инструкции одновременно, группировать результаты и быстрее выдавать желаемый результат, сокращая время ожидания. MIPS утверждает, что P8700 обеспечивает прирост производительности до 60% по сравнению с последовательным выполнением. В то же время, 8-ступенчатая выборка команд, 7-ступенчатая выдача и 4-ступенчатый конвейер декодирования обеспечивают высокую пропускную способность.

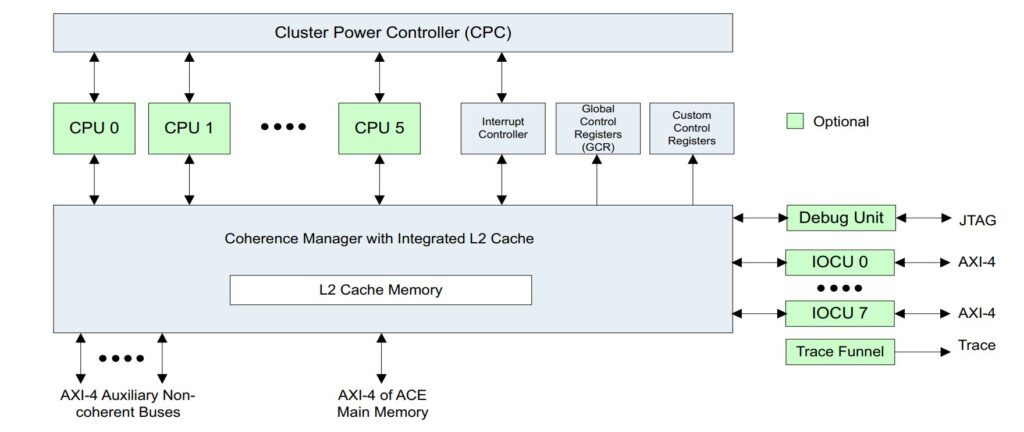

Многопроцессорная система P8700 (MPS) использует высокомасштабируемую и настраиваемую кластерную архитектуру, что делает ее подходящей для различных приложений с высокой интенсивностью вычислений. В каждом кластере может размещаться до шести процессорных ядер RISC-V и восемь блоков когерентности ввода-вывода (Icu), при этом общее количество агентов в кластере не должно превышать восьми. Coherence Manager (CM) обеспечивает согласованность кэширования с использованием протокола на основе каталогов, управляя кэшированием как уровня 1 (L1), так и уровня 2 (L2), причем размер последнего составляет до 8 МБ. Архитектура поддерживает до 64 кластеров, масштабируясь до 512 ядер и 2048 аппаратных потоков (harts). Гибкость еще больше повышается за счет независимых доменов синхронизации, позволяющих настраивать производительность и энергоэффективность ядер, CM и интерфейсов ввода-вывода. Кроме того, контроллер питания кластера (CPC) обеспечивает динамическое управление питанием, позволяя регулировать энергопотребление на уровне ядра и регулировать тактовую частоту для оптимизации энергопотребления.

Отличительной чертой P8700 MPS является возможность конфигурирования с возможностью изменения количества ядер, размеров кэш-памяти, фокуса и конфигурации памяти в соответствии с конкретными потребностями приложений. Кэши L1 и L2 настраиваются и поддерживают эффективное управление памятью с помощью таких функций, как защита ECC и передача данных из кэша в кэш. Система поддерживает как согласованные, так и несогласованные настройки, с интерфейсами AXI4 и ACE для конфигураций с одним и несколькими кластерами, соответственно. Возможности отладки, включая PDTrace и гибридные режимы отладки, упрощают разработку и устранение неполадок. Благодаря такой надежной архитектуре P8700 MPS хорошо подходит для применения в автомобилестроении, машинном обучении, создании сетей и высокопроизводительных встраиваемых системах.

MIPS P8700 будет представлен в системах-на-кристалле MobileEye

MIPS P8700 будет интегрирован в системы-на-кристалле (SoC) Mobileye, разработанные для платформ автономного вождения. Mobileye включила процессоры MIPS в несколько поколений EyeQ, от EyeQ2 до EyeQ6H и EyeQ6L, а теперь и в свою платформу EyeQ следующего поколения. Сюда также входят ожидаемый Mobileye EyeQ7 и некоторые предыдущие поколения. О партнерстве было объявлено еще в 2022 году .

Характеристики MIPS P8700

- Архитектура набора инструкций : RISC-V RV64GCZba_Zbb

- Привилегированные режимы : Супервизор, Машина, Отладка

- Ядер на кластер : до 6

- Потоки на ядро : 1 или 2

- Масштабируемость : до 64 кластеров, 512 ядер, 2048 потоков

- Конвейер : 8-широкая выборка, 4-широкая декодирование, 7-широкая выдача

- Кэш инструкций L1 : 32 КБ или 64 КБ

- Кэш данных L1 : 32 КБ или 64 КБ

- Кэш L2 : от 256 КБ до 8 МБ

- Размеры страниц MMU : до 512 ГБ

- IOCU на кластер : до 8

- Внутренние пути данных : 512 бит

- Поддержка отладки : EJTAG, трассировка RISC-V

- Управление питанием : управление питанием на уровне ядра и кластера

- Функциональная безопасность : соответствует ASIL-B(D)

- Интерфейс системной шины : AMBA ACE, AXI-4

В MIPS P8700 MPS встроены функции обеспечения функциональной безопасности и конфигурирования. Устройство совместимо со стандартом ASIL-B (D) для промышленного и автомобильного применения и включает контроль четности и исправление ошибок SRAM.

MIPS P8700 MPS IP теперь доступен для более широкого рынка, и поставки с OEM-запусками начнутся в ближайшее время. На веб-сайте MIPS есть больше полезной информации, включая техническое описание и руководство программиста.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.