Компания Arm представила новое ядро класса микроконтроллеров с ядром Cortex-M85, которое обеспечивает более высокую целочисленную производительность, чем Cortex-M7, и более высокую производительность машинного обучения по сравнению с Cortex-M55, оснащенным инструкциями Helium.

Новое ядро Cortex-M85 предназначено для разработчиков, которым требуется повышенная производительность для своих продуктов на базе Cortex-M без перехода на ядра Cortex-A, а вместо этого с сохранением важных функций, таких как детерминизм, короткие задержки прерывания и расширенные режимы управления с низким энергопотреблением во всех ядрах Cortex-M.

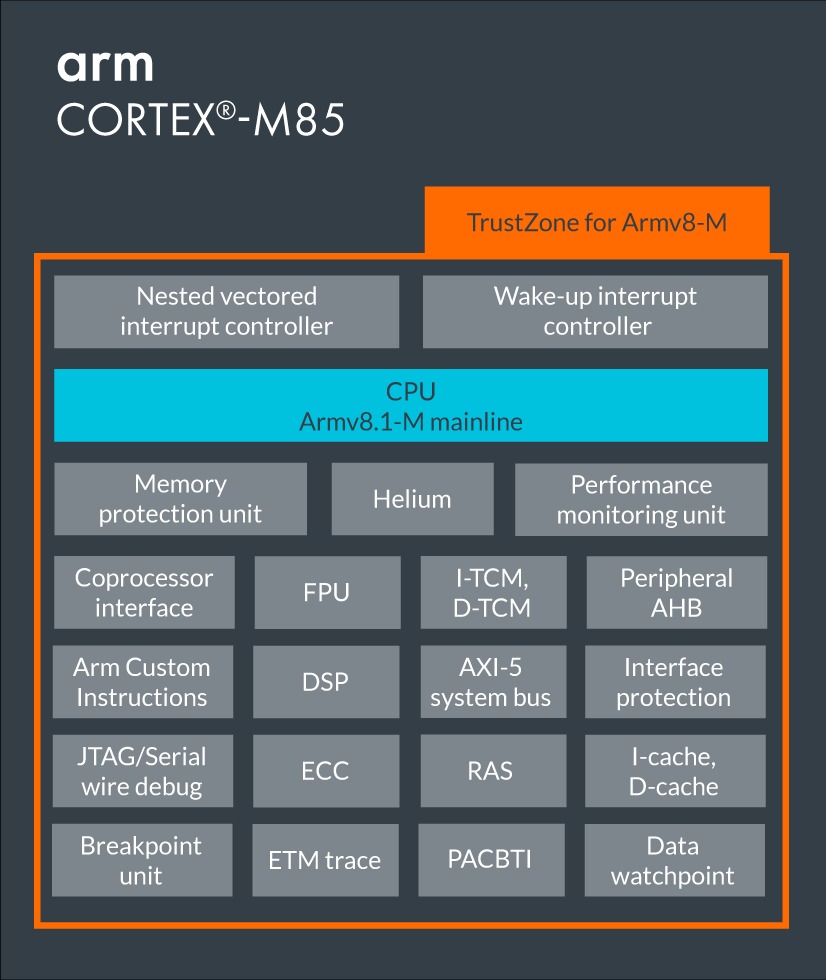

Основные характеристики и спецификации Arm Cortex-M85:

- Архитектура — Армв8.1-М

- Производительность — 6,28 CoreMark/МГц и 3,13/4,52/8,76DMIPS/МГц (1. «основные правила» в документации Dhrystone, 2. встраивание функций, 3. одновременная («многофайловая») компиляция).

- Интерфейсы шины

- AMBA 5 AXI 64-бит основная системная шина (совместима с IP-адресами AXI4)

- AMBA 5 AHB 32-битная периферийная шина

- AMBA 5 AHB 64-битная шина доступа TCM (подчиненный порт)

- Конвейер — 7-этапный (для основного целочисленного конвейера)

- Безопасность

- Технология Arm TrustZone

- Расширение PACBTI (аутентификация указателя, идентификация цели филиала) помогает достичь уровня безопасности 2, сертифицированного PSA .

- Защита памяти — дополнительные блоки защиты памяти (MPU) для изоляции процессов с 16 областями MPU и фоновой областью — если реализована TrustZone, могут быть безопасные и незащищенные MPU.

- Расширение DSP — 32-битное расширение DSP/SIMD

- Расширение вектора

- Опциональная технология Helium (векторное расширение М-профиля), поддерживающая до: 2 x 32-битных MAC-адресов/цикл

- 4 x 16-битных MAC/цикл

- 8 x 8-битных MAC-адресов/цикл

- Модуль с плавающей запятой (FPU) — дополнительный FPU с поддержкой операций с плавающей запятой половинной точности (fp16), одинарной точности (fp32) и двойной точности (fp64).

- Поддержка ускорителей — дополнительный интерфейс сопроцессора (64-разрядный), поддерживающий до 8 сопроцессоров для пользовательских ускорителей вычислений. Дополнительные пользовательские инструкции для рук.

- Кэш инструкций — до 64 КБ с ECC (опционально)

- Кэш данных — до 64 КБ с ECC (опционально)

- Инструкции TCM (ITCM) — до 16 МБ с ECC (опционально)

- Данные TCM (DTCM) — до 16 МБ с ECC (опционально)

- прерывания

- Встроенный вложенный векторный контроллер прерываний (NVIC), поддерживающий до 480 прерываний и немаскируемых прерываний (NMI). Количество уровней приоритета настраивается от 8 до 256.

- Контроллер прерывания пробуждения (WIC)

- Внутренний и/или внешний (дополнительно) WIC для пробуждения процессора после блокировки питания или при остановке всех часов.

- Поддержка низкого энергопотребления

- Архитектурно определенные режимы сна и глубокого сна.

- Встроенные инструкции ожидания события (WFE) и ожидания прерывания (WFI) с функцией перехода в спящий режим при выходе

- Сигналы индикации сна и глубокого сна

- Несколько доменов питания с дополнительной поддержкой хранения памяти и логики

- Отлаживать

- Аппаратные и программные точки останова

- Блок контроля производительности (PMU)

- Трассировка — необязательная трассировка инструкций со встроенной трассировкой макроячейки (ETM), трассировкой данных (DWT) (выборочная трассировка данных) и трассировкой инструментальных средств (ITM) (программная трассировка)

- Надежность

- ECC в кэше инструкций, кэше данных, TCM инструкций, TCM данных (опционально)

- Двухъядерный LOCK STEP (опционально, доступно к концу 2022 г.)

- Защита интерфейса шины (опционально, доступно к концу 2022 г.)

- PMC-100 (программируемый контроллер MBIST, опционально, доступно к концу 2022 г.)

- Расширение надежности, доступности и удобства обслуживания (RAS)

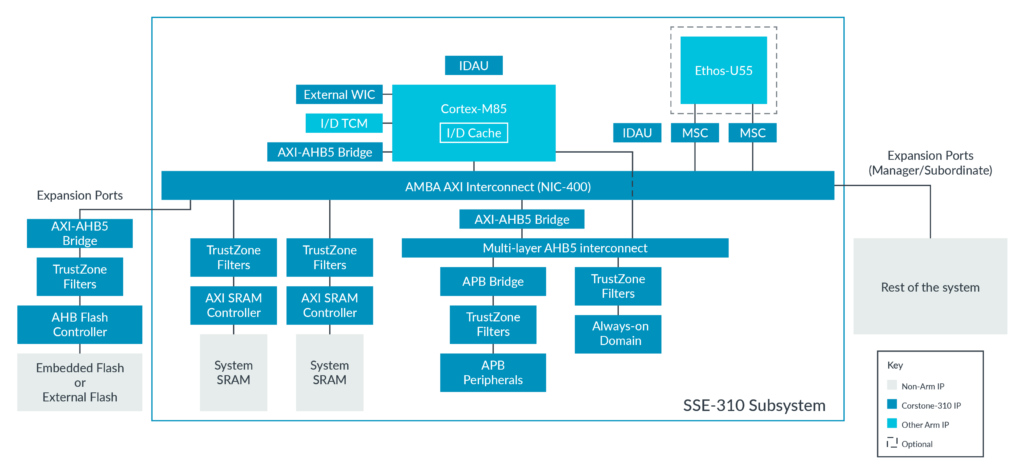

- Эталонный пакет — Corstone-310 с Cortex-M85 и Ethos-U55 uNPU

Разработчики могут начать с эталонной платформы подсистемы Arm Corstone-310 (SSE-310), объединяющей Cortex-M85 и uNPU Ethos-U55, а также другие элементы для создания микроконтроллера с SRAM, Trustzone, комплектом управления питанием (PCK-600), безопасный компонент отладки (SDC-600), защищенные системные IP-компоненты SIE-200. Разработчики программного обеспечения также могут подготовить свой код для нового ядра с помощью Arm Virtual Hardware (AVH) с моделями процессоров, систем и плат разработки на базе Arm, включая Corstone-310, для создания прототипов, разработки и развертывания.

Микроконтроллер на базе Cortex-M85 будет поставляться с более крупными встроенными SRAM, более высокими тактовыми частотами (вероятно, это означает, что мы увидим больше микроконтроллеров с тактовой частотой 1 ГГц и выше, помимо NXP i.MX RT1170), и будет реализован в узлах меньшей геометрии, а Arm предоставит Cortex-M85. PIK (комплект для реализации процессора) с литейным процессом TSMC 22ULL, который включает в себя руководство пользователя, схемы shmoo, планы этажей и эталонные сценарии реализации в одном пакете.

Представители компании Arm не сказали когда ожидается выпуск микроконтроллеров Cortex-M85, но возможна задержка в один или два года после того, как ядро Arm будет объявлено. Подробнее можно узнать в анонсе и на странице разработчика.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.