Компания Efinix анонсировала три программно-определяемых SoC на базе архитектуры RISC-V, основанных на ядре Charles Papon VexRiscv и оптимизированных для FPGA компании от Trion T8 до T120.

VexRiscv представляет собой 32-разрядный процессор на базе архитектуры RISC-V, использующий RISCV32I ISA с расширениями M и C, имеет пять этапов конвейера (выборка, декодирование, выполнение, память и обратная запись) и настраиваемый набор функций. Каждый SoC включает в себя ядро RISC-V, память, а также различные устройства ввода-вывода и интерфейсы.

Основные характеристики для каждого из трех RISC-V SoC:

- Ruby SoC

- FPGA – ~12K LEs / 78 блоков оперативной памяти

- Производительность – 50 МГц (1.16 DMIPS/МГц)

- Оперативная память-4 КБ встроенной оперативной памяти, до 3,5 ГБ DDR DRAM

- Периферийные устройства – 16х портов GPIO, таймер, PLIC, 3х SPI ведущих, 3x I2C ведущих/ведомых, 2х порта UART

- 1x AXI4, 2x APB3 периферийное устройство пользователя

- Сферы применения — система управления в реальном времени и обработка сигналов изображения.

- Jade SoC

- FPGA – ~ 7K LEs / 93 блока оперативной памяти

- Производительность — 50 МГц (1,2 DMIPS / МГц)

- Память — 32 КБ встроенной памяти

- Периферийные устройства – 16x GPIO, таймер, PLIC, 2x SPI ведущих, 2x I2C ведущих/ведомых, 1x UAR

- 1x APB3 периферийное устройство пользователя

- Сферы применения — управление и контроль, промышленная автоматизация или регистрация данных

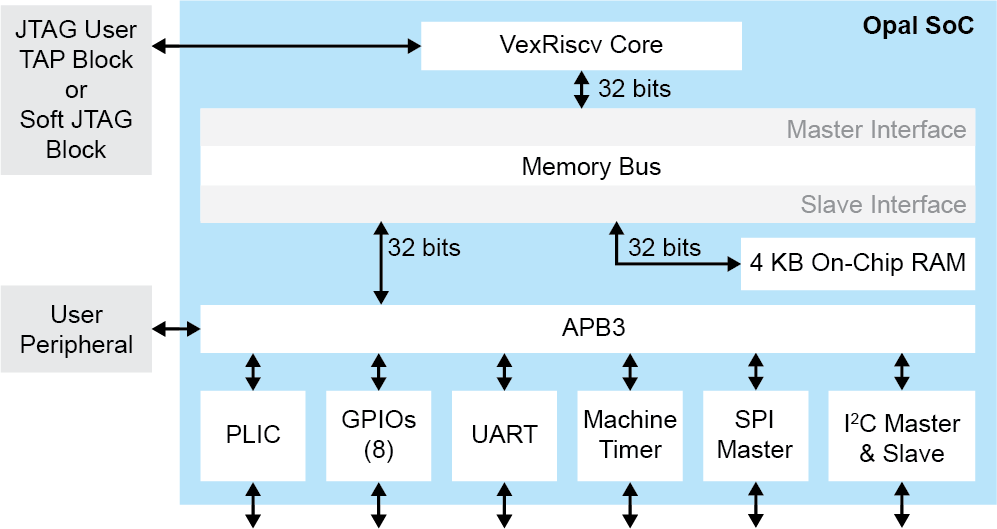

- Opal SoC

- FPGA – ~ 5K LE / 16 блоков оперативной памяти

- Производительность — 50 МГц / 20 МГц (0,98 DMIPS / МГц)

- Память — 4 КБ встроенной памяти

- Периферийные устройства — 8x GPIO, таймер, PLIC, 1x SPI ведущих, 1x I2C ведущих/ведомых, 1x UART

- 1x APB3 периферийное устройство пользователя

- Сферы применения — мониторинг системы или удаленная настройка и контроль.

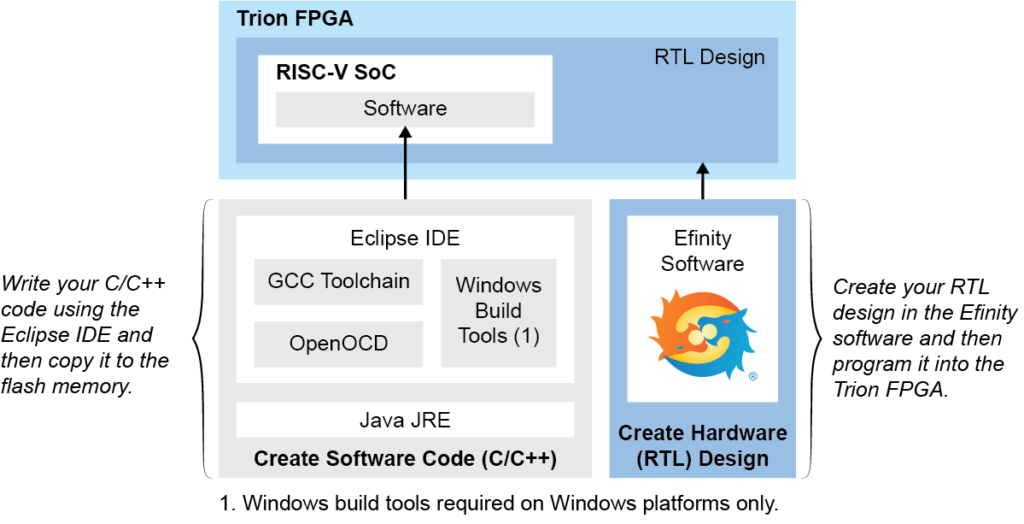

Для каждого SoC компания предоставляет RTL-файлы SoC, пакет поддержки платы (BSP), пример кода и SDK на основе Eclipse IDE, GCC toolchain и отладчика OpenOCD.

Программное обеспечение Efinity также позволит вам создавать собственные RTL-проекты на основе Ruby, Jade или Opal RISC-V SoC для одной из плат разработки Efinix Trion.

Вы найдете дополнительную информацию и ссылки для загрузки файлов RISC-V SoC (требуется бесплатная регистрация по электронной почте) на странице продукта.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.