На следующей неделе состоится FOSDEM 2020, и будет несколько интересных бесед о разработке аппаратного и программного обеспечения с открытым исходным кодом . Один из докладов называется «Open ESP — гетерогенная платформа с открытым исходным кодом для разработки систем RISC-V», вот выдержки из него:

ESP — это исследовательская платформа с открытым исходным кодом для систем на кристалле RISC-V, которая объединяет множество аппаратных ускорителей.

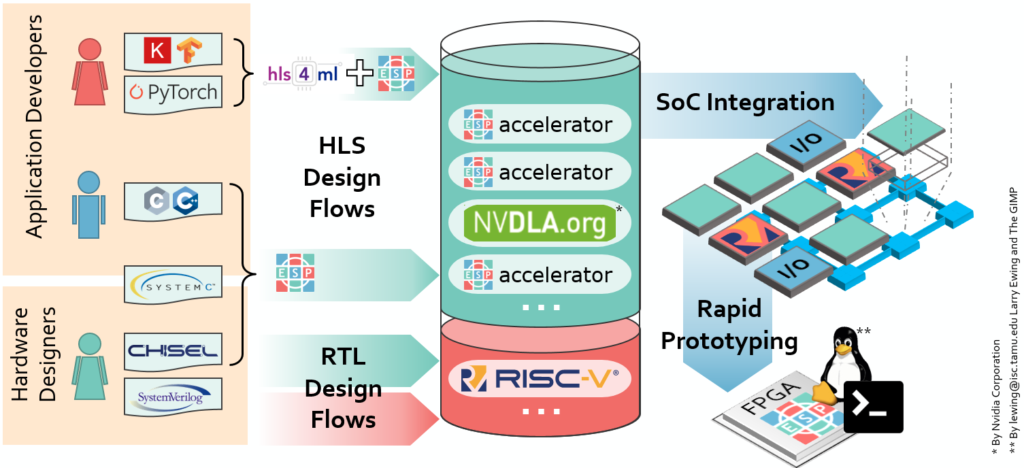

ESP обеспечивает вертикально интегрированный процесс проектирования от разработки программного обеспечения и аппаратной интеграции до полного системного прототипирования на FPGA. Для разработчиков приложений она предлагает автоматизированные решения для конкретной области, позволяющие синтезировать новые ускорители для их программного обеспечения и отобразить их в гетерогенной архитектуре SoC. Для инженеров по аппаратному обеспечению она предлагает автоматизированные решения для интеграции своих конструкций ускорителей в полный SoC.

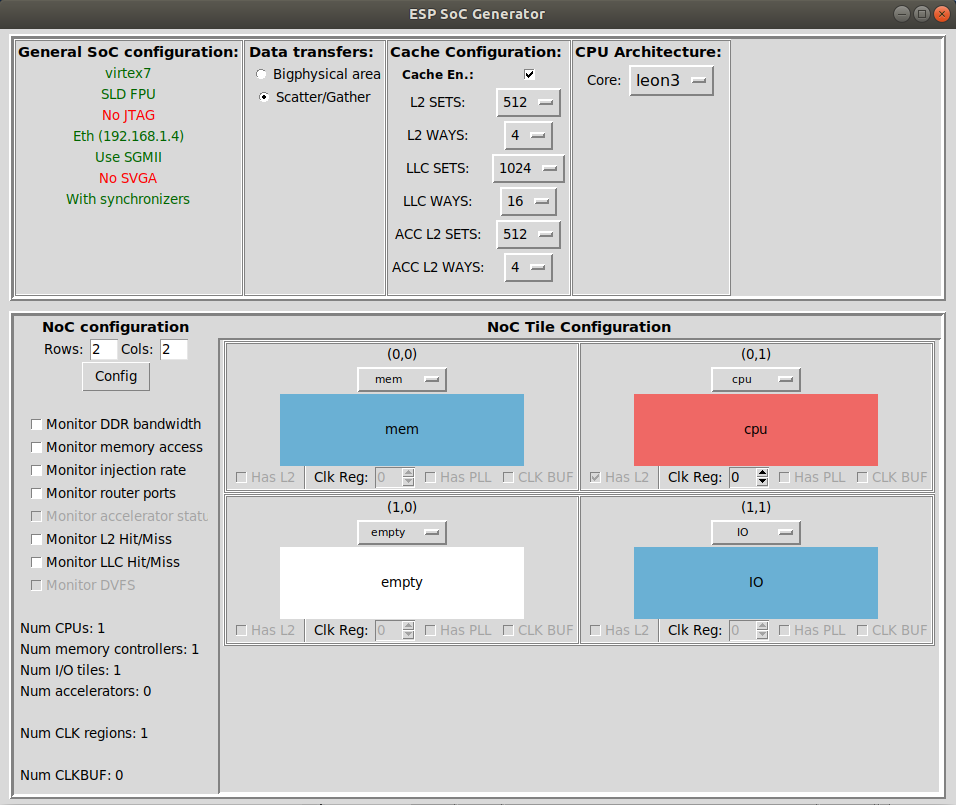

Если мы перейдем на официальный сайт, то увидим, что ESP (Embedded Scalable Platform) фактически поддерживает как 32-битные ядра Leon3 (Sparc) и 64-битные Ariane (RISC-V), так и различные аппаратные ускорители от платформы или сторонних производителей.

Особенности:

- Архитектура

- Архитектура на основе тайла: тайлы процессора, памяти и ускорителя

- NoC (Network-on-Chip)

- Поддерживает 32-битные ядра Leon3 (Sparc) или 64-битные Ariane (RISC-V)

- Ускорители

- ESP ускорители

- Cadence Stratus HLS

- Xilinx Vivado HLS

- Chisel

- Сторонние ускорители — ускоритель глубинного обучения NVIDIA (NVDLA)

- ESP ускорители

- Дизайн

ESP совместима с платами разработки FPGA, такими как Xilinx Virtex UltraScale + FPGA VCU118, Xilinx Virtex-7 FPGA VC707 или proFPGA quad Virtex7, которая, в свою очередь, может работать под управлением Linux SMP на ядрах RISC-V или Sparc.

Изначально ESP был разработан для работы на CentOS 7 и до сих пор является рекомендуемой ОС, но недавно была добавлена поддержка Ubuntu 18.04. Обязательные компоненты включают в себя различные пакеты из ОС (Python, Perl, Qt и т. д.), коммерческие инструменты от Cadence, Xilinx и / или Mentors Graphics, а также наборы инструментов RISC-V и / или Sparc.

Вы можете следовать инструкциям по установке ESP в Centos или Ubuntu и создать свой первый одноядерный или многоядерный SoC с пользовательским интерфейсом ESP SoC Generator, как описано в документации.

Запланировано больше уроков, специально ориентированных на дизайн ускорителей. Если вам нужен более подробный обзор Embedded Scalable Platform, вы можете посмотреть это 16-минутное видео, опубликованное несколько недель назад.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.