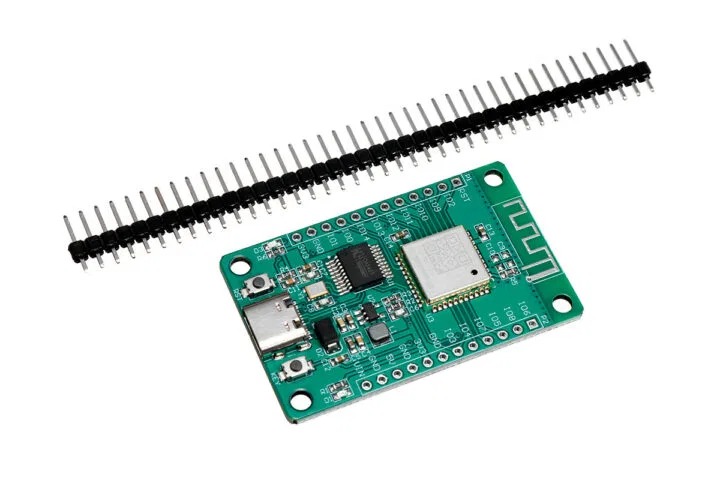

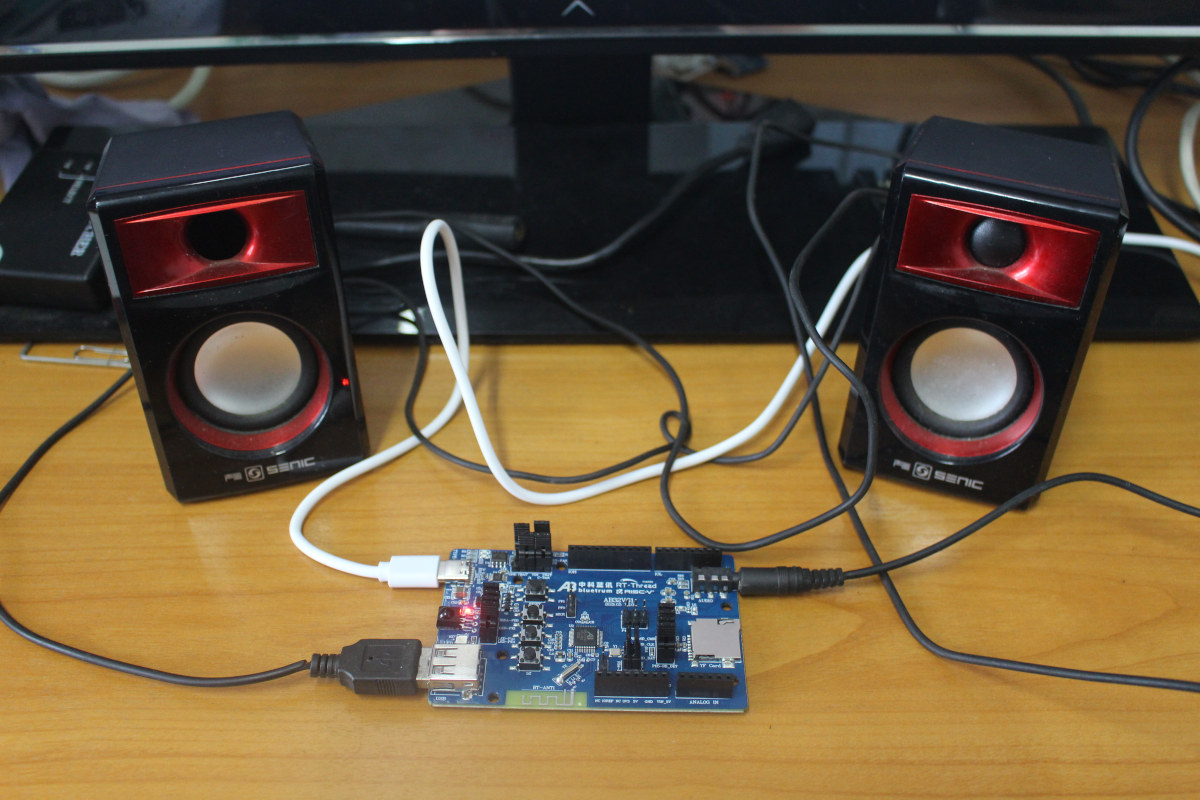

В прошлом году была рассмотрена плата для разработки HiSpark WiFi IoT на базе Hisilicon Hi3861 с поддержкой LiteOS и HarmonyOS, которая была доступна в Китае по цене чуть менее $10 или как часть комплекта для разработки с базовой платой и модулями примерно за $60.

Плату можно было купить на Taobao, но теперь в продаже на Banggood появилось то, что кажется новой версией платой для разработки HarmonyOS на базе Hi3861V100 в более широком форм-факторе на за $10.99. Читать далее «Плата для разработки HarmonyOS появилась в продаже менее чем за $11»