SkiffOS — кросс-компилируемая система minimal Linux для встраиваемых контейнеров, на днях добавила поддержку одноплатного компьютера Sipeed Nezha RISC-V, и началась работа над меньшей по размеру платой Sipeed Lichee RV.

Читать далее «SkiffOS — дистрибутив minimal Linux для встраиваемых контейнеров, теперь поддерживает плату Sipeed Nezha RISC-V»MangoPi MQ Pro — альтернатива Raspberry Pi Zero W за 20 долларов

MangoPi MQ Pro — это Allwinner D1 RISC-V SBC, который предлагает альтернативу Raspberry Pi Zero W с тем же форм-фактором и большинством тех же функций, включая подключение по Wi-Fi и Bluetooth.

Читать далее «MangoPi MQ Pro — альтернатива Raspberry Pi Zero W за 20 долларов»Плата Bee Motion Mini сочетает в себе ESP32-C3 с датчиком PIR

Крошечный Bee Motion Mini, разработанный Smart Bee Designs, сочетает в себе беспроводную ESP32-C3 RISC-V SoC с датчиком PIR для создания отчетов об обнаружении движения через WiFi, Bluetooth LE или Bluetooh Mesh.

Читать далее «Плата Bee Motion Mini сочетает в себе ESP32-C3 с датчиком PIR»Ai-Thinker TG-12F — более дешевая и стабильная альтернатива модулям ESP32

Ai-Thinker TG-12F — самый экономичный IoT модуль WiFi и Bluetooth на рынке. Это платформа на базе RISC-V, которая поставляется с общедоступным SDK с открытым исходным кодом.

Большинство существующих клиентов Ai-Thinker уже должны быть знакомы с модулями серии ESP32 и платами для разработки компании. В новом модуле TG-12F добавлена поддержка конфигурации сети с помощью Bluetooth, преимущества нулевой конфигурации или сети SoftAP, а также он быстрее и стабильнее, чем модули ESP32. Читать далее «Ai-Thinker TG-12F — более дешевая и стабильная альтернатива модулям ESP32»

Комплект для разработки Dongshan Nezha STU включает в себя SBC / SoM на базе Allwinner D1 RISC-V

Dongshan Nezha STU — это комплект для разработки, состоящий из системы-на-модуле (SoM) на базе Allwinner D1 и несущей платы с тремя 40-контактными разъемами для доступа к вводам-выводам процессора RISC-V.

Хотя модуль “Dongshan Nezha STU Core” не такой компактный, как модуль Sipeed LicheeRV, его также можно использовать в качестве автономного одноплатного компьютера (SBC) с портами USB-C, Ethernet и HDMI, а также разъемом для микро SD-карты для прошивки и он чем-то похож на Khadas Edge. Читать далее «Комплект для разработки Dongshan Nezha STU включает в себя SBC / SoM на базе Allwinner D1 RISC-V»

Модульный Linux-терминал DevTerm получает модуль RISC-V, совместимый с Raspberry Pi CM3

Модульный портативный компьютер DevTerm на базе операционной системы Linux в ретро стиле, получил 64-битный модуль RISC-V на базе SoC Allwinner D1 1 ГГц и предлагает альтернативу существующим модулям на базе Arm, таким как Raspberry Pi CM3, или альтернативы на базе процессоров Allwinner H6 или Rockchip RK3399.

Читать далее «Модульный Linux-терминал DevTerm получает модуль RISC-V, совместимый с Raspberry Pi CM3»Renesas представляет семейство 64-битных микропроцессоров RISC-V RZ / Five с поддержкой Linux

Компания Renesas представила свое первое семейство процессоров RISC-V с микропроцессорами общего назначения RZ / Five на базе 64-битного ядра процессора RISC-V Andes AX45MP, и с долгосрочной поддержкой Linux через CIP Linux промышленного класса, позволяющее поддерживать встроенные системы на базе Linux более 10 лет.

Процессор RISC-V совместим по выводам с семейством процессоров RZ / G2UL на базе Arm Cortex-A55 / M33, и, несмотря на то, что это семейство общего назначения, чипы RZ / Five особенно хорошо подходят для конечных IoT устройств, таких как шлюзы для инверторов для солнечных панелей или систем домашней безопасности. Читать далее «Renesas представляет семейство 64-битных микропроцессоров RISC-V RZ / Five с поддержкой Linux»

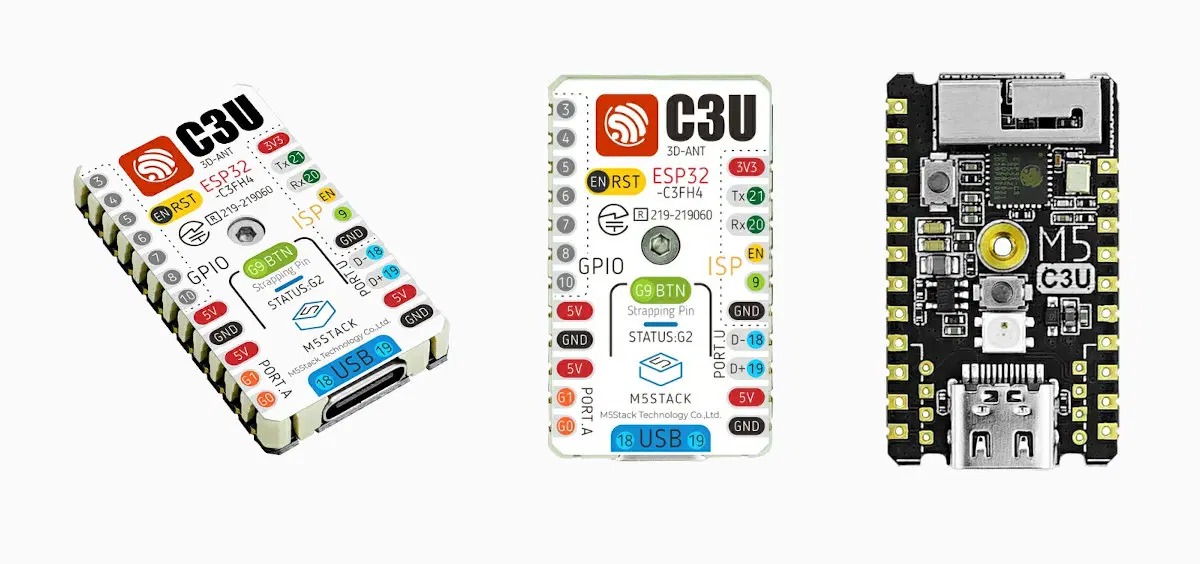

IoT модуль M5Stamp C3U использует собственный USB-интерфейс ESP32-C3 для программирования и отладки

M5Stamp C3U — это обновленная версия RISC-V IoT модуля M5Stamp C3 с термостойкой крышкой, поддержкой WiFi 4 и Bluetooth 5.0, в котором был убран чип CH9102 USB -TTL, а вместо этого используется внутренний USB-интерфейс процессора ESP32-C3 для программирования и получения дополнительного вывода GPIO.

Хотя некоторые процессоры ESP32 поставляются со встроенным интерфейсом USB, многие платы по-прежнему используют внешний чип USB-TTL, такой как CH340 или CP2102, для работы с последовательным интерфейсом, который используется для отладки и прошивки, вероятно, из-за ограничений при использовании ESP32-C3 ( последовательный USB / JTAG), но компания M5Stack, вероятно, посчитала их работоспособными, а небольшое снижение затрат выгодной. Читать далее «IoT модуль M5Stamp C3U использует собственный USB-интерфейс ESP32-C3 для программирования и отладки»