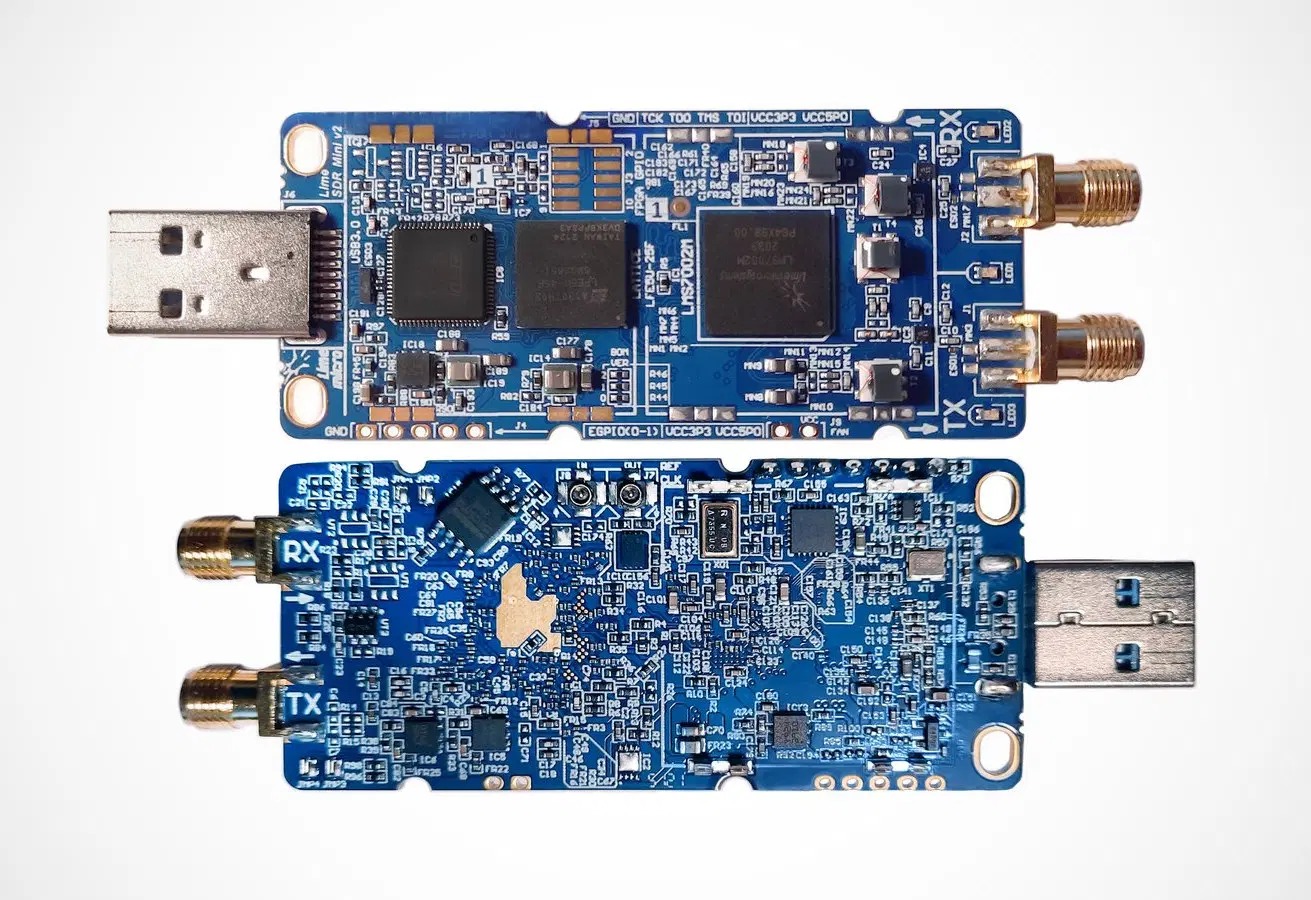

LimeSDR Mini — это аппаратная полнодуплексная плата USB SDR с открытым исходным кодом, основанная на Intel Altera Max 10 Altera FGPA, которая была представлена в 2017 году на Crowd Supply и собрала около 2 миллионов долларов США. С тех пор он использовался в различных проектах, включая передатчики цифрового телевидения.

Читать далее «Плата LimeSDR Mini 2.0 USB SDR получает обновление до Lattice Semi ECP5 FPGA (краудфандинг)»ZUBoard 1CG — недорогая плата для разработки AMD Xilinx Zynq UltraScale+ ZU1CG MPSoC FPGA

Avnet ZUBoard 1CG — это плата для разработки с новым двухъядерным процессором AMD Xilinx Zynq UltraScale+ ZU1CG начального уровня Cortex-A53 MPSoC с 81 000 системных логических ячеек FPGA, оснащенная 1 ГБ оперативной памяти LPDDR4, а также разъемами SYZYGY и расширением mikroBus для плат Click.

Плата стоимостью 159 долларов может предложить хорошую возможность начать работу с Zynq UltraScale+ MPSoC, поскольку она намного дешевле, чем платы на базе устройств ZU3, таких как Ultra96-V2 или MYD-CZU3EG. Avnet говорит, что плата подходит для приложений искусственного интеллекта, машинного обучения, встроенного зрения, встроенной обработки и робототехники.

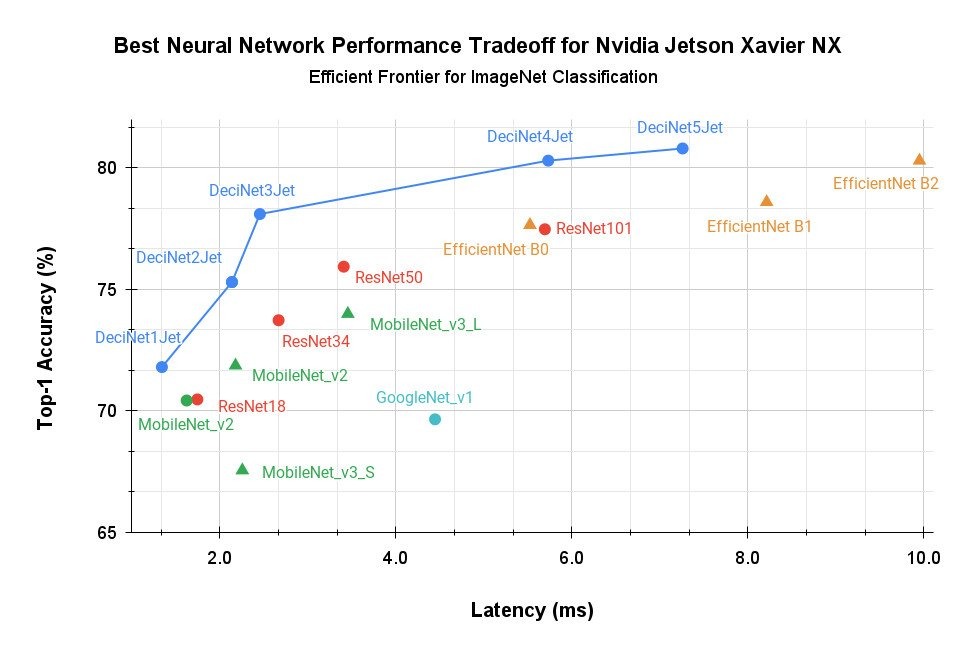

Читать далее «ZUBoard 1CG — недорогая плата для разработки AMD Xilinx Zynq UltraScale+ ZU1CG MPSoC FPGA»Модели искусственного интеллекта DeciNets поставляются с оптимизацией процессора Intel

Компания Deci представила созданные AutoNAC модели «DeciNets» для процессоров Intel Cascade Lake, которые, как утверждается, намного быстрее и точнее, чем другие модели классификации изображений для процессоров. Между тем, Aaeon объявила, что на ее платах UP доступен NPU Hailo-8.

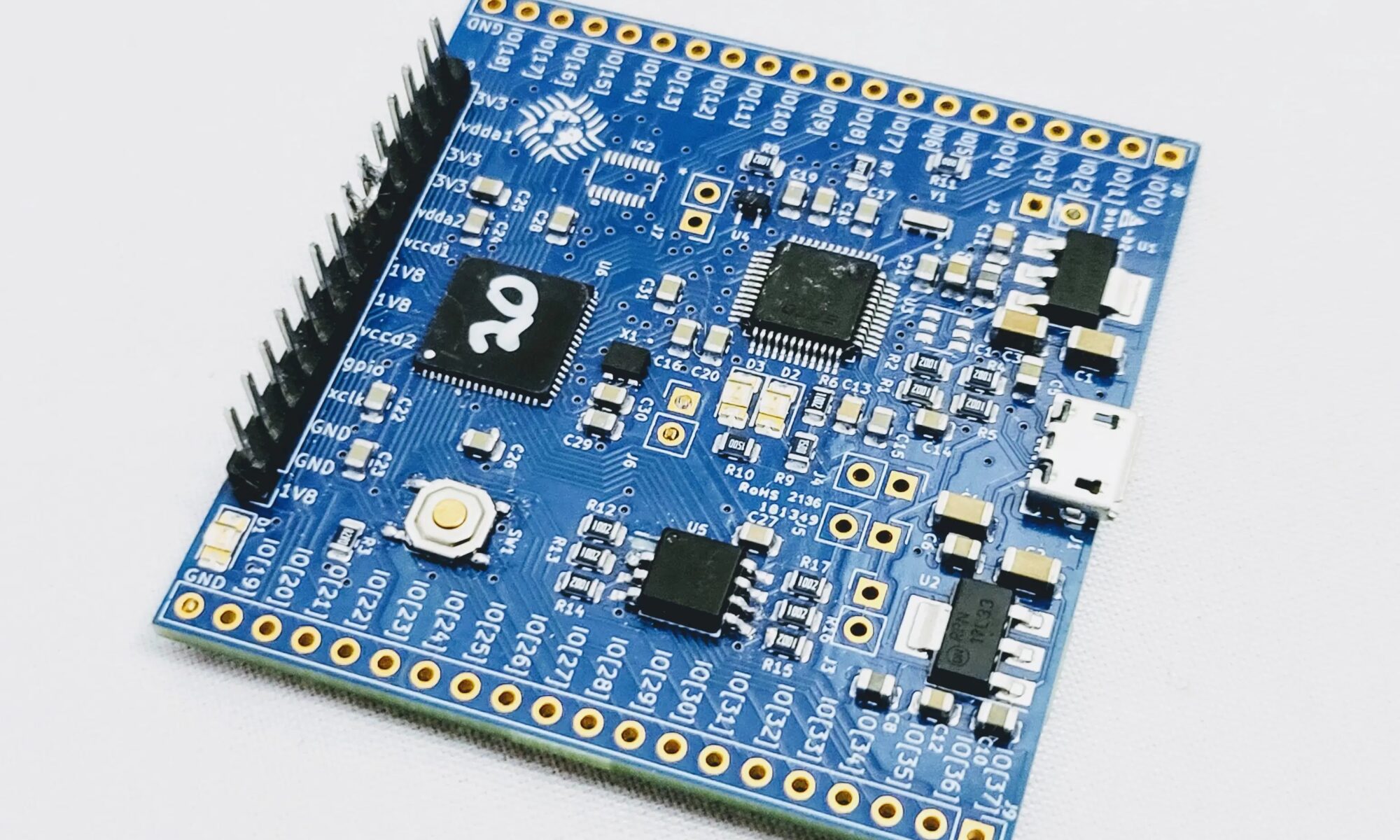

Читать далее «Модели искусственного интеллекта DeciNets поставляются с оптимизацией процессора Intel»OSZU3 System-in-Package (SiP) объединяет AMD Xilinx Zynq UltraScale+ MPSoC с 2 ГБ ОЗУ, PMIC и пассивными компонентами.

Octavo Systems сотрудничала с AMD Xilinx для создания системы-в-корпусе OSZU3 (SiP), которая объединяет Zynq UltraScale+ MPSoC ZU3 с оперативной памятью до 2 ГБ, схемой управления питанием и другими компонентами в компактном (40×20,5 мм) корпусе BGA размером 600-шариков BGA.

Читать далее «OSZU3 System-in-Package (SiP) объединяет AMD Xilinx Zynq UltraScale+ MPSoC с 2 ГБ ОЗУ, PMIC и пассивными компонентами.»CLEAR — это ASIC FPGA с открытым исходным кодом, предоставленный компанией Efabless

Конструкции процессоров с открытым исходным кодом доступны для работы на оборудовании FPGA, но немногие из них переходят на кремний из-за связанных с этим затрат. Именно поэтому пару лет назад был выпущен Google SkyWater PDK (комплект для проектирования процессов) вместе с предложением изготовить до 100 штук бесплатно по избранным проектам в сотрудничестве с Efabless.

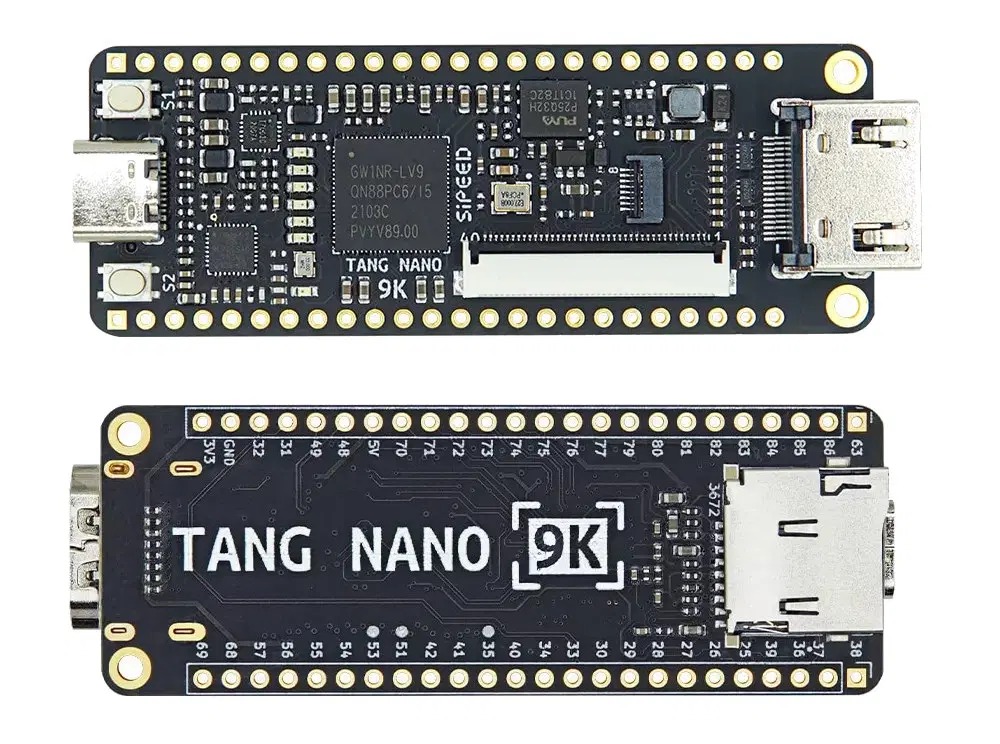

Читать далее «CLEAR — это ASIC FPGA с открытым исходным кодом, предоставленный компанией Efabless»Плата Tang Nano 9K FPGA может эмулировать программное ядро PicoRV32 RISC-V со всеми периферийными устройствами

Tang Nano 9K FPGA — это третья плата от Sipeed на основе GOWIN FPGA после оригинальной платы Tang Nano с 1K LUT и Tang Nano 4K, выпущенной в прошлом году с FPGA GW1NSR-LV4C (также известной как GW1NSR-4C), предлагающей 4068 логических блоков и 64 Мбит PSRAM. плюс процессор на основе ядра Arm Cortex-M3.

Модули FPGA SoC получают сетевой носитель и новую модель Polar Fire SoC

Несущая плата Enclustra «Mercury + PE3» для своих модулей FPGA/SoC Mercury/Mercury+ может действовать как SBC или подключаться к ПК через PCIe x8. Он предлагает QSFP+, 4x SFP +, FireFly и 2x GbE. Мы также исследуем новый модуль «Mercury + MP1», основанный на PolarFire SoC на базе RISC-V.

Читать далее «Модули FPGA SoC получают сетевой носитель и новую модель Polar Fire SoC»Компания Renesas представляет семейство FPGA стоимостью менее 50 центов с бесплатными инструментами разработки на основе Yosys

Компания Renesas представила семейство недорогих маломощных FPGA — ForgeFPGA, которые будут продаваться (в больших) объемах менее, чем за 50 центов. Этому способствовало приобретение в августе прошлого года компании Dialog Semiconductors, которая ранее разработала программируемую матрицу смешанных сигналов GreenPAK.

Читать далее «Компания Renesas представляет семейство FPGA стоимостью менее 50 центов с бесплатными инструментами разработки на основе Yosys»