На этой неделе Lime Microsystems выпустила LimeSDR XTRX, компактную и мощную плату программно-определяемого радио (SDR) в форм-факторе mini PCIe. В основе платы лежит AMD Artix 7 FPGA и ВЧ-трансивер Lime Microsystems LMS7002M, которые служат платформой для разработки цифровых и ВЧ-проектов с интенсивным использованием логики.

Читать далее «Новый LimeSDR XTRX выпускается в форм-факторе MiniPCIe»USB-ключ Machdyne FPGA оснащен 12-контактным PMOD

Kolibri — это USB-ключ, который объединяет FPGA Lattice iCE40, микроконтроллер RP2040 и разъем PMOD для расширения ввода-вывода. Компактное устройство также совместимо с Open Source Project IceStorm.

Kolibri оснащен маломощной FPGA Lattice из семейства iCE40, как и большинство устройств Machdyne.

Читать далее «USB-ключ Machdyne FPGA оснащен 12-контактным PMOD»Gowin Semi представляет оценочную плату Arora V 138K

На этой неделе компания Gowin Semiconductors анонсировала оценочную плату на основе серии GW5AT-138 FPGA, предназначенную для связи, обработки изображений серверов, автомобильных и других высокоскоростных приложений.

FPGA GW5AT (22-нм техпроцесс) относится к продукту пятого поколения семейства Gowin Arora. Обратитесь к странице GOWINSEMI Arora V FPGA для получения дополнительной информации.

Читать далее «Gowin Semi представляет оценочную плату Arora V 138K»Компьютер на базе FPGA можно использовать как персональный сервер

На днях компания Machdyne представила еще одну компактную встраиваемую плату на базе FPGA Lattice ECP5, которая может работать на Kakao Linux (частичный форк linux-on-litex-vexriscv ). Kopflos — это безголовый компьютер общего назначения, оснащенный портом LAN RJ45, разъемом JTAG и несколькими портами USB для дополнительных периферийных устройств.

Компьютер Kopflos использует FPGA Lattice ECP5 (LFE5U-12F), аналогичную другим платам, выпущенным в прошлом году компанией Machdyne (например, Noir и Schoko).

Читать далее «Компьютер на базе FPGA можно использовать как персональный сервер»Achronix Speedster7t AC7t1500 FPGA теперь доступен для приложений с высокой пропускной способностью

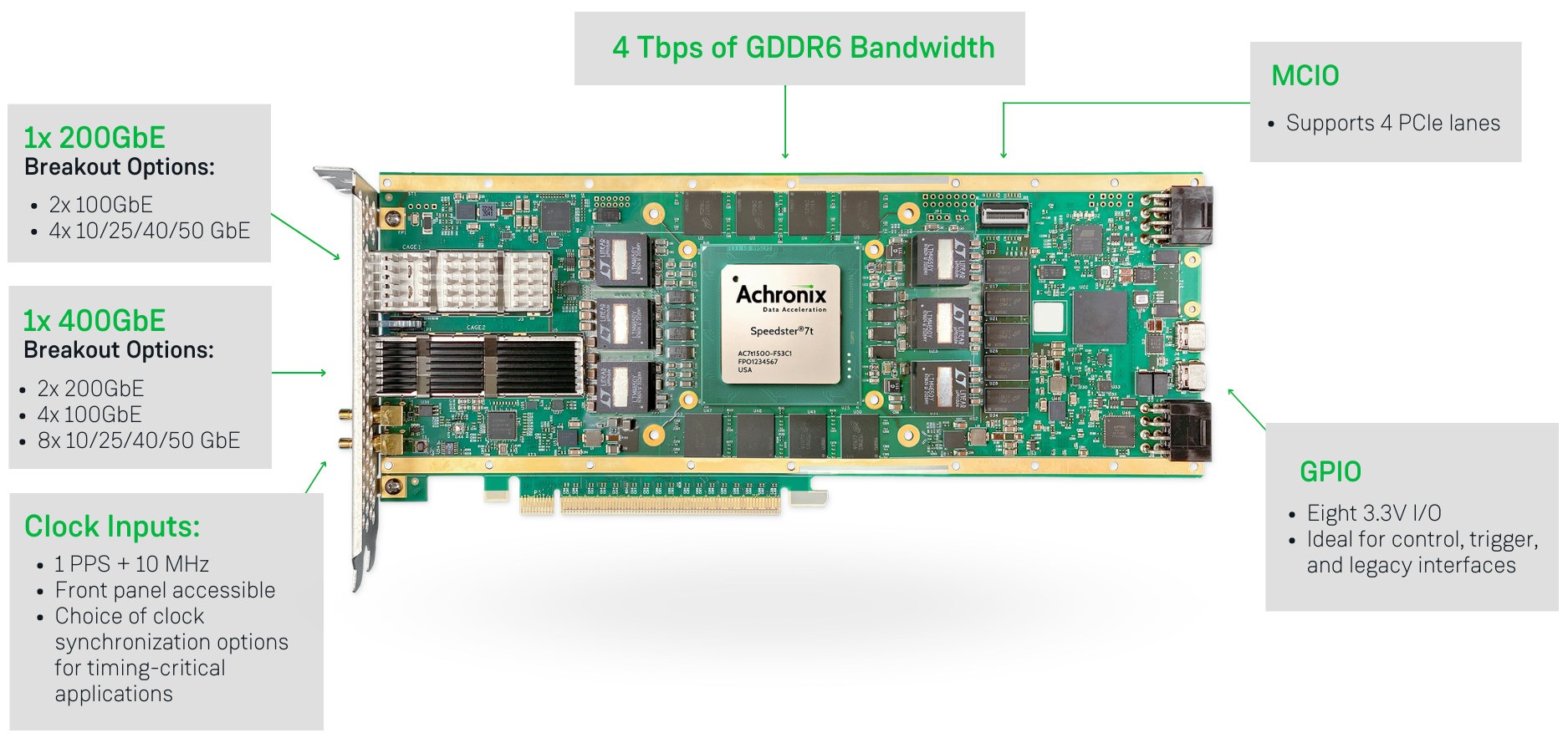

Компания Achronix Semiconductor недавно объявила об общедоступной Speedster7t AC7t1500 FPGA, предназначенной для приложений ускорения сетей, хранения и вычислений (AI/ML).

Семейство 7-нм Speedster7t FPGA предлагает порты PCIe Gen5 и интерфейсы памяти GDRR6 и DDR5/DDR4, обеспечивает скорость до 400 Гбит/с на портах Ethernet и включает в себя 2D-сеть на кристалле (2D NoC), которая может обрабатывать 20 Тбит/с общей пропускной способности.

Читать далее «Achronix Speedster7t AC7t1500 FPGA теперь доступен для приложений с высокой пропускной способностью»XRF16 Gen3 SOM оснащен Xilinx Zynq UltraScale+ ZU49DR RFSoC с полосой пропускания до 6 ГГц

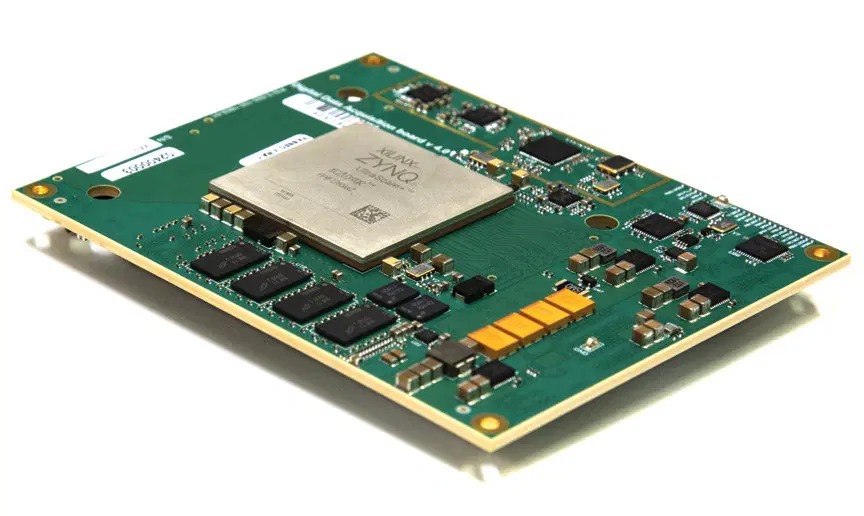

Несколько раз, в течение нескольких лет мы писали о процессорах Xilinx Zynq UltraScale+ MPSoC, которые объединяют ядра Arm Cortex-A53/R5 и графический процессор Mali-400 с матрицей Ultrascale FPGA. Но AMD-Xilinx также предлагает одночиповые адаптируемые радиоплатформы Zynq UltraScale+ RFSoC, поддерживающие аналоговую полосу пропускания до 7,125 ГГц.

Эта тема привлекла наше внимание из-за предстоящей ZU49DR SoM от iWave Systems, которая, похоже, находится в стадии разработки, но мы также заметили, что компания Avnet в прошлом году запустила решение XRF16 Gen3 SoM с тем же Zynq Ultrascale + ZU49DR RFSoC третьего поколения с 16 RF- АЦП, 16 каналов РЧ-ЦАП и полоса пропускания РЧ 6 ГГц.

Читать далее «XRF16 Gen3 SOM оснащен Xilinx Zynq UltraScale+ ZU49DR RFSoC с полосой пропускания до 6 ГГц»Плата STEPFPGA FPGA программируется с помощью Web IDE (Crowdfunding)

Миниатюрная плата для разработки FPGA STEPFPGA MXO2Core основана на FPGA Lattice MXO2-4000 и предназначена для обучения с простой в использовании Web IDE вместо более традиционных инструментов и подробными учебными пособиями.

Плата также оснащена 2-значным сегментным дисплеем, несколькими светодиодами, кнопками и 4-позиционным DIP-переключателем, а также двумя рядами по двадцать контактов для расширения ввода-вывода и портом USB Type-C, используемым для питания, программирование или хранилища.

Читать далее «Плата STEPFPGA FPGA программируется с помощью Web IDE (Crowdfunding)»Промышленная камера USB Type-C с открытым исходным кодом оснащена платформой Lattice Crosslink NX FPGA

Гаурав Сингх (Gaurav Singh), выступая в роли Circuit Valley, разработал промышленную камеру USB 3.0 Type-C с открытым исходным кодом с тремя платами: одна для сбора данных с помощью датчика CMOS, другая — на базе платформы Lattice Crosslink NX FPGA — для обработки изображений и, наконец, плата, оснащенная контроллером Infineon FX3 USB 3.0 для отправки видеоданных на хост.

Читать далее «Промышленная камера USB Type-C с открытым исходным кодом оснащена платформой Lattice Crosslink NX FPGA»