На прошлой неделе мы рассмотрели универсальный микроконтроллер Gigadevice GD32V с ядром RISC-V «Bumblebee», и нам сообщили, что Andes Technology недавно представила IP-ядро AndesCore N22 RISC-V «Bumblebee», способное поддерживать наборы команд RV32IMAC или RV32EMAC.

Поиск в Интернете не дал информации о том, что конкретно представляют собой ядра RISC-V «Bumblebee», или, может быть, речь идет о том, что многие из них могут быть в паре параллельно. Но, это только небольшая тонкость, давайте посмотрим на детали, которые может предложить ядро AndesCore N22. Ядро RISC-V разработано для микроконтроллеров начального уровня, встречается в IoT-устройствах и носимых устройствах, и способно к глубокой встроенной обработке протоколов для управления вводом/выводом, хранением, сетевым подключением, AI и AR/VR.

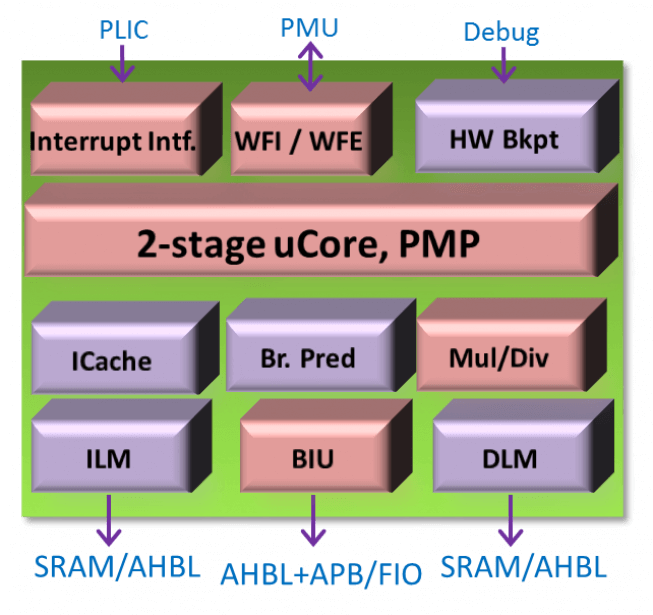

Основные характеристики AndesCore N22:

- Архитектура набора инструкций (ISA) AndeStar V5 (RV32IMAC) / V5e (RV32EMAC), совместимая с технологией RISC-V плюс расширения Andes, созданные для повышения производительности и функциональности

- 32-битная двухступенчатая конвейерная архитектура процессора

- 16/32-битный смешиваемый формат команд для уплотнения плотности кода

- Прогнозирование ветвления для ускорения управления кодом

- Настраиваемый множитель

- Защита физической памяти (PMP)

- Core-Local Interrupt Controller (CLIC) с выборочной векторизацией и приоритетным вытеснением

- Гибко конфигурируемый контроллер прерываний на уровне платформы (PLIC) для поддержки SoC с несколькими процессорами

- Усовершенствованная технология CoDense для уменьшения размера программного кода

- Аппаратное обеспечение StackSafe, помогающее измерять размер стека и обнаруживать переполнение/опустошение во время выполнения

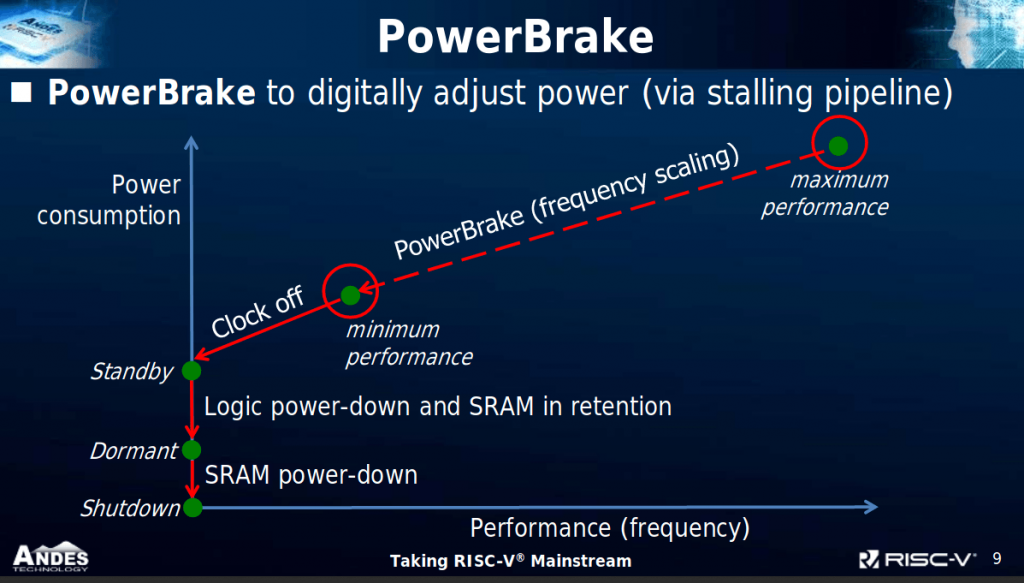

- PowerBrake для цифровой регулировки мощности (через остановочный конвейер)

- Несколько конфигураций для компромисса между размером ядра и требованиями к производительности

Недавняя презентация на английском языке дает нам более подробную информацию, и, например, утверждается, что AndesCore N22 обладает «превосходным PPA (мощность, производительность и площадь)»:

- Минимальная полезная конфигурация: <15K выходов

- Динамическая мощность: 1,36 мкВт / МГц при 28 нм

- Производительность: 3,95 CoreMark / МГц

- Максимальная частота: до 700 МГц в наихудшем случае

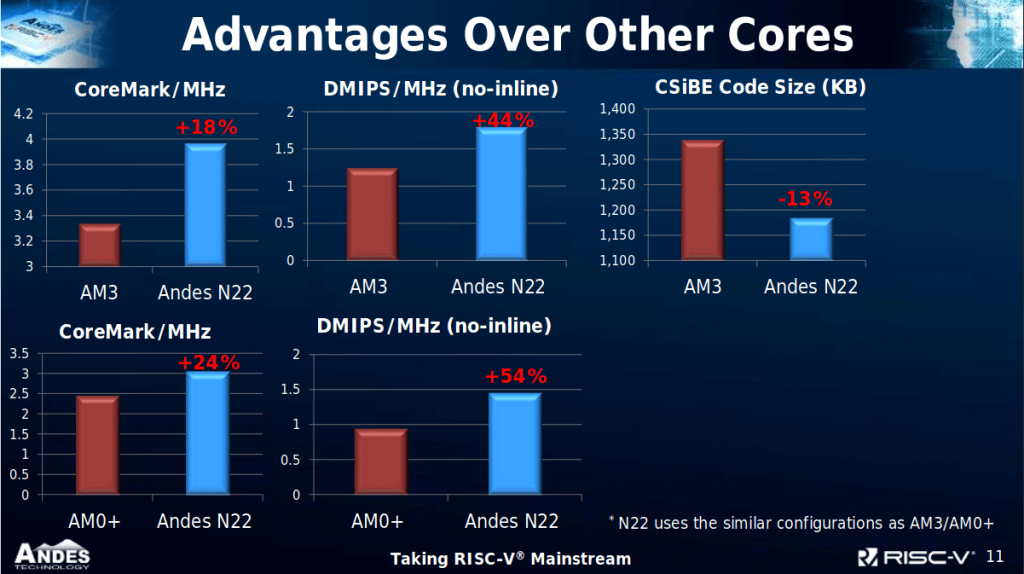

Документ также показывает производительность, занимаемую площадь (размер кода) и эффективность ядра Andes N22 RISC-V по сравнению с ядрами Arm Cortex-M3 и M0 + в аналогичной конфигурации.

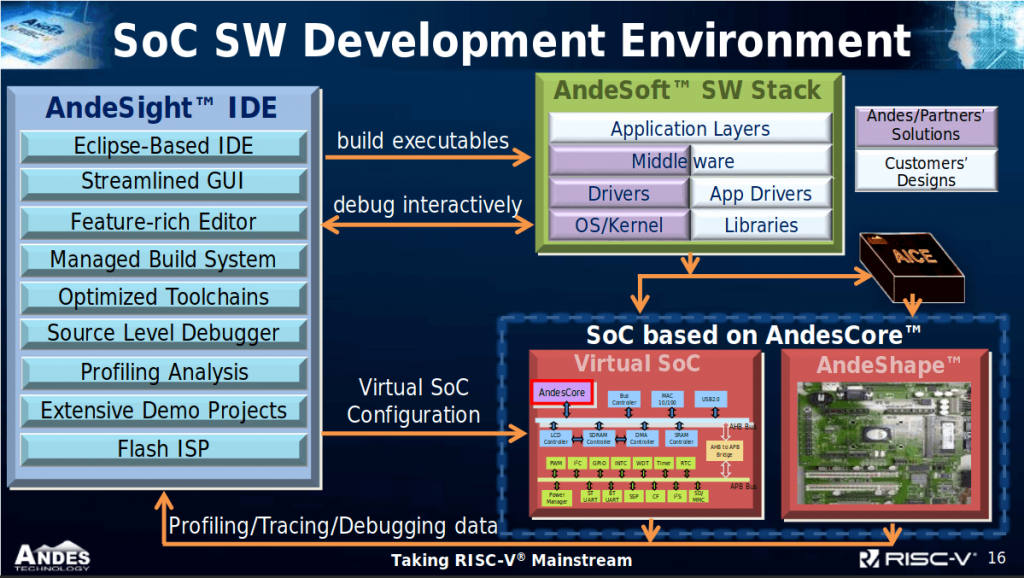

Andes также предоставляет инструменты для разработки, в том числе бесплатную загрузку IDE на основе AndeSight Eclipse, программный стек AndeSoft, а также две платы разработки на основе AndeShape FPGA, а именно Arduino-совместимую плату Corvette-F1 и полнофункциональный набор для разработки ADP-XC7K, отладочное оборудование, такое как AICE-MINI + и AICE-MICRO.

Ядро AndesCore N22 официально поддерживается сообществами GNU и LLVM, доступно несколько оптимизированных библиотек, таких как MCUlib и newlib, и примеры программ. Новое ядро RISC-V MCU поддерживает FreeRTOS с открытым исходным кодом и коммерчески поддерживаемые операционные системы реального времени Express Logic ThreadX. Компания также упоминает операционные системы «RISC-V Ready», такие как Zephyr, RT-Thread, µC / OS-II, MyNewt, SylixOS, LiteOS или AliOS Things, которые, как мы понимаем, могут не поддерживаться официально (пока), но уже работают с общими ядрами RISC-V.

Вы можете найти более подробную информацию на странице продукта, а также посмотреть видео ниже, сопровождающее вышеупомянутую презентацию.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.