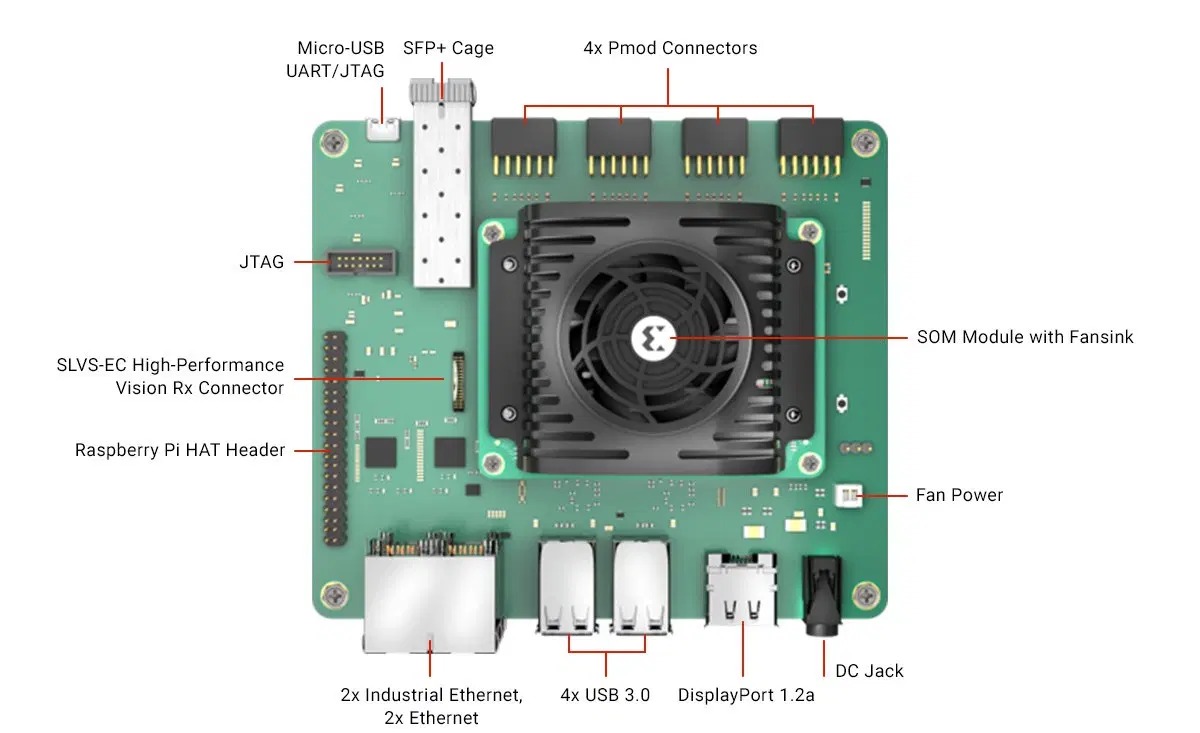

Стартовый комплект для робототехники AMD Xilinx Kria KR260 включает систему Kria K26 Zynq UltraScale+ XCK26 FPGA MPSoC (SoM), представленную в прошлом году вместе со стартовым комплектом Kria KV260 Vision AI.

Читать далее «Стартовый комплект AMD Kria KR260 Robotics Starter Kit за 349 долларов США конкурирует с набором для разработки NVIDIA Jetson AGX Xavier»Плата контроллера дрона работает под управлением Linux на Zynq UltraScale+

Плата контроллера Topic «Платформа БПЛА и робототехники» работает под управлением Linux, ROS и PX4 на Zynq UltraScale + и обеспечивает WiFi/BT, GPS, несколько датчиков, 4x моторных ввода-вывода и 2x MIPI-CSI. Комплект разработчика добавляет камеры, PS, отладку и многое другое.

Читать далее «Плата контроллера дрона работает под управлением Linux на Zynq UltraScale+»Система SDR на базе процессора Jetson оснащена обновленным программным обеспечением AirStack

В выпуск Deepwave Digital v0.5.0 стека AirStack SDR на основе Ubuntu добавлены частоты дискретизации CV и улучшенная поддержка восстановления. AirStack работает на Deepwave AIR-T и новых надежных системах AIR-T Edge на базе Jetson TX2i, Artix-7 FPGA и приемопередатчика AD.

Читать далее «Система SDR на базе процессора Jetson оснащена обновленным программным обеспечением AirStack»Xilinx представляет серию Versal AI Edge с ядрами Cortex-A72 и R5 и структурой FPGA

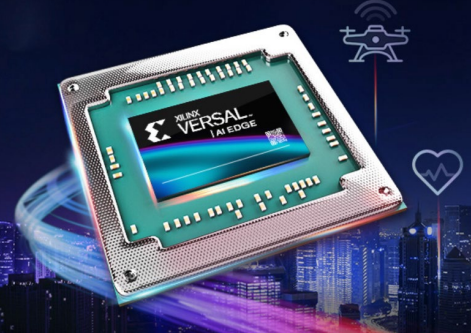

Edge AI решает проблемы с задержкой и безопасностью за счет ускорения AI на устройстве для оптимальных вычислений при низком энергопотреблении. Xilinx объявляет о выпуске серии Versal AI Edge, которая является 4-м членом семейства Adaptive Compute Acceleration Platform (ACAP). Серия Versal состоит из семи моделей от VE2002 до VE2802 с процессором, изготовленным по 7 нм кремниевой технологии.

Читать далее «Xilinx представляет серию Versal AI Edge с ядрами Cortex-A72 и R5 и структурой FPGA»Xilinx представляет Kria K26 SoM и комплект разработчика Vision AI на базе Zynq Ultrascale + XCK26 FPGA MPSoC

Поставщики кремния обычно сосредотачиваются на дизайне микросхем и предоставляют дорогостоящий оценочный комплект первым клиентам, оставляя разработку экономичных плат и систем-на-модулях компаниям, производящим встраиваемые системы.

Читать далее «Xilinx представляет Kria K26 SoM и комплект разработчика Vision AI на базе Zynq Ultrascale + XCK26 FPGA MPSoC»Компания Xilinx выпустила открытый исходный код Vitis HLS для разработки FPGA (только Front-end)

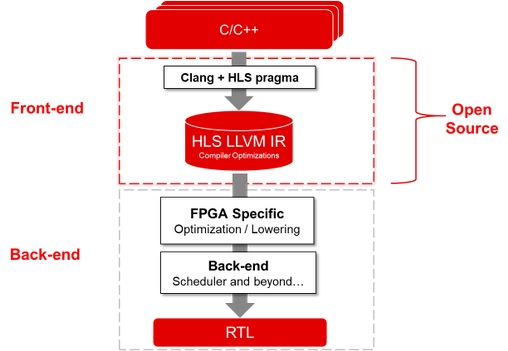

Хотя есть некоторые программы с открытым исходным кодом для разработки FPGA, такие как Symbiflow или Yosys, поставщики FPGA обычно предоставляют только программы с закрытым исходным кодом для разработчиков, желающих работать над своими чипами.

Читать далее «Компания Xilinx выпустила открытый исходный код Vitis HLS для разработки FPGA (только Front-end)»Amazon EC2 F1 Instances подключит Xilinx Virtex Ultrascale+ FPGA платы к облаку

Ранее уже встречались несколько плат и модулей на базе Xilinx Zynq Ultrascale+ MPSoC, таких как AXIOM Board и Trenz TE0808 SoM, обе платы с ZU9EG MPSoC, системы продаются по несколько тысяч долларов. Но появилась информация о том, что вам не нужно приобретать плату для использования Virtex UltraScale+ FPGAs, которая отличается от Zynq UltraScale+, тем что у нее нет ARM CPU & GPU, она как правило оснащена более мощным FPGA. В ноябре прошлого года Amazon запустили предварительную версию F1 instances дающую доступ к оборудованию данного типа, через их облако. Читать далее «Amazon EC2 F1 Instances подключит Xilinx Virtex Ultrascale+ FPGA платы к облаку»

OpenAMP платформа с открытым кодом обеспечивающая связь между Linux, RTOS и приложениями Bare Metal в гетерогенных встраиваемых системах

Интегрированные системы становятся все более сложными и выходят за пределы однородных многоядерных систем путем смешивания различных типов ядер, таких как ядра высокой производительности, ядра низкой мощности в реальном времени, или даже FPGA структура. Примеры включают NXP i.MX6 SoloX с ядром ARM Cortex A9 для Linux-приложений и ядро ARM Cortex M4 для задач реального времени, или Xilinx Zynq UltraScale+ MPSoC с ядром Cortex A53 для приложений высшего уровня, ядро Cortex R5 для обработки в режиме реального времени и Ultrascale FPGA логика. Все эти разные ядра под управлением собственных ОС на базе Linux, RTOS или bare metal приложения, все это делает разработку программного обеспечения еще более сложной задачей. В целях снижения сложности, а также для решения некоторых проблем, Multicore Association запустила новую рабочую группу нацеленную на управление, расширение и стандартизацию OpenAMP (Open Asymmetric Multi Processing), открытый исходный код который позволяет операционным системам взаимодействовать в широком диапазоне сложных гомогенных и гетерогенных архитектур, и позволяет производить асимметричную многопроцессорную обработку приложений используя параллелизм, предлагаемый в многоядерной конфигурации. Читать далее «OpenAMP платформа с открытым кодом обеспечивающая связь между Linux, RTOS и приложениями Bare Metal в гетерогенных встраиваемых системах»