Хотя есть некоторые программы с открытым исходным кодом для разработки FPGA, такие как Symbiflow или Yosys, поставщики FPGA обычно предоставляют только программы с закрытым исходным кодом для разработчиков, желающих работать над своими чипами.

Недавно компания Xilinx предприняла шаги, чтобы выполнить свое «обязательство по поддержке инициатив разработчиков и исследователей с открытым исходным кодом», выпустив исходный код Vitis HLS Front-End.

Что такое Vitis HLS?

Прежде чем рассмотреть выпуск исходного кода, стоит узнать, что именно делает Vitis HLS. Компания описывает его как инструмент синтеза высокого уровня (HLS), который позволяет функциям C, C ++ и OpenCL подключаться к логической матрице устройства и блокам RAMDSP. Он реализует аппаратные ядра в потоке ускоренной разработки приложений Vitis и использует код C/C ++ для разработки RTL IP для проектов FPGA в среде разработки Vivado Design Suite от Xilinx.

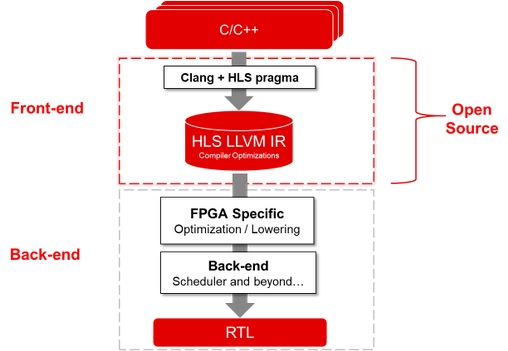

Схема проектирования Vitis HLS выглядит следующим образом:

- Компилируйте, моделируйте и отлаживайте алгоритм C / C ++.

- Просматривайте отчеты для анализа и оптимизации дизайна.

- Синтезируйте алгоритм C в проект RTL.

- Проверьте реализацию RTL с помощью совместного моделирования RTL.

- Упакуйте реализацию RTL в расширение скомпилированного объектного файла (.xo) или экспортируйте в IP-адрес RTL.

Частичный выпуск с открытым исходным кодом

Ключевое слово в выпуске — «Front-End», поскольку внутренняя часть Vitis HLS, обрабатывающая специфическую для FPGA оптимизацию и планирование перед генерацией кода RTL, все еще является закрытым исходным кодом.

Интерфейсный исходный код позволит разработчикам программного и аппаратного обеспечения использовать стандартную инфраструктуру Clang/LLVM и настраивать процесс проектирования, чтобы добавить поддержку новых языков высокого уровня, новых оптимизации для конкретных областей или директив компилятора, а также настроить преобразования в LLVM IR (промежуточные представления). Исходный код интерфейса Vitis HLS можно найти на Github.

Версия с открытым исходным кодом Vitis HLS front-end уже используется компаниями и университетами, получившими код заранее. Плагин SLX от Silexica расширяет возможности преобразования кода Vitis HLS 2020.2 для улучшения результатов задержки и пропускной способности Vitis HLS. В то время как Иллинойсский университет в Урбана-Шампейн интегрировал новые прагмы Clang и LLVM для оценки, аспирант Имперского колледжа Лондона использовал код для интеграции динамического и статического планирования (DASS) в поток HLS, а Гонконгский университет науки и технологий (HKUST) разработал два проекта, а именно: «Высокоэффективную автоматическую оптимизацию фазового упорядочения» и «Multi-FPGA HLS» с использованием машинного обучения и эвристических алгоритмов для повышения производительности и потребления ресурсов, а также нескольких FPGA, соединенных с сетью или памятью DDR.

Дополнительную информацию вы найдете в объявлении.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.