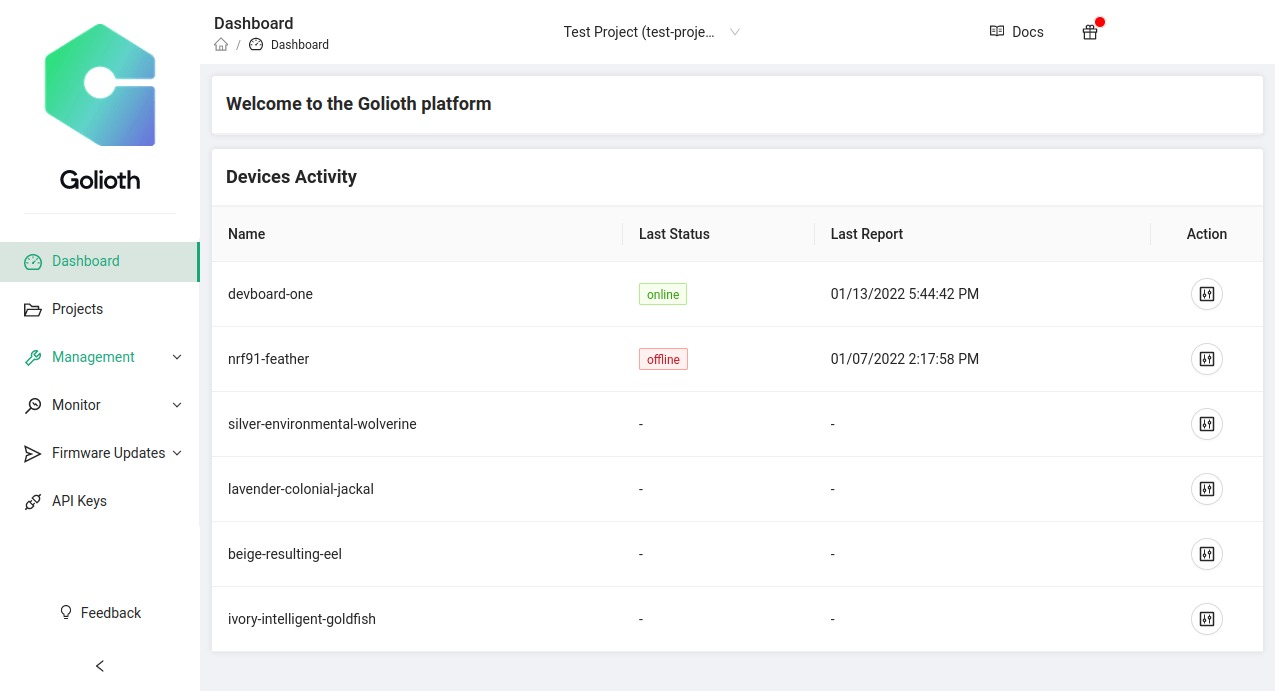

Уже существует множество платформ для разработки интернета вещей, но представлена еще одна — Golioth, которая предлагает Zephyr SDK, поддержку “первого уровня” для Nordic Semiconductor nRF9160 (сотовая связь) и Espressif Systems ESP32-C3 (Wi-Fi), а также симулятор на базе QEMU для удобства тестирования.

Читать далее «Платформа для разработки интернета вещей Goliath предлагает Zephyr SDK, поддержку nRF9160, ESP32 и более 100 других платформ»Плата разработки WCH CH32V307 RISC-V имеет 8 портов UART, управляемых через Ethernet

CH32V307V-EVT-R1 — это макетная плата на базе микроконтроллера WCH CH32V307 RISC-V с портами Ethernet и USB Type-C и восемью интерфейсами UART, доступными через разъемы.

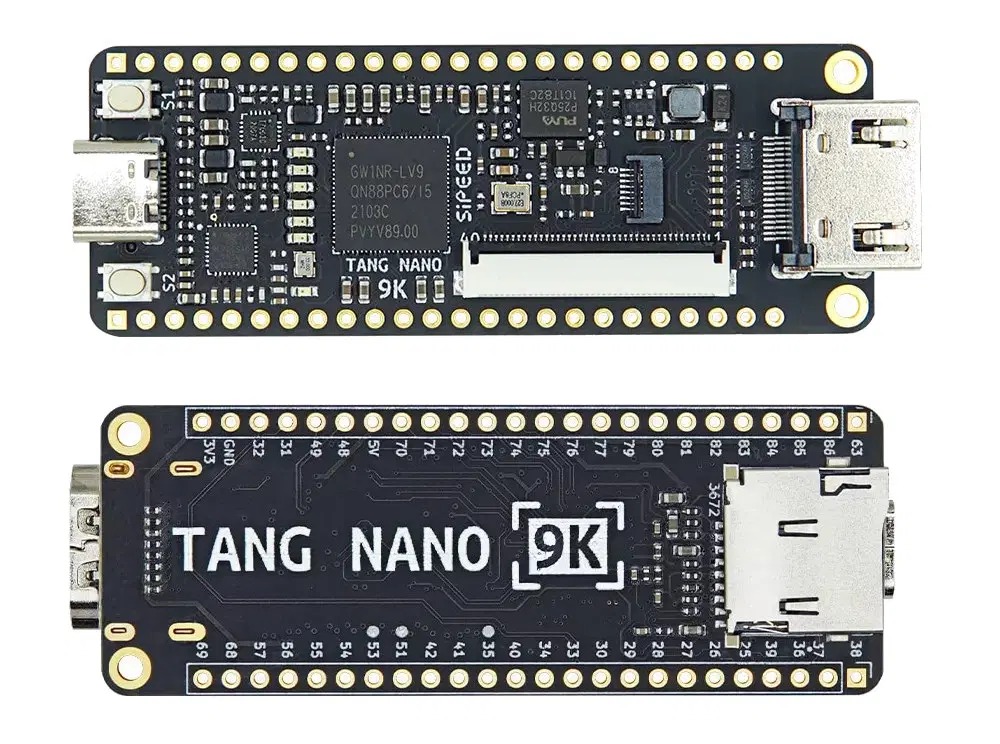

Читать далее «Плата разработки WCH CH32V307 RISC-V имеет 8 портов UART, управляемых через Ethernet»Плата Tang Nano 9K FPGA может эмулировать программное ядро PicoRV32 RISC-V со всеми периферийными устройствами

Tang Nano 9K FPGA — это третья плата от Sipeed на основе GOWIN FPGA после оригинальной платы Tang Nano с 1K LUT и Tang Nano 4K, выпущенной в прошлом году с FPGA GW1NSR-LV4C (также известной как GW1NSR-4C), предлагающей 4068 логических блоков и 64 Мбит PSRAM. плюс процессор на основе ядра Arm Cortex-M3.

Выпуск Linux 5.16 – Основные изменения, архитектуры Arm, RISC-V и MIPS

Линус Торвальдс только что объявил о выпуске Linux 5.16:

Изменений немного со времени -rc8, что ожидаемо. Дополнительная неделя была связана с праздниками, и не возникло большого количества задач последнего момента, требующих решения.

Читать далее «Выпуск Linux 5.16 – Основные изменения, архитектуры Arm, RISC-V и MIPS»

Процессор Intel Mobileye EyeQ Ultra RISC-V предназначен для автономного вождения уровня 4

Продолжим освещать новинки, представленными на выставке CES 2022. Изюминкой выставки стал чип EyeQ Ultra от Mobileye — дочерней компании Intel, который не содержит ядер x86, вместо этого автомобильный процессор оснащен 12 ядрами RISC-V, графическим процессором Arm и DSP и призван обеспечить автономное вождение 4-го уровня, благодаря ускорителю искусственного интеллекта 176 TOPS.

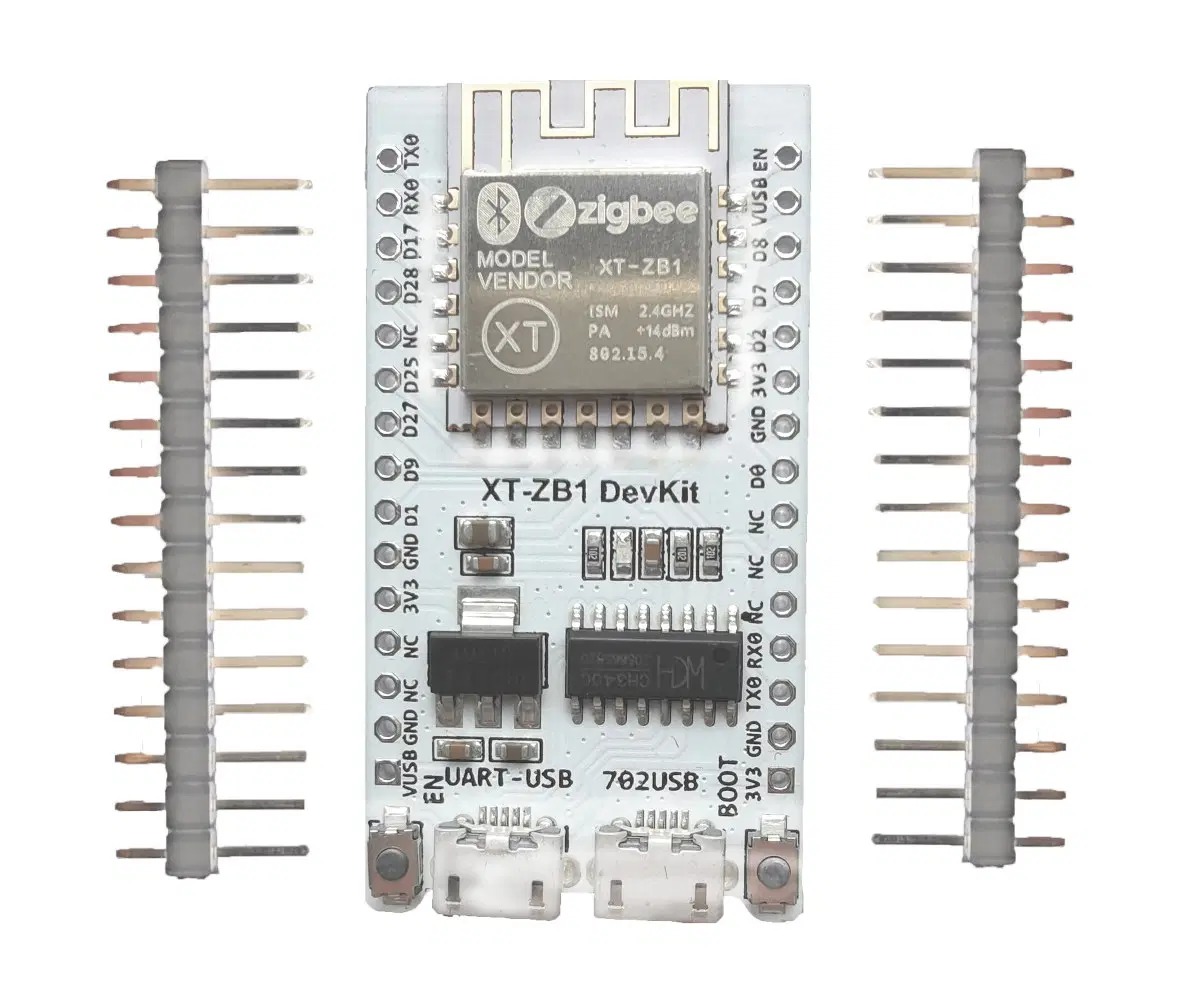

Читать далее «Процессор Intel Mobileye EyeQ Ultra RISC-V предназначен для автономного вождения уровня 4»Комплект для разработки XT-ZB1 Zigbee & BLE за $1.9 включает RISC-V модуль BL702

Bouffalo Labs BL702 — это 32-битный микроконтроллер RISC-V с радиомодулем 2,4 ГГц для подключения Zigbee 3.0 и Bluetooth 5.0 LE, который впервые был представлен в UART & JTAG отладочной плате Sipeed RV-Debugger Plus, в которой радиомодуль вообще не использовался.

Но сейчас на рынке появился комплект для разработки XT-ZB1 на базе Zigbee & BLE модуля BL702, который продается всего $1.9 за штуку на Aliexpress. Правда за доставку придется отдать $5.6, но там также есть комплекты по 5 или 10 штук с той же стоимостью доставки, а это означает, что если вы купите 10 штук, общая стоимость будет составлять $24, включая доставку, а это примерно $2.4 за плату. Примечание, только модуль стоит $1. Читать далее «Комплект для разработки XT-ZB1 Zigbee & BLE за $1.9 включает RISC-V модуль BL702»

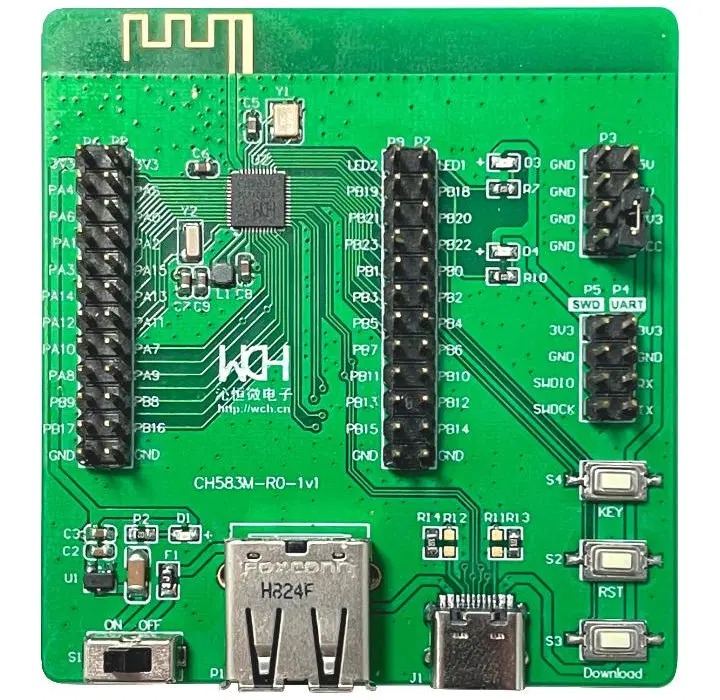

Микроконтроллер CH583 RISC-V поддерживает Bluetooth 5.3 LE

Вслед за микроконтроллером CH572 RISC-V BLE с 10 КБ SRAM, WCH представила микроконтроллер CH583 RISC-V с 32 КБ SRAM, 1 МБ флэш-памяти и поддержкой новейшего стандарта Bluetooth 5.3 LE.

Читать далее «Микроконтроллер CH583 RISC-V поддерживает Bluetooth 5.3 LE»Модуль Sipeed Lichee RV RISC-V получает несущую плату стоимостью 5 долларов США с портами HDMI и USB, а также опциональный Wi-Fi

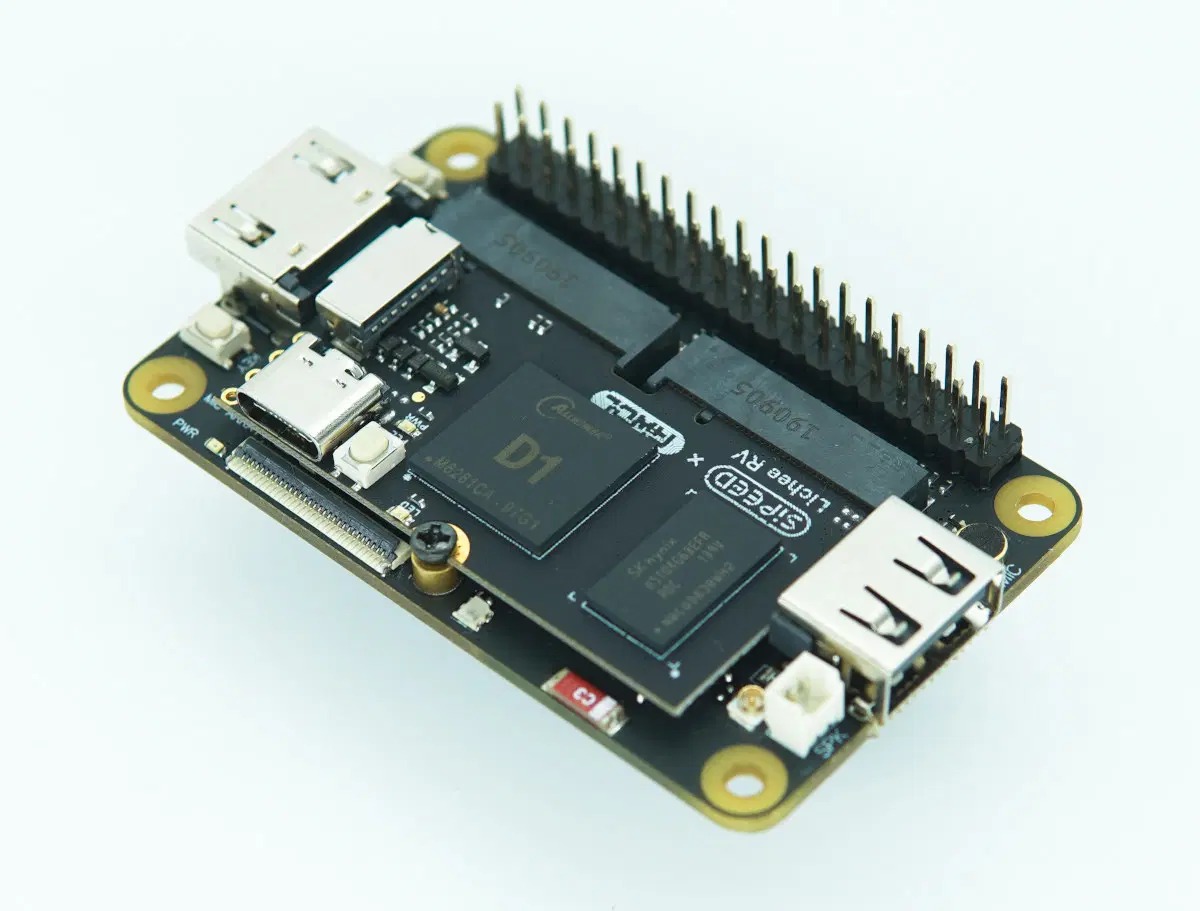

В прошлом месяце компания Sipeed представила плату Lichee RV Allwinner D1 Linux RISC-V по цене всего 17 долларов с 512 МБ ОЗУ. Хотя с портом USB-C он может использоваться как отдельная часть, его двойной разъем M.2 делает его больше похожим на модуль, и мы отметили, что в то время в разработке находилась крошечная несущая плата.

Читать далее «Модуль Sipeed Lichee RV RISC-V получает несущую плату стоимостью 5 долларов США с портами HDMI и USB, а также опциональный Wi-Fi»