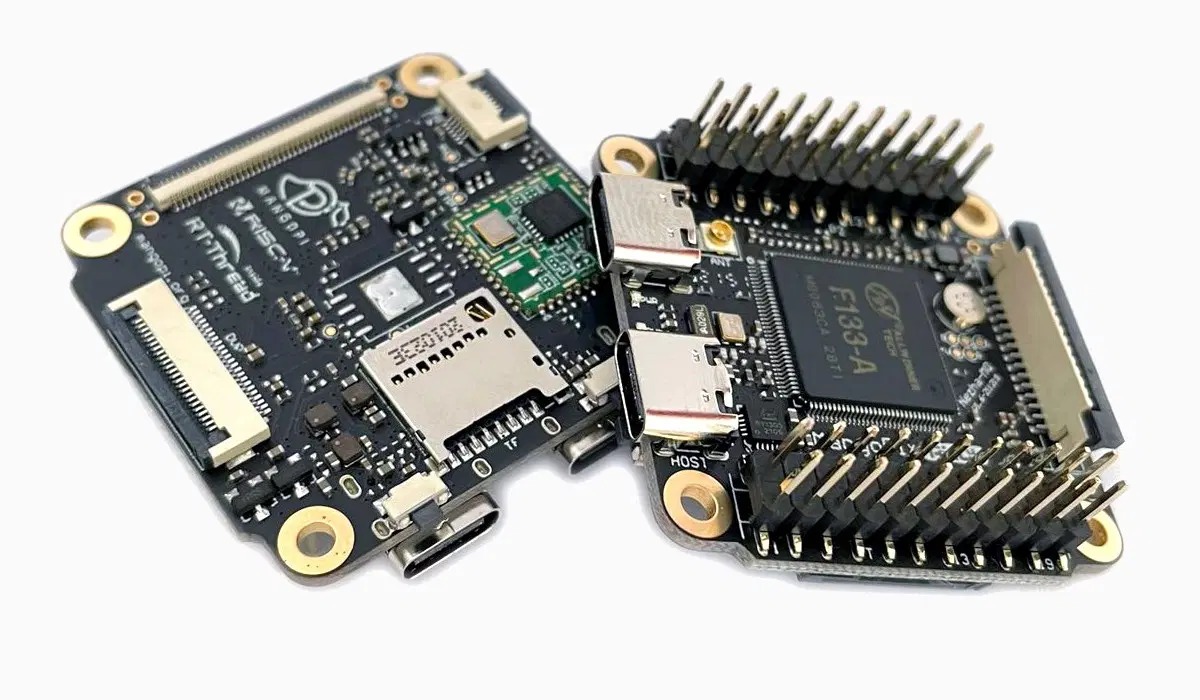

На днях в продажу на Crowd Supply поступила крошечная плата разработчика MangoPi-Nezha MQ с процессором Allwinner F133-A (он же Allwinner D1s) RISC-V с 64 МБ встроенной оперативной памяти за 39 долларов, а поставка ожидается в июле 2022 года.

Читать далее «Плата разработчика MangoPi-Nezha MQ RISC-V за 39 долларов США работает под управлением OpenWrt, Debian или RT-Smart RTOS (Crowdfunding)»Ядра Codasip L31 и L11 RISC-V для AI/ML поддерживают TFLite Micro, пользовательская настройка

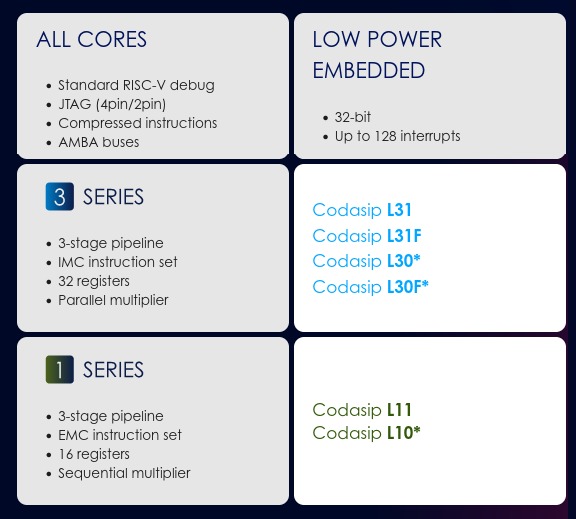

Codasip анонсировала маломощные встроенные процессорные ядра RISC-V L31 и L11, оптимизированные для настройки периферийных приложений AI/ML IoT с ограничениями по мощности и размеру.

Читать далее «Ядра Codasip L31 и L11 RISC-V для AI/ML поддерживают TFLite Micro, пользовательская настройка»Конкурс проектирования RISC-V — получите бесплатную плату, чипы RISC-V и денежные призы.

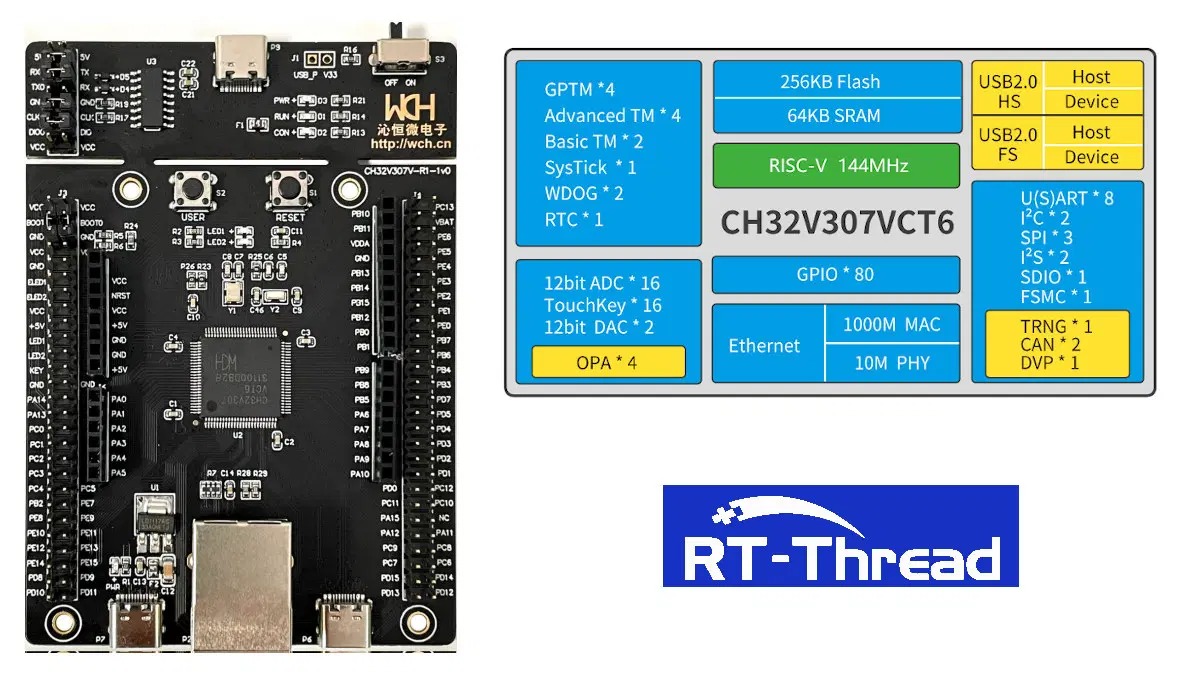

Некоторое время назад мы писали о 32-разрядном микроконтроллере RISC-V WCH CH32V307, который был обнаружен на плате с восемью портами UART, управляемыми через Ethernet или USB, и компания выпустила некоторый исходный код для использования платы, приглашая сообщество отправлять запросы на включение в проект.

Читать далее «Конкурс проектирования RISC-V — получите бесплатную плату, чипы RISC-V и денежные призы.»RISC-V или Arm? Крошечная плата на базе Linux, размером 4×4 см с Wi-Fi, предлагает оба варианта

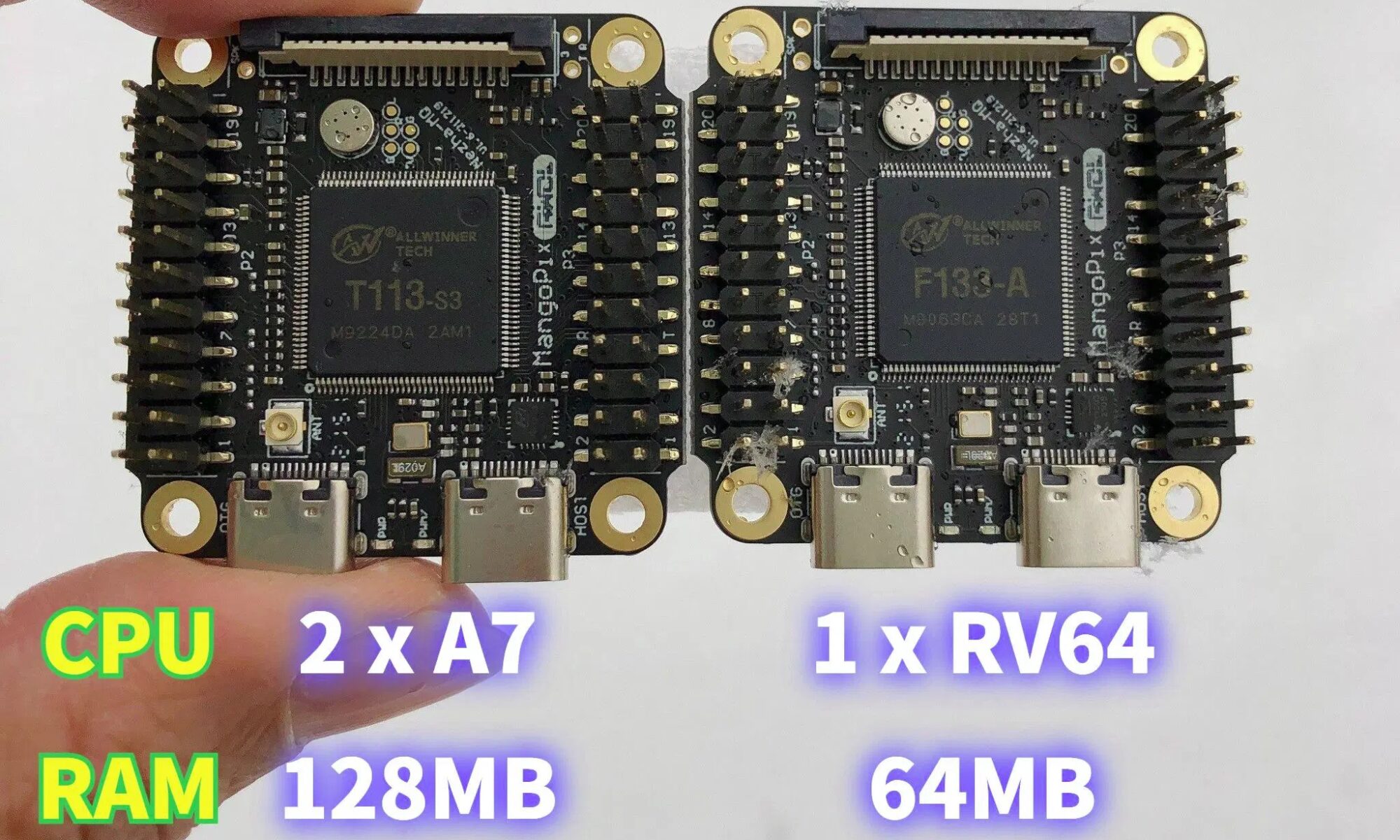

Прошлой осенью мы писали о процессоре Allwinner D1s / F133-A RISC-V и готовящейся к выпуску MangoPi MQ1 — крошечной плате размером 4×4 см на базе этого процессора. Плата не продается, но у нас есть более подробная информация, и компания также работает над версией Arm, оснащенной процессором Allwinner T113-S3 с двумя ядрами Cortex-A7, совместимым по контактам с F133-A SoC.

CLEAR — это ASIC FPGA с открытым исходным кодом, предоставленный компанией Efabless

Конструкции процессоров с открытым исходным кодом доступны для работы на оборудовании FPGA, но немногие из них переходят на кремний из-за связанных с этим затрат. Именно поэтому пару лет назад был выпущен Google SkyWater PDK (комплект для проектирования процессов) вместе с предложением изготовить до 100 штук бесплатно по избранным проектам в сотрудничестве с Efabless.

Читать далее «CLEAR — это ASIC FPGA с открытым исходным кодом, предоставленный компанией Efabless»Intel инвестирует 1 миллиард долларов в инновации в литейном производстве и становится членом RISC-V International

Компания Intel на днях объявила о создании фонда в размере 1 миллиарда долларов для поддержки компаний, внедряющих инновации и новые технологии в литейную экосистему. Компания заявляет, что фонд будет уделять приоритетное внимание инвестициям в «возможности, которые ускоряют время выхода клиентов на рынок, включая интеллектуальную собственность (ИС), программные инструменты, инновационные архитектуры микросхем и передовые технологии упаковки».

Читать далее «Intel инвестирует 1 миллиард долларов в инновации в литейном производстве и становится членом RISC-V International»Сравнение модулей ESP32-S3, ESP32-C3 и ESP8266

Компания Ai-Thinker недавно представила модули ESP-S3-12K на основе чипа ESP32-S3. Он поддерживает 2.4 ГГц WiFi и Bluetooth 5 LE. Чип беспроводной сети ESP32-S3 оснащен 32-битным двухъядерным процессором Xtensa LX7 с тактовой частотой до 240 МГц и дополнительными векторными инструкциями для ускорения ИИ, а также надежным механизмом шифрования безопасности, специально разработанным для рынка AIoT. Читать далее «Сравнение модулей ESP32-S3, ESP32-C3 и ESP8266»

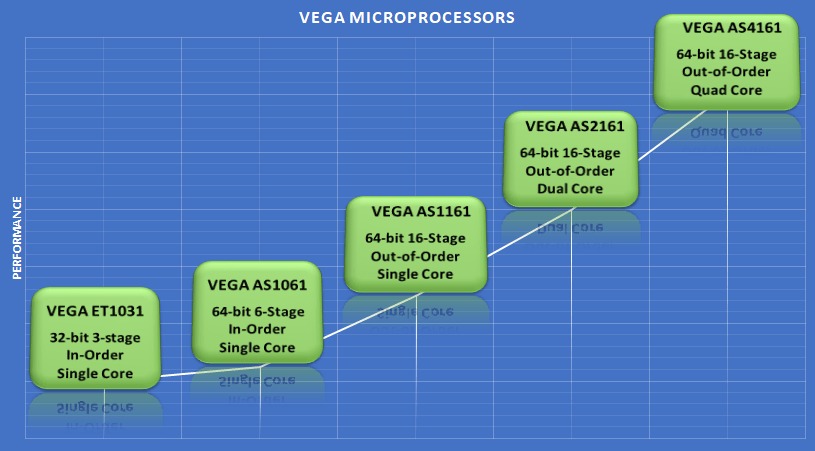

Индия переходит на архитектуру RISC-V с процессорами VEGA

Одно из основных преимуществ архитектуры RISC-V заключается в том, что она открыта, поэтому любая организация с нужными навыками может разрабатывать свои собственные ядра, и правительство Индии воспользовалось этой возможностью, разработав Программу развития микропроцессоров (MDP), которая помогает разрабатывать ядра VEGA RISC-V на местном уровне.

Читать далее «Индия переходит на архитектуру RISC-V с процессорами VEGA»