В настоящее время в виртуальном мире проходит RISC-V Summit 2020, и RISC-V International, некоммерческая корпорация, стремящаяся стимулировать принятие и внедрение архитектуры набора команд RISC-V (ISA), воспользовалась случаем, чтобы напомнить нам о росте ISA в плане коммерческой адаптации, обучения и других проектов.

Калиста Редмонд (Calista Redmond), генеральный директор RISC-V International, подробно рассказала о росте членства:

В этом году наше техническое сообщество выросло на 66 процентов до более чем 2300 человек в наших более чем 50 технических и специальных группах. Мы наблюдаем растущую динамику рынка ядер RISC-V, SoC, плат для разработчиков, программного обеспечения и инструментов для различных вычислений, от встроенных до корпоративных.

…

Мы гордимся тем, что количество наших членов во всем мире увеличилось более чем вдвое за последний год до 1000 человек, включая 222 организации ».

RISC-V также запустил RISC-V Exchange, который теперь включает более 124 ядер RISC-V, SoC и плат для разработчиков, а также 129 программных приложений и инструментов RISC-V.

Ядра RISC-V запущенные в 2020 году

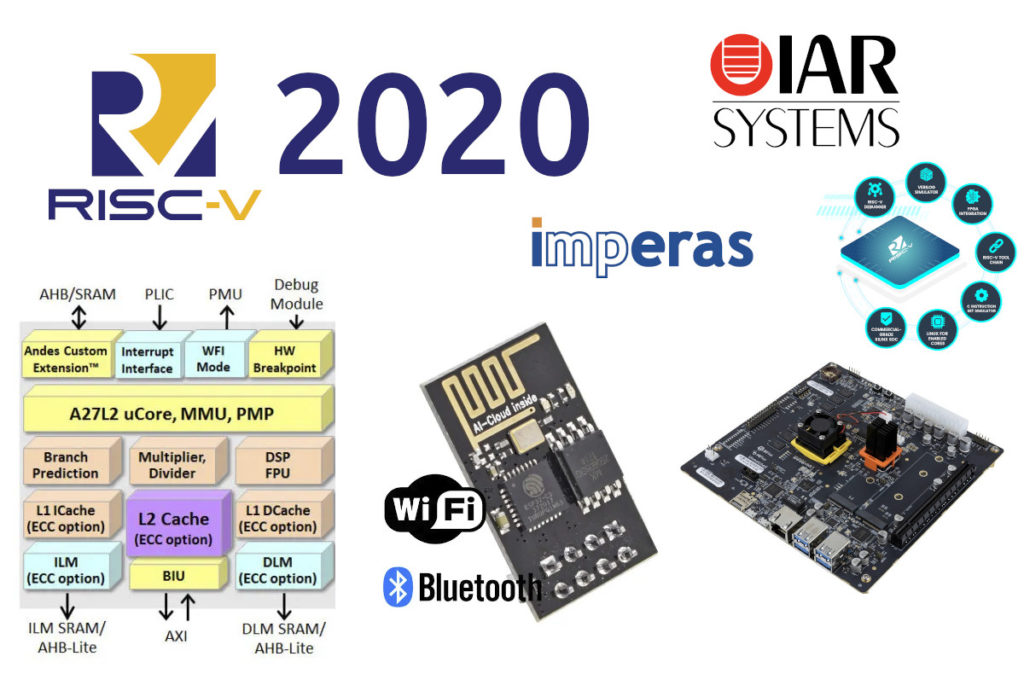

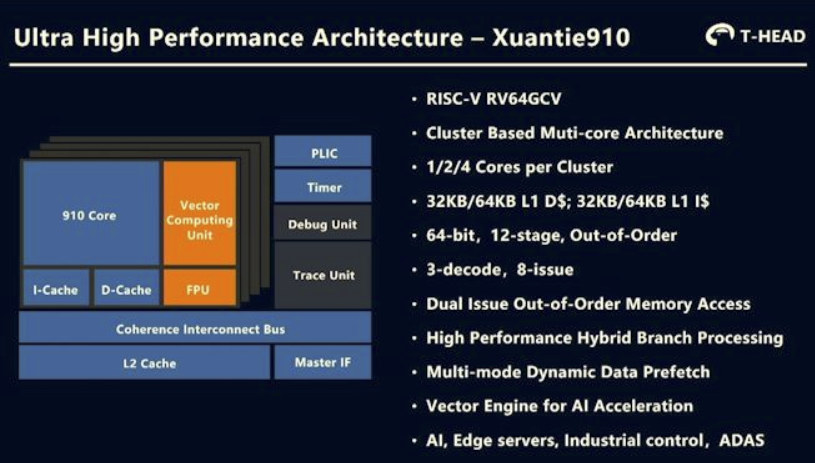

Слишком много ядер RISC-V, чтобы перечислить их все здесь, остановимся на некоторых из наиболее заметных анонсов – 64-разрядное ядро RISC-V Alibaba XT910, компания Andes добавила кеш-памяти второго уровня в его 32-разрядные и 64-разрядные RISC- V-ядра, а также многоядерная поддержка семейства 45-й серии. Если мы не ошибаемся, SiFive не выпускала новые ядра в 2020 году, но выпуск SiFive Core IP 20G1 улучшил существующие ядра RISC-V компании за счет улучшения производительности, повышения эффективности и уменьшения занимаемой площади.

Одна из замечательных особенностей RISC-V заключается в том, что он открыт, поэтому он отлично подходит для студентов, которые могут создавать программные ядра RISC-V, работающие на платформах FPGA, и в этом году Университет Китайской академии наук (UCAS) разработал NutShell, 64-разрядный SoC, который работает на частоте до 200 МГц и может работать под управлением Linux. RISC-V international мог бы даже продвигать RISC-V ISA как подходящий для 13-летних детей, поскольку молодой Николас Шарки участвовал в семинаре и сумел создать собственное ядро RISC-V …

Объявления 2020 RISC-V SoC

Ядра хороши, но для практических приложений их нужно интегрировать в микросхемы или модули. В 2020 году произошло несколько интересных событий, особенно в области микроконтроллеров.

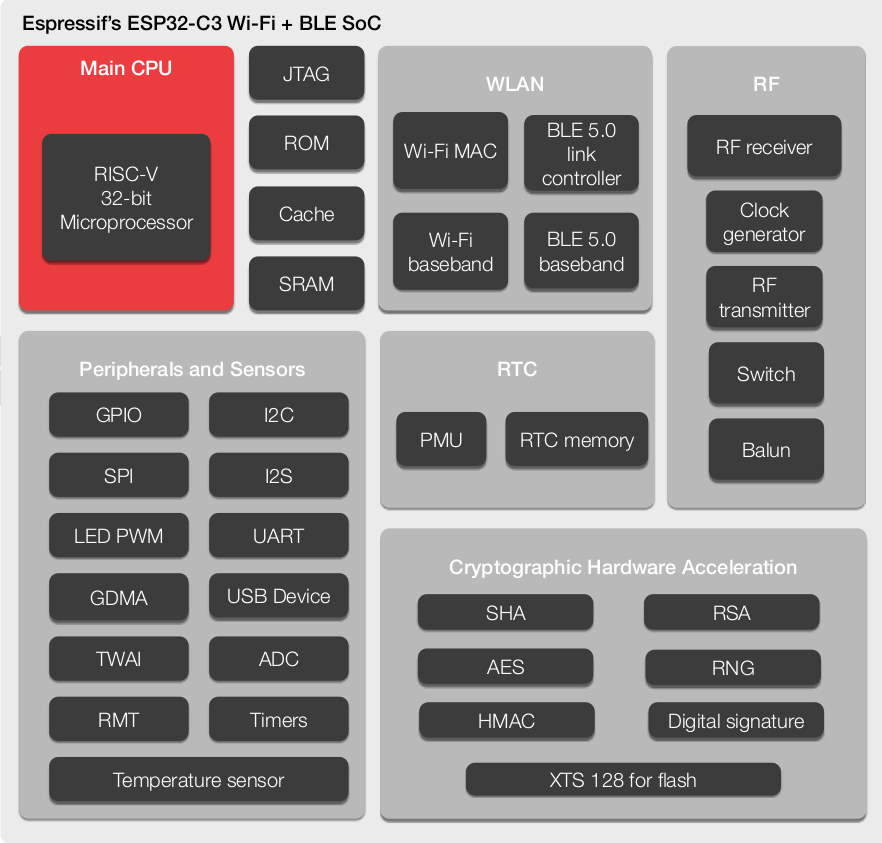

Хотя устройство было объявлено в самом конце 2019 года, мы добавим многоядерный процессор AIoT RISC-V Greenwaves GAP9 в наш список SoC 2020 года, поскольку он стал доступен только в этом году. Затем zGlue и Antimicro представили ASIC на основе чиплета GEM2 с жестким ядром RISC-V и FPGA Lattice iCE40. Но самые интересные анонсы, или, по крайней мере, те, которые вызвали наибольший ажиотаж, произошли во второй половине года, когда сначала BL602 / BL604 RISC-V WiFi и BLE SoC обещали конкурировать по цене с ESP8266, затем Allwinner работал над процессор RISC-V на базе Xuantie C906 с поддержкой Linux, и, наконец, Espressif представляет собственный чип RISC-V WiFi и BLE IoT с ESP32-C3.

Платы для разработки RISC-V и SBC

У нас также было довольно захватывающее объявление на передней панели RISC-V SBC с кампанией по сбору средств для платы Polarfire SoC Icicle RISC-V + FPGA, которая началась в июле, а затем, в августе, компания Sipeed запустила аккуратный, полностью интегрированный портативный комплект разработчика RISC-V AI MAIX Amigo. Затем появились новости об альтернативе Raspberry Pi – Picorio RISC-V, хотя это долгосрочный проект, поэтому может пройти некоторое время, прежде чем он станет доступным.

Инструменты разработки программного обеспечения RISC-V

Большинство людей, вероятно, используют инструментальную цепочку GNU для создания проектов для целей RISC-V, но некоторые коммерческие инструменты добавили поддержку открытого ISA, включая IAR Embedded Workbench, добавив поддержку GigaDevice Semiconductor RISC-V MCU (например, GD32V) и расширенную трассировку для Приложения на основе RISC-V в сотрудничестве с SiFive.

Очевидный выбор для людей, которые хотят экспериментировать без оборудования, – использовать эмулятор QEMU, поддерживающий RISC-V, но для профессионалов, которым могут потребоваться более продвинутые функции и производительность, Imperas OVPsim может быть лучшим вариантом, и, в феврале этого года, компания добавила первую эталонную модель с Инкапсуляция UVM для проверки RISC-V.

Поскольку RISC-V ISA является открытым, существует довольно большое количество ядер, что позволяет сделать выбор, прежде чем начинать разработку, и, подобрать лучшее для вашего приложения, Bluespec выпустила RISC-V Explorer, бесплатный инструмент для оценки и сравнения ядер RISC-V.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.