Процессоры Armv8 и Armv8-M поддерживают безопасность Arm TrustZone, направленную на предотвращение программных атак на целевое устройство. Однако, если у хакера есть физический доступ к аппаратному обеспечению, этого может быть недостаточно для предотвращения взлома.

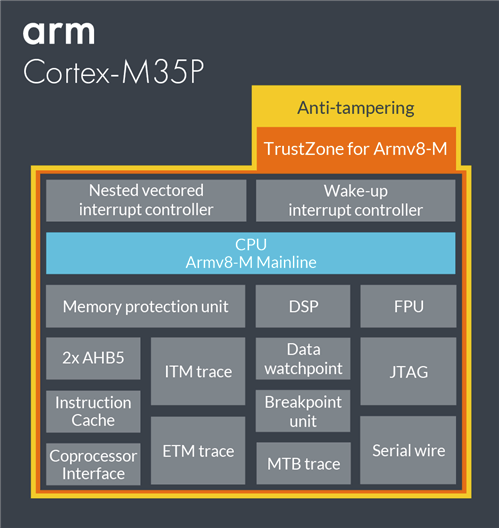

Ядро Arm Cortex-M35P решает эту проблему, предоставляя физическую (отсюда «P» в названии) безопасность с функциями защиты от несанкционированного доступа, защищающую от доступа даже при прямом обращении к аппаратным средствам.

Основные характеристики процессора:

- Архитектура — Armv8-M Mainline (Harvard)

- Поддержка ISA — Thumb/Thumb-2

- Канал — трехступенчатый

- Защита программного обеспечения — опция TrustZone для Armv8-M, проверка стека

- Физическая защита — встроенная защита от инвазивных и неинвазивных атак

- DSP расширения

- дополнительные инструкции DSP/SIMD

- 16/32-бит MAC за один цикл

- Два 16-бит MAC за один цикл

- 8/16-битная SIMD-арифметика

- Блок с плавающей точкой — дополнительный блок с плавающей точкой с одиночной точностью, совместимый с IEEE 754

- Сопроцессорный интерфейс — дополнительный специализированный интерфейс сопроцессора, подключенный к шинам для 8 процессорных блоков для пользовательских вычислений

- Защита памяти — дополнительный модуль защиты памяти (MPU) с 16 зонами для обеспечения безопасности

- Прерывания — немаскируемые прерывания (NMI) и до 480 физических прерываний от 8 до 256 приоритетными уровнями

- Wake-up Interrupt Controller — дополнительно для пробуждения процессора при «спящем режиме» или когда все часы остановлены

- Режимы сна — интегрированная функция пробуждения когда возникает событие(WFE) и пробуждения когда возникает прерывание (WFI) с функцией «Спящий режим»

- Отладка — дополнительные порты отладки JTAG и Serial Wire. До 8 точек прерывания и 4 точек наблюдения

- Трассировка — выборочная трассировка инструкций (ETM), буфер Micro Trace (MTB), трассировка данных (DWT) и контрольная диаграмма (ITM)

- Кэш — кэш команд. Настраиваемая четность кэш для создания ECC (код исправления ошибок) для приложений безопасности.

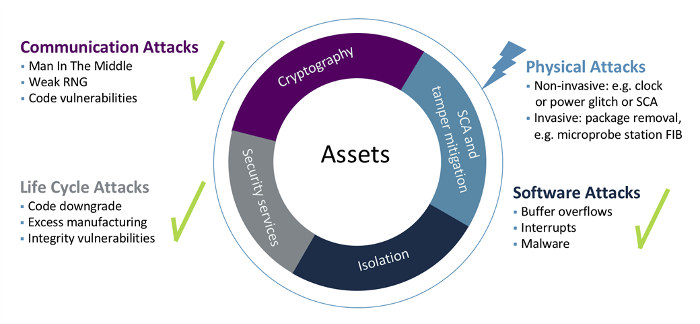

Четыре типа атак

Физическая защита достигается благодаря нескольким функциям безопасности, включая:

- Равномерное время для выполнения команд в постоянном количестве циклов во избежание утечки информации

- 100% -ый охват четности с каждым флопом в процессоре защищен с помощью настраиваемой четности для обнаружения случайных ошибок и/или введенных ошибок.

Вряд ли «умная лампочка» будет обладать такой физической безопасностью, а Arm Cortex M35P — и другой процессор серии «P» от Microsoft — скорее всего, будет использоваться в высокоценных приложениях, таких как платежные терминалы, жизнеобеспечивающие медицинские устройства и автомобильные приложения.

Более подробную информацию вы найдете на странице продукта Arm Cortex M35P и в блоге в сообществе Arm Community. Если вы заинтересованы узнать больше о безопасности устройств с устройствами Arm в целом, вы можете проверить страницу ресурсов Arm Platform Security Architecture (PSA).

Благодарим сайт cnx-software.com за предоставленную информацию.

Оригинал статьи опубликован здесь