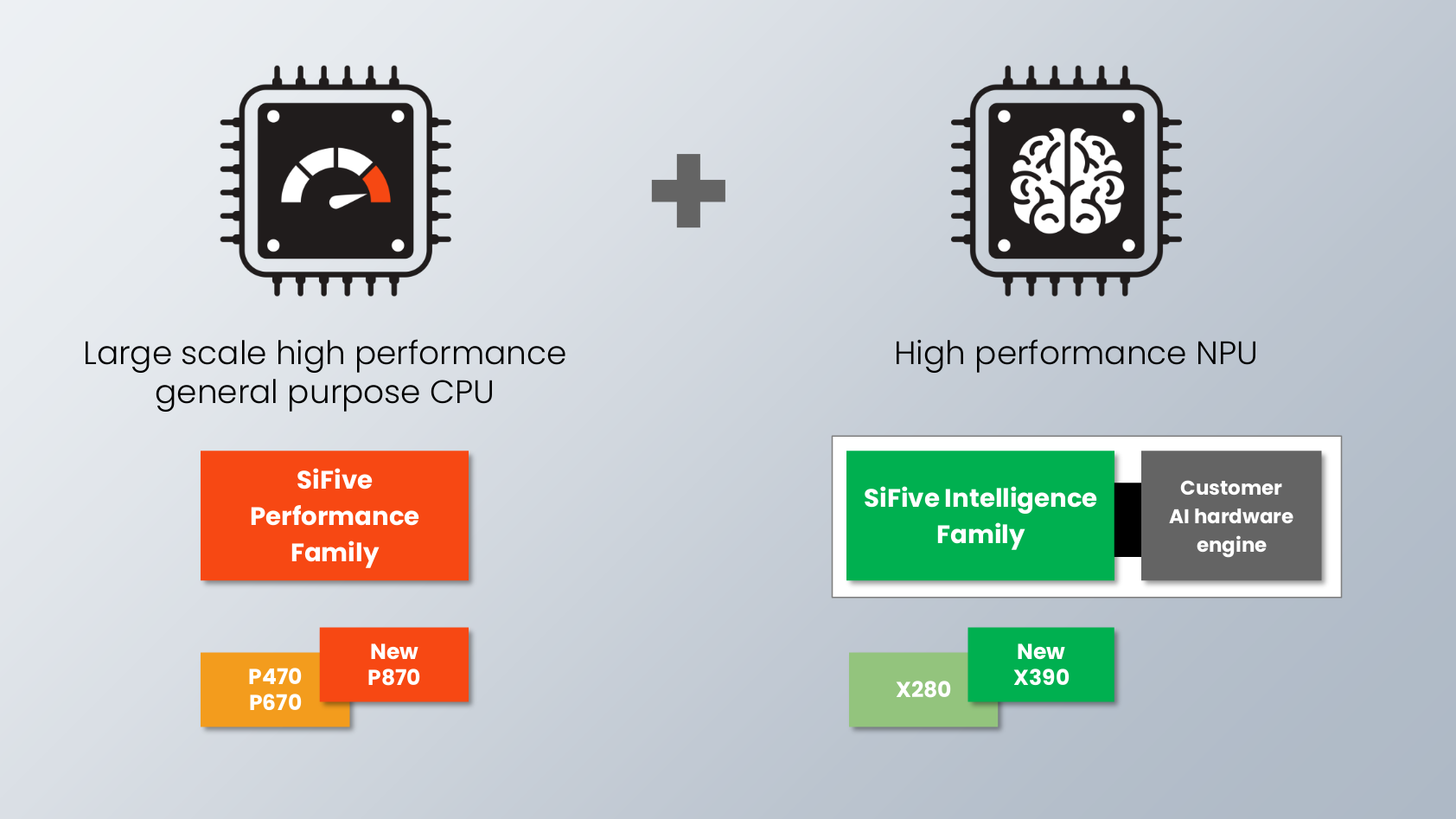

SiFive анонсировала два новых высокопроизводительных IP-блока с NPU Intelligence X390 и ядром Performance P870 RISC-V, которые должны найти свое применение в процессоре, предназначенном для приложений генеративного искусственного интеллекта и машинного обучения.

Читать далее «SiFive анонсирует NPU Intelligent X390 и ядро Performance P870 RISC-V»Недорогая USB-плата разработки CH32V003 с микроконтроллером RISC-V

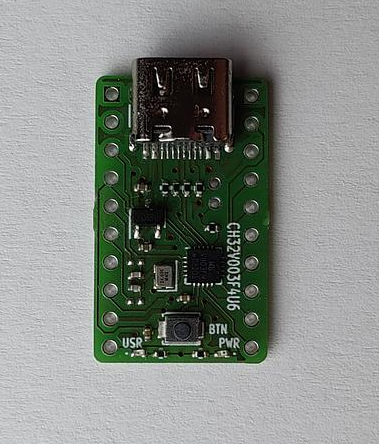

LECTRONZ недавно представила один из своих последних продуктов под названием USB-плата разработки CH32V003, предназначенная для предоставления разработчикам и энтузиастам универсальной и компактной платформы для экспериментов с микроконтроллерами RISC-V.

Как следует из названия, в основе этой платы лежит экономичный микроконтроллер CH32V003F4U6 от WCH с тактовой частотой до 48 МГц, 16 КБ флэш-памяти и 2 КБ оперативной памяти.

Читать далее «Недорогая USB-плата разработки CH32V003 с микроконтроллером RISC-V»OpenWrt 23.05 выпущен с MbedTLS по умолчанию, пакетами Rust, поддерживающая более 1790 устройств

На днях была выпущена операционная система Linux с открытым исходным кодом OpenWrt 23.05 для маршрутизаторов и безголовых встраиваемых систем с ограниченными ресурсами, с момента выпуска OpenWrt 22.03 чуть больше года назад с более чем 4300 коммитами.

Новая версия теперь поддерживает более 1790 устройств или около 200 новых устройств по сравнению с версией OpenWrt 22.03 с заметными новыми целями, включая цель ipq807x для Qualcomm IPQ807x WiFi 6 SoC, подцель mediatek/filogic для Mediatek Filogic 830 и 630 SoC, и цель sifiveu для плат разработки HiFive Unleashed и Unmatched RISC-V.

Плата MCU RISC-V начального уровня с поддержкой Wi-Fi6, BLE 5.0 и Zigbee

Waveshare представила ESP32-C6-DEV-KIT-N8, универсальную плату для разработки, оснащенную беспроводными возможностями Wi-Fi 6, Bluetooth 5 и IEEE 802.15.4 (Zigbee 3.0 и Thread). Эта плата имеет 23х контакта GPIO, порт USB Type-C и совместимость со средой разработки ESP-IDF для различных проектов Интернета вещей.

Читать далее «Плата MCU RISC-V начального уровня с поддержкой Wi-Fi6, BLE 5.0 и Zigbee»Преобразователь Ollie v2 USB в UART/CAN/RS485/RS232 получил порт USB-C, пластиковый корпус и многое другое (краудфандинг)

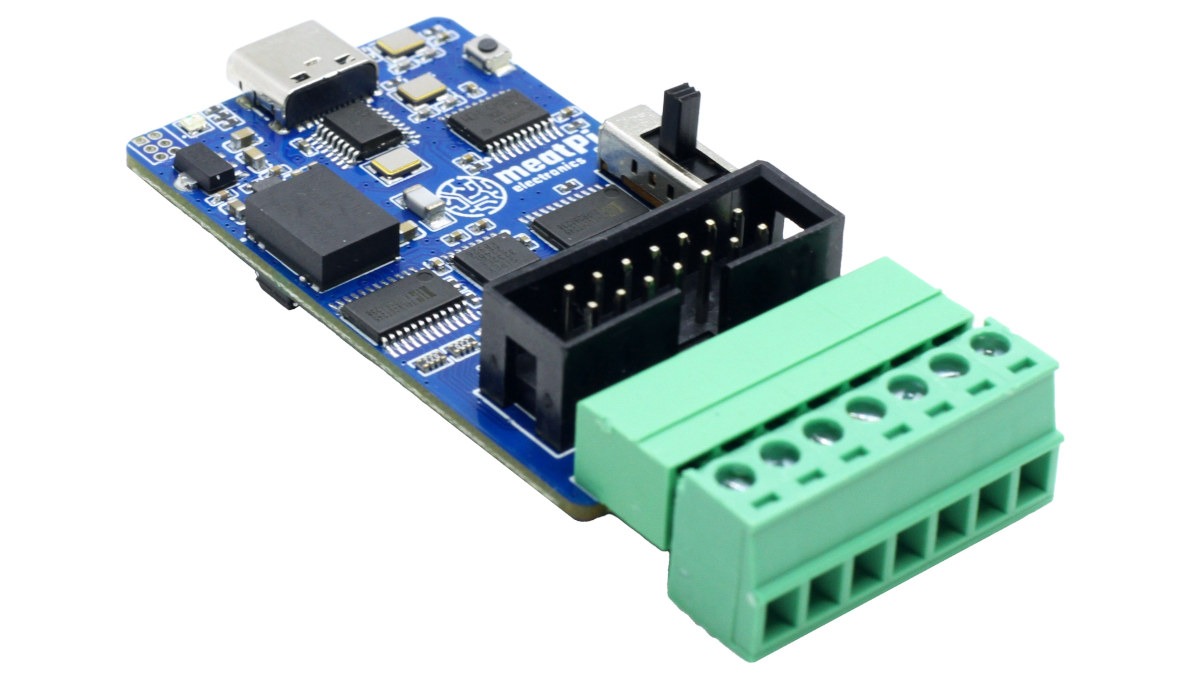

Ollie v2 — это улучшенная версия преобразователя Ollie USB в изолированный UART, CAN Bus, RS232 и RS485, который имеет порт USB-C, пластиковый корпус, возможность устанавливать напряжение с целевой платы и различные другие незначительные улучшения.

Читать далее «Преобразователь Ollie v2 USB в UART/CAN/RS485/RS232 получил порт USB-C, пластиковый корпус и многое другое (краудфандинг)»Sipeed представляет док-станцию Tang Mega 138K Pro Dock

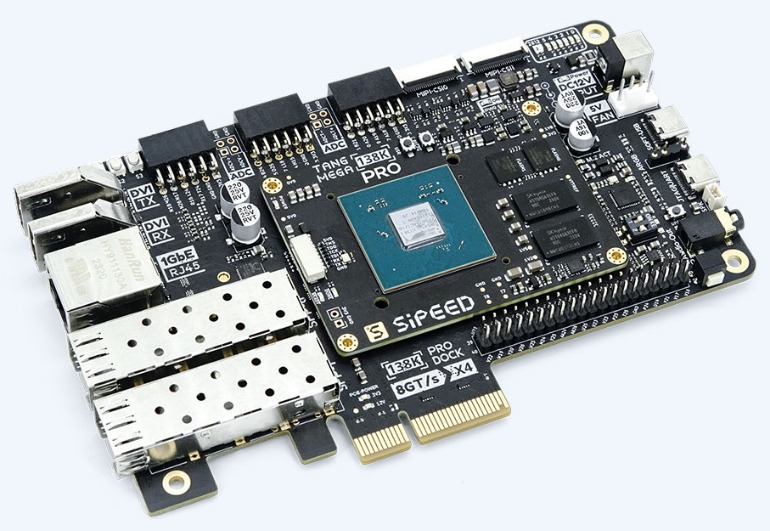

Сегодня компания Sipeed выпустила новую плату для разработки серии Tang, оснащенную мощной GOWIN GW5AST RISC-V FPGA. Эта универсальная плата предлагает ряд гибких функций, включая порт GbE, два интерфейса DVI, 8х портов Serdes 12,5 Гбит/с и множество других периферийных устройств.

Читать далее «Sipeed представляет док-станцию Tang Mega 138K Pro Dock»Кластерная плата Lichee Cluster 4A mini-ITX RISC-V выпущена по цене от 929 долларов США и выше

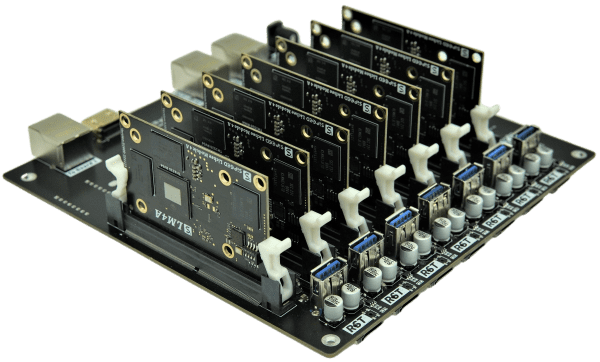

Как и ожидалось, Sipeed выпустила кластерную плату Lichee Cluster 4A mini-ITX и блок, вмещающий до семи модулей RISC-V, по цене от 929 долларов на Aliexpress.

Все предлагаемые комплекты оснащены семью системными модулями Sipeed LM4A на базе четырехъядерного процессора RISC-V T-Head TH1520 с конфигурацией памяти и хранилища 8 ГБ/32 ГБ или 16 ГБ/128 ГБ.

Читать далее «Кластерная плата Lichee Cluster 4A mini-ITX RISC-V выпущена по цене от 929 долларов США и выше»Andes выпускает процессорное ядро AX45MPV RISC-V с векторным расширением 1.0

Недавно компания Andes Technology объявила о выпуске процессора AndesCore AX45MPV RISC-V, который создан на основе многоядерного процессора AX45MP и дополнен векторным расширением RISC-V 1.0.

Новое ядро ЦП RISC-V, оснащенное векторной обработкой RISC-V и возможностью параллельного выполнения, предназначено для SoC, обрабатывающего большие объемы данных для таких приложений, как ADAS, вывод и обучение искусственного интеллекта, AR/VR, мультимедиа, робототехника и обработка сигналов.

Читать далее «Andes выпускает процессорное ядро AX45MPV RISC-V с векторным расширением 1.0»