Компания Signaloid, специализирующаяся на оборудовании и облачных вычислениях, базирующаяся в Кембридже, запустила краудфандинговую компанию для C0-microSD — крошечной программируемой системы-на-модуле (SoM) iCE40UP5K FPGA в форм-факторе карты microSD. Она поставляется с предустановленным программным ядром RISC-V, и пользователи также могут загружать на плату собственные проекты FPGA.

Читать далее «Signaloid C0-microSD — это iCE40UP5K FPGA SoM в форм-факторе карты microSD (Crowdfunding)»Семейство FPGA AMD Versal Premium Gen2 SoC включает ядра Arm Cortex-A72/R5F, высокопроизводительную матрицу FPGA, интерфейсы PCIe Gen6 и CXL 3.1

FPGA AMD Versal Premium Series Gen 2 SoC объединяет процессоры с двумя ядрами Cortex-A72 и процессоры с двумя ядрами Cortex-R5F с высокопроизводительной матрицей FPGA, содержащей до 3,2 млн логических ячеек и интерфейсами CXL 3.1 (Compute Express Link), PCIe Gen6 и DDR5/LPDDR5X с высокой пропускной способностью для центров обработки данных, коммуникационного оборудования, испытательных и измерительных приложений, а также приложений с интенсивным использованием данных в аэрокосмической и оборонной промышленности.

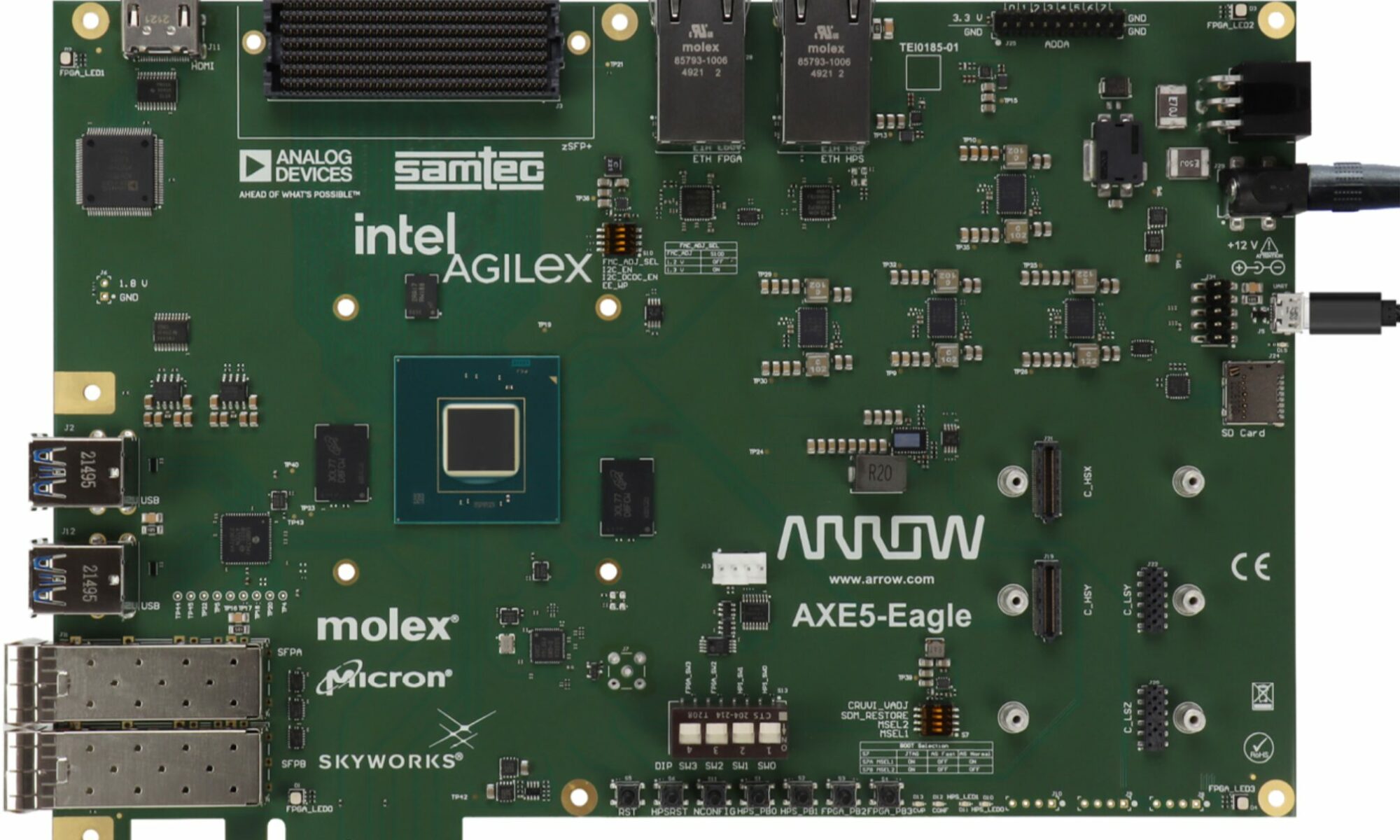

Читать далее «Семейство FPGA AMD Versal Premium Gen2 SoC включает ядра Arm Cortex-A72/R5F, высокопроизводительную матрицу FPGA, интерфейсы PCIe Gen6 и CXL 3.1»Комплект разработчика Trenz Electronic AXE5-EAGLE-ES оснащен 5 E-Series SoC FPGA

Комплект разработчика Trenz Electronic AXE5-EAGLE-ES работает на базе FPGA Intel Agilex 5 E-series SoC под кодовым названием Sundance Mesa. Он разработан для приложений FPGA в таких секторах, как беспроводная связь, видеотрансляция и защита. Комплект содержит 656k логических элементов и четырехъядерную систему обработки с двухъядерными кластерами Arm Cortex-A76 и Cortex-A55. Он поддерживает высокоскоростные приемопередатчики до 17 Гбит/с, подключение PCIe 4.0 и интегрированные интерфейсы памяти, такие как DDR4 и LPDDR4/5.

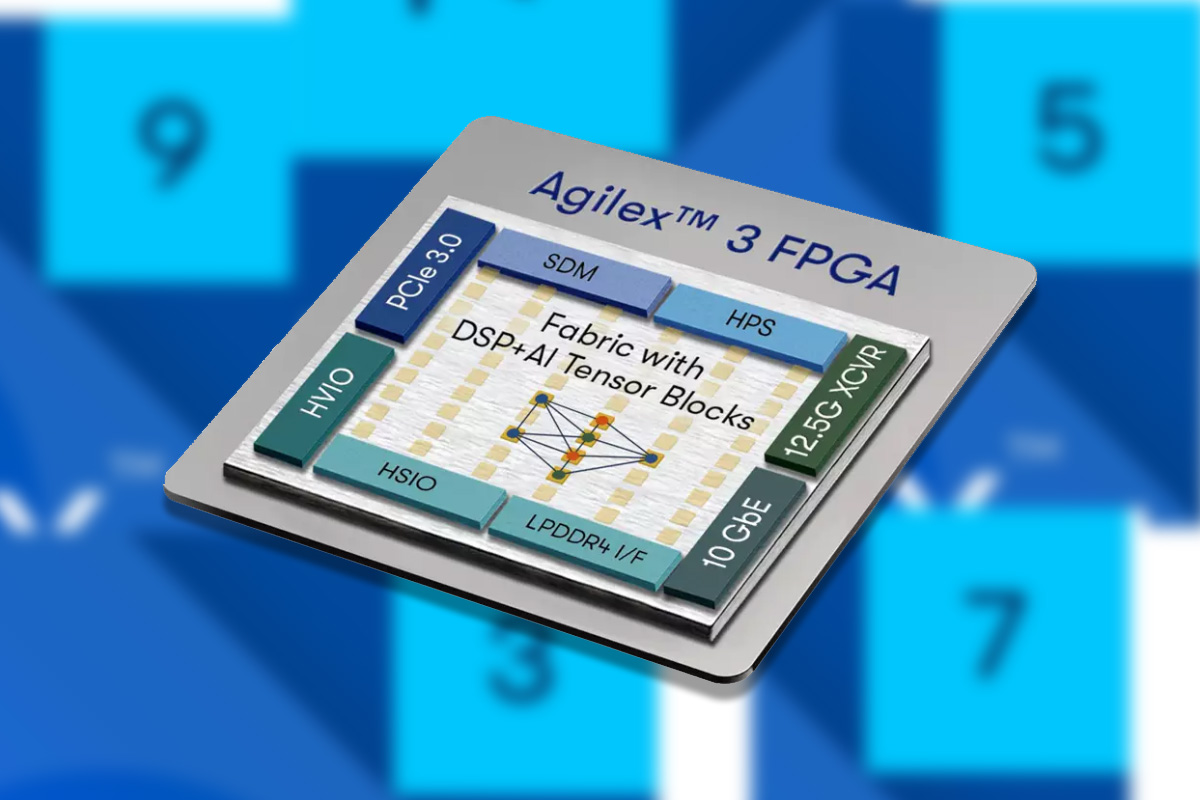

Читать далее «Комплект разработчика Trenz Electronic AXE5-EAGLE-ES оснащен 5 E-Series SoC FPGA»7-нм SoC FPGA Agilex 3 от Altera оснащена ядрами Cortex-A55, блоком AI Tensor, DSP, 10 GbE и другими функциями.

Altera, независимая дочерняя компания Intel, выпустила линейку Altera Agilex 3 SoC FPGA, созданную на основе 7-нм технологии Intel. По словам Altera, эти FPGA отдают приоритет стоимости и энергоэффективности, сохраняя при этом необходимую производительность.

Читать далее «7-нм SoC FPGA Agilex 3 от Altera оснащена ядрами Cortex-A55, блоком AI Tensor, DSP, 10 GbE и другими функциями.»ThunderScope — осциллограф с открытым исходным кодом Thunderbolt и PCIe, с частотой дискретизации данных 1 Гвыб/с (краудфандинг)

ThunderScope — это осциллограф с открытым исходным кодом, Thunderbolt/USB4 и PCIe, с частотой дискретизации до 1 Гвыб/с. Устройство портативное и представляет собой доступную альтернативу дорогостоящим настольным осциллографам с открытым исходным кодом и обеспечивает более высокую частоту дискретизации, чем большинство USB-осциллографов.

Читать далее «ThunderScope — осциллограф с открытым исходным кодом Thunderbolt и PCIe, с частотой дискретизации данных 1 Гвыб/с (краудфандинг)»Efinix представила энергоэффективное семейство SoC FPGA Topaz RISC-V для «крупносерийных применений массового рынка»

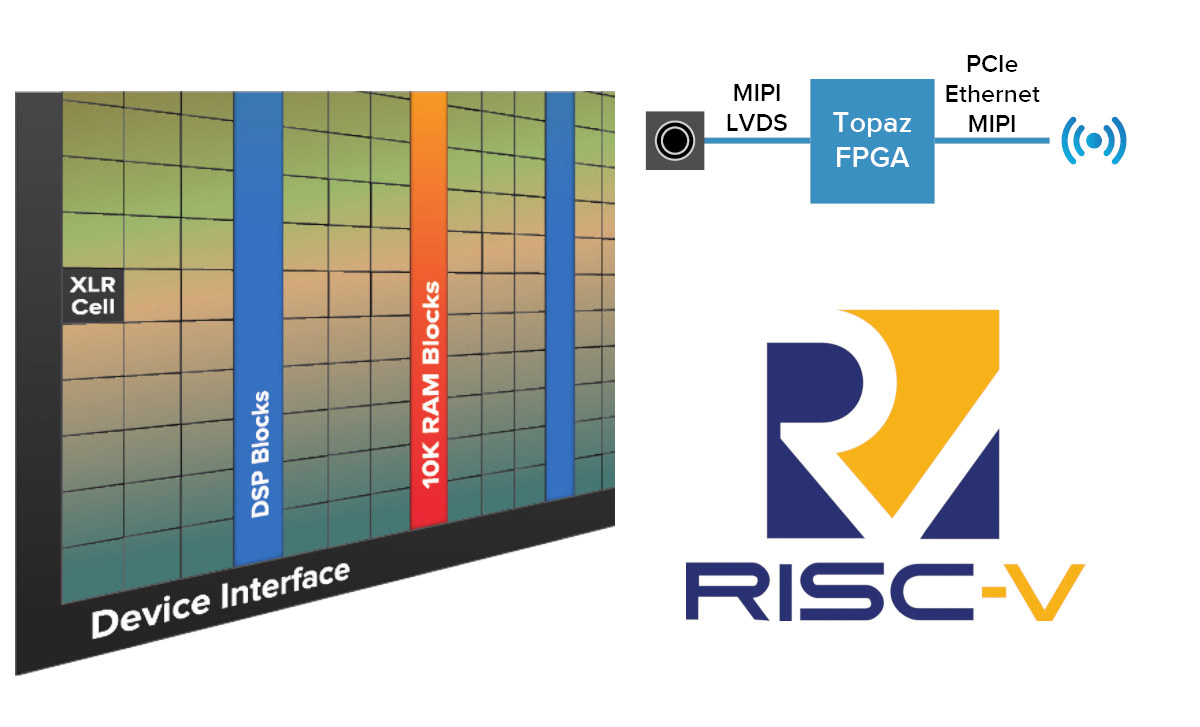

Efinix Topaz — новое энергоэффективное семейство SoC ПЛИС RISC-V, производимое по той же 16-нм технологии TSMC, что и Efinix Titanium SoC FPGA , но оптимизированное для высокой производительности при малом энергопотреблении и ориентированное на высокообъемные массовые приложения.

SoC ПЛИС Topaz предоставляют меньше функций, чем семейство Titanium, но все же предлагают до четырех аппаратных ядер RISC-V, PCIe Gen3, интерфейсы MIPI, LPDDR4, LVDS и передатчики до 12.5 Гбит/с, при этом большинство функций являются опциональными и зависят от выбранных SKU.

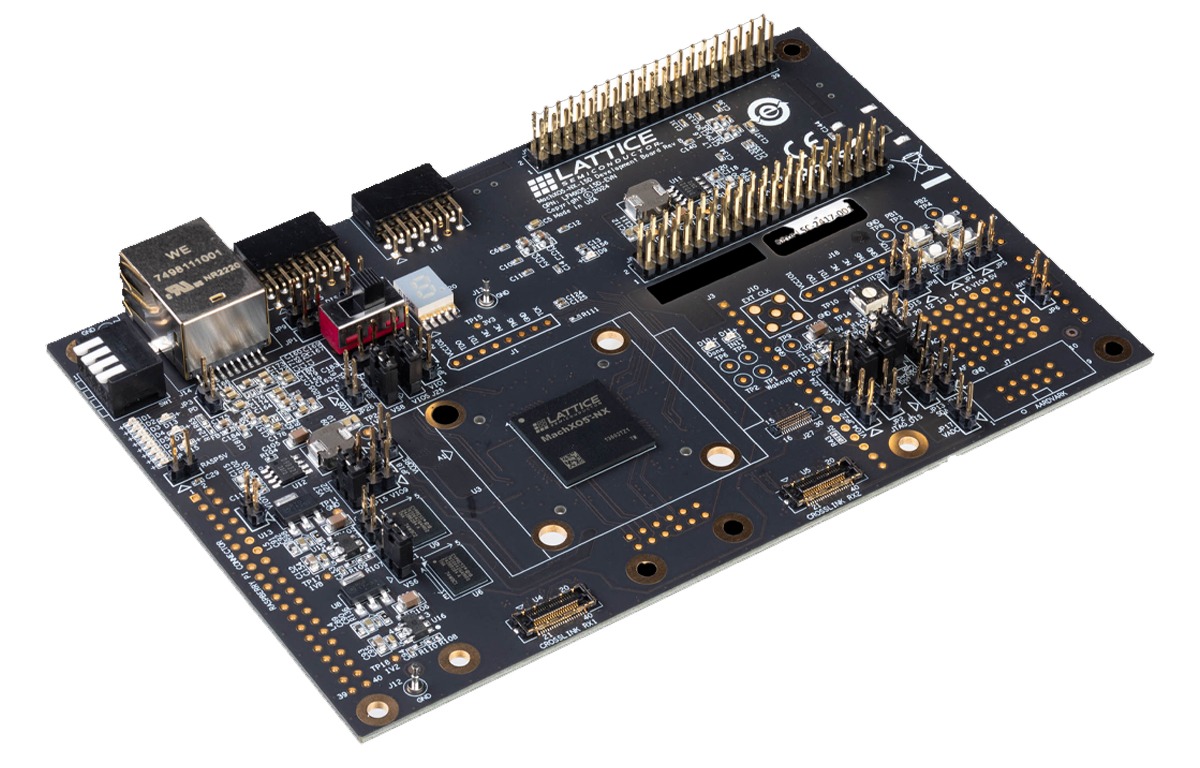

Семейство Lattice MachXO5D-NX FPGA обеспечивает аппаратную безопасность в программируемых FPGA

Lattice Semiconductor недавно представила семейство FPGA MachXO5D-NX, которое интегрирует аппаратный корень доверия (RoT) в маломощные FPGA. Это решает проблемы безопасности, объединяя встроенную флэш-память и аппаратное шифрование для минимизации рисков захвата кода во время загрузки.

Читать далее «Семейство Lattice MachXO5D-NX FPGA обеспечивает аппаратную безопасность в программируемых FPGA»Компактные и маломощные Certus-NX-09 и Certus-NX-28 FPGA Lattice Semi оснащены дополнительным интерфейсом PCIe Gen2

Компания Lattice Semiconductor добавила два новых устройства в свое маломощное семейство FPGA Lattice Certus-NX, а именно Certus-NX-28 и Certus-NX-09, доступные в нескольких корпусах и предназначенные для коммуникационных, вычислительных, промышленных и автомобильных приложений.

Читать далее «Компактные и маломощные Certus-NX-09 и Certus-NX-28 FPGA Lattice Semi оснащены дополнительным интерфейсом PCIe Gen2»