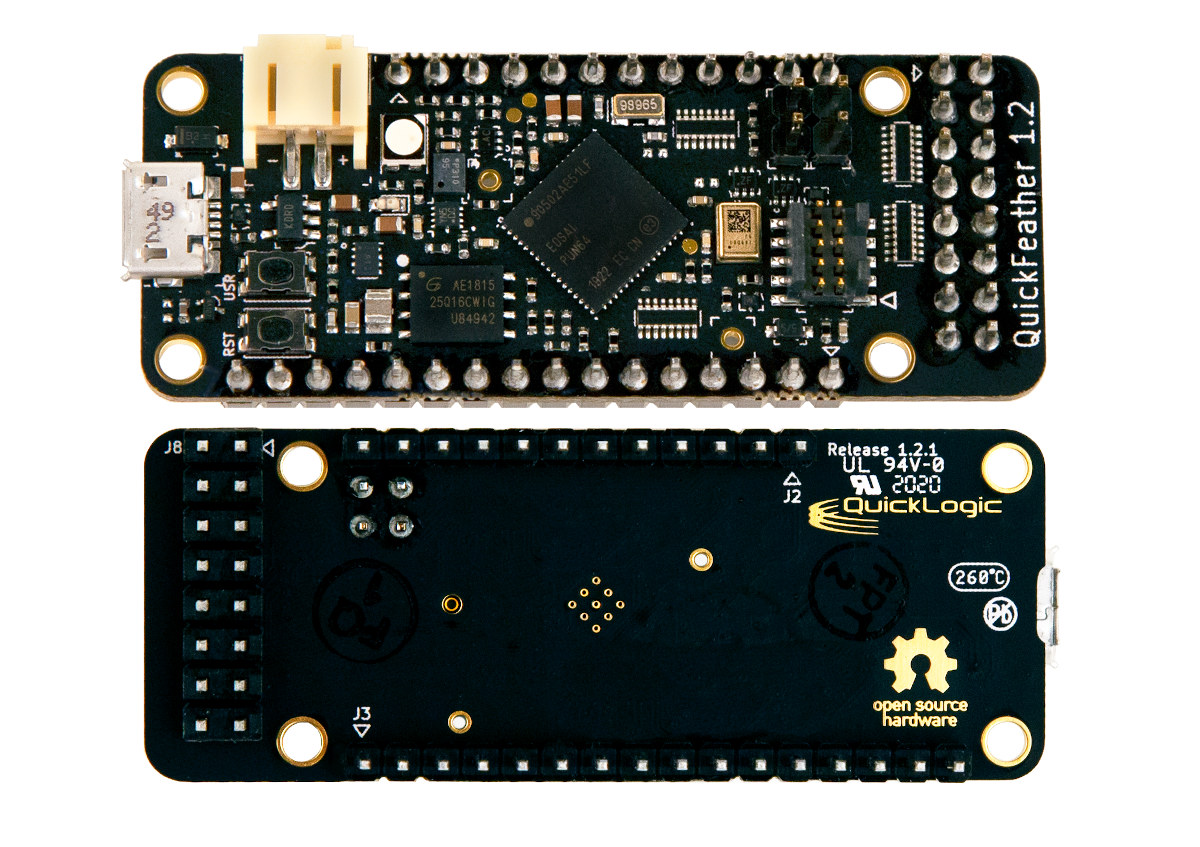

Хотя сегодня встречается все больше плат разработчика на FPGA, лишь немногие из них предназначены для установки в макетную плату. Ранее уже рассматривались TinyFPGA BX , Fipsy и QuickFeather — FPGA-платы, совместимые с макетными платами.

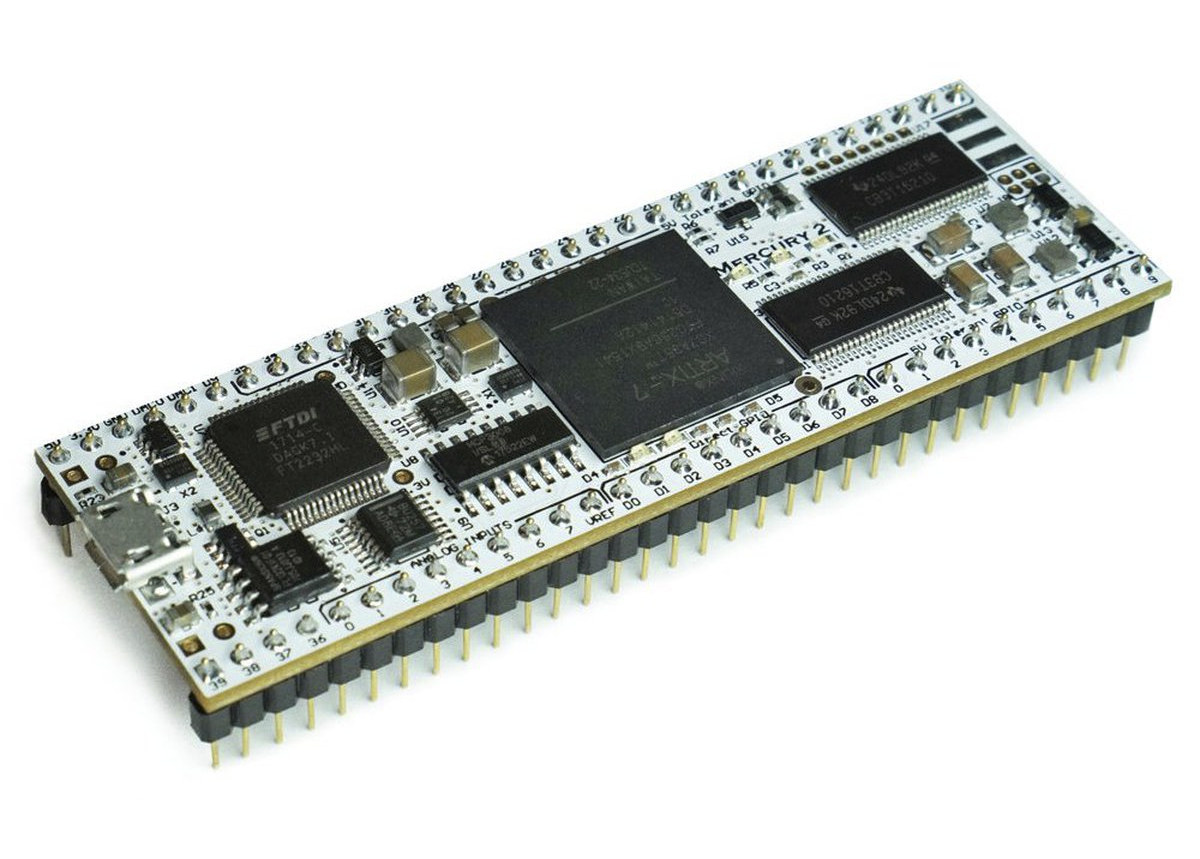

Однако все эти платы основаны на FPGA начального уровня, таких как Lattice Semi ICE40 или QuickLogic EOS S3. Если требуется более мощная FPGA-плата, совместимая с макетной платой, то плата разработчика MicroNova Mercury 2 с Xilinx Artix-7 FPGA может соответствовать требованиям.