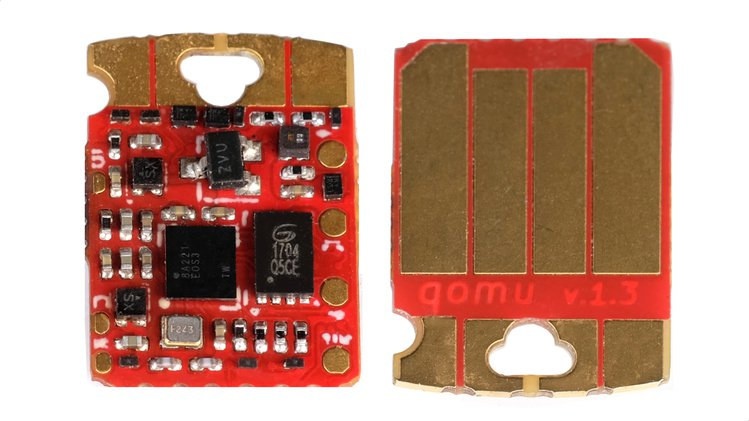

В прошлом мы видели несколько крошечных плат «omu» размером с USB-разъем, начиная с Tomu на базе Silabs EFM32 Arm-Cortex-M0 + MCU, затем Fomu, обеспечивающего программирование Python и RISC-V на Lattice ICE40 FPGA и, наконец, ключ безопасности Somu FIDO2.

Читать далее «Плата Qomu программируется с помощью набора инструментов с открытым исходным кодом Symbiflow (краудфандинг)»Высокоскоростной интерфейс USB2IO сочетает в себе Intel Cyclone 10 FPGA и STM32H7 MCU

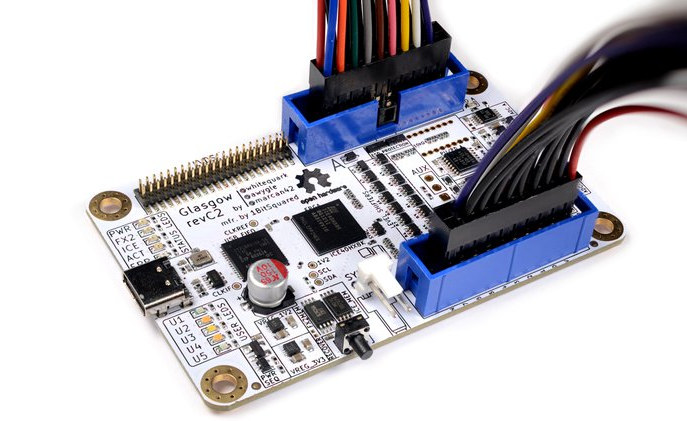

Во второй половине 2020 года мы увидели изрядное количество инструментов отладки USB для разработчиков электроники и хакеров, включая Glasgow Interface Explorer с ICE40 FPGA.

Читать далее «Высокоскоростной интерфейс USB2IO сочетает в себе Intel Cyclone 10 FPGA и STM32H7 MCU»Glasgow Interface Explorer — инструмент аппаратной отладки на базе iCE40 FPGA (краудфандинг)

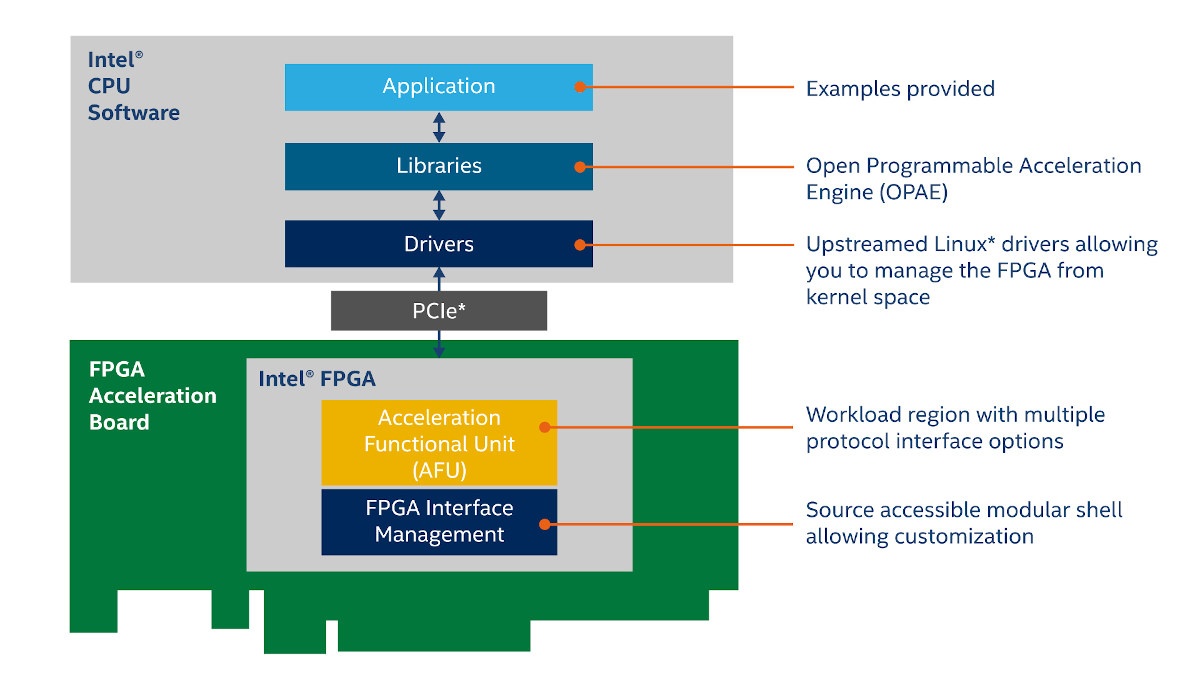

Intel представляет eASIC N5X Structured ASIC и стэк Open FPGA

Сегодня Intel проводит виртуальный день технологий FPGA 2020, и перед этим компания сделала два объявления. Во-первых, компания представила новое семейство структурированных eASIC Intel eASIC N5X с процессором, совместимым с Intel FPGA, для быстрого создания приложений для 5G, искусственного интеллекта, облачных и периферийных рабочих нагрузок.

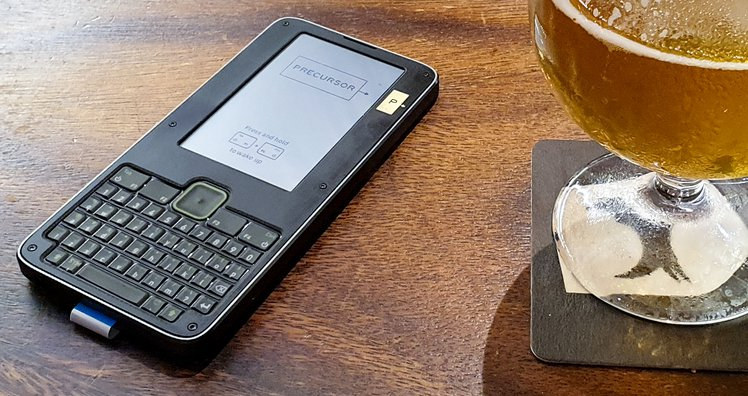

Читать далее «Intel представляет eASIC N5X Structured ASIC и стэк Open FPGA»Preursor — это открытая платформа для разработки мобильного оборудования, с двумя FPGA (краудфандинг)

Sutajio Ko-usagi PTE LTD на протяжении многих лет запускала на Crowd Supply разное интересное оборудование, включая ноутбук Novena с открытым исходным кодом и FPGA-плату Fomu, которая вставляется внутрь USB порта.

Читать далее «Preursor — это открытая платформа для разработки мобильного оборудования, с двумя FPGA (краудфандинг)»PolarBerry — это компактный SBC и модуль RISC-V FPGA с поддержкой Linux (краудфандинг)

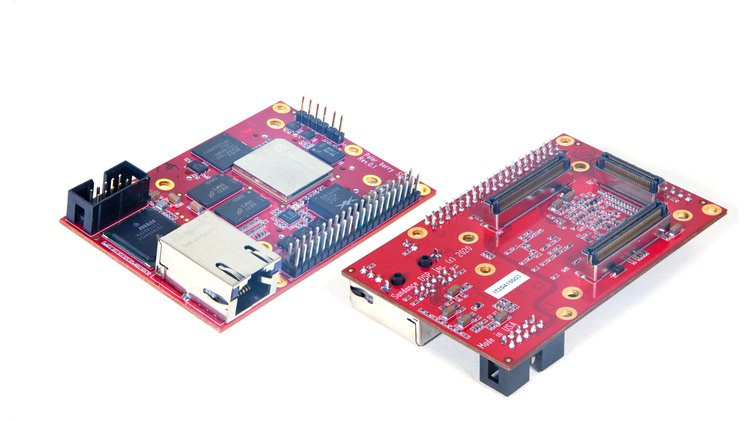

На днях компания SiFive анонсировал материнскую плату mini-ITX для ПК с RISC-V, но если вам нужна платформа RISC-V Linux в более компактном форм-факторе, Sundance PolarBerry может лучше соответствовать вашим требованиям, хотя плата будет ориентирована на другие варианты использования.

PolarBerry, работающий на базе Microchip PolarFire RISC-V SoC FPGA, представляет собой одноплатный компьютер с Gigabit Ethernet и 40-контактным разъемом GPIO, а также систему-на-модуле благодаря трем межплатным разъемам Samtec.

Читать далее «PolarBerry — это компактный SBC и модуль RISC-V FPGA с поддержкой Linux (краудфандинг)»Комплект для разработки iW-RainboW-G35D на базе MPSoC Xilinx Zynq UltraScale+ ZU19EG предлагает HDMI 2.0, 10GbE и высокоскоростные трансиверы

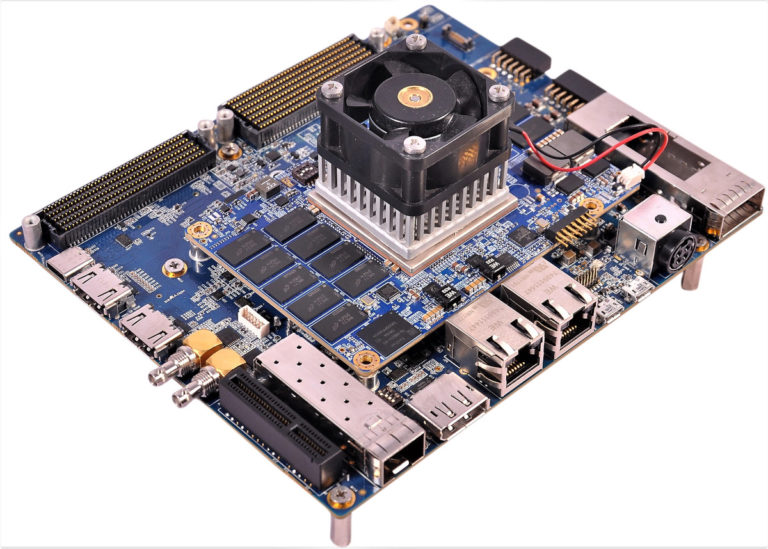

iWave Systems iW-RainboW-G35D представляет собой комплект для разработки на базе Xilinx Zynq UltraScale+ ZU19EG Arm Cortex-A53 и MPSoC FPGA в сочетании с 4 Гб оперативной памяти DDR4 с ECC для системы обработки (PS) и 4 Гб двухканальной оперативной памяти DDR4 для программируемой логики (PL).

Плата оснащена двумя портами (вход и выход) HDMI 2.0 с поддержкой разрешений 4Kp60 UHD, разъемом 10GbE SFP+, а также такими внешними интерфейсами, как FMC+, FMC, FireFly и QSFP для высокоскоростных трансиверов и многим другим. Читать далее «Комплект для разработки iW-RainboW-G35D на базе MPSoC Xilinx Zynq UltraScale+ ZU19EG предлагает HDMI 2.0, 10GbE и высокоскоростные трансиверы»

Шлюз Corazon-AI на базе FPGA поддерживает до 8 IP-камер для видеоаналитики

Ранее в этом году мы рассмотрели некоторые решения для видеоаналитики на базе встраиваемого компьютера AAEON UP Xtreme Edge, сочетающего процессор Intel Whiskey Lake с модулями AI-ускорителя Intel Movidius Myriad X, а также программные решения для управления и видеоаналитики Milestones и SAIMOS или aotu. ai BrainFrame.

iWave Systems представила аналогичное решение – шлюз Corazon-AI, способный обрабатывать до 8 IP-камер в режиме реального времени, но вместо того, чтобы полагаться на AI-ускорители, компания использует Xilinx Zynq Ultrascale + Arm Cortex-A53/R5 FPGA MPSoC для AI-вывода.

Читать далее «Шлюз Corazon-AI на базе FPGA поддерживает до 8 IP-камер для видеоаналитики»