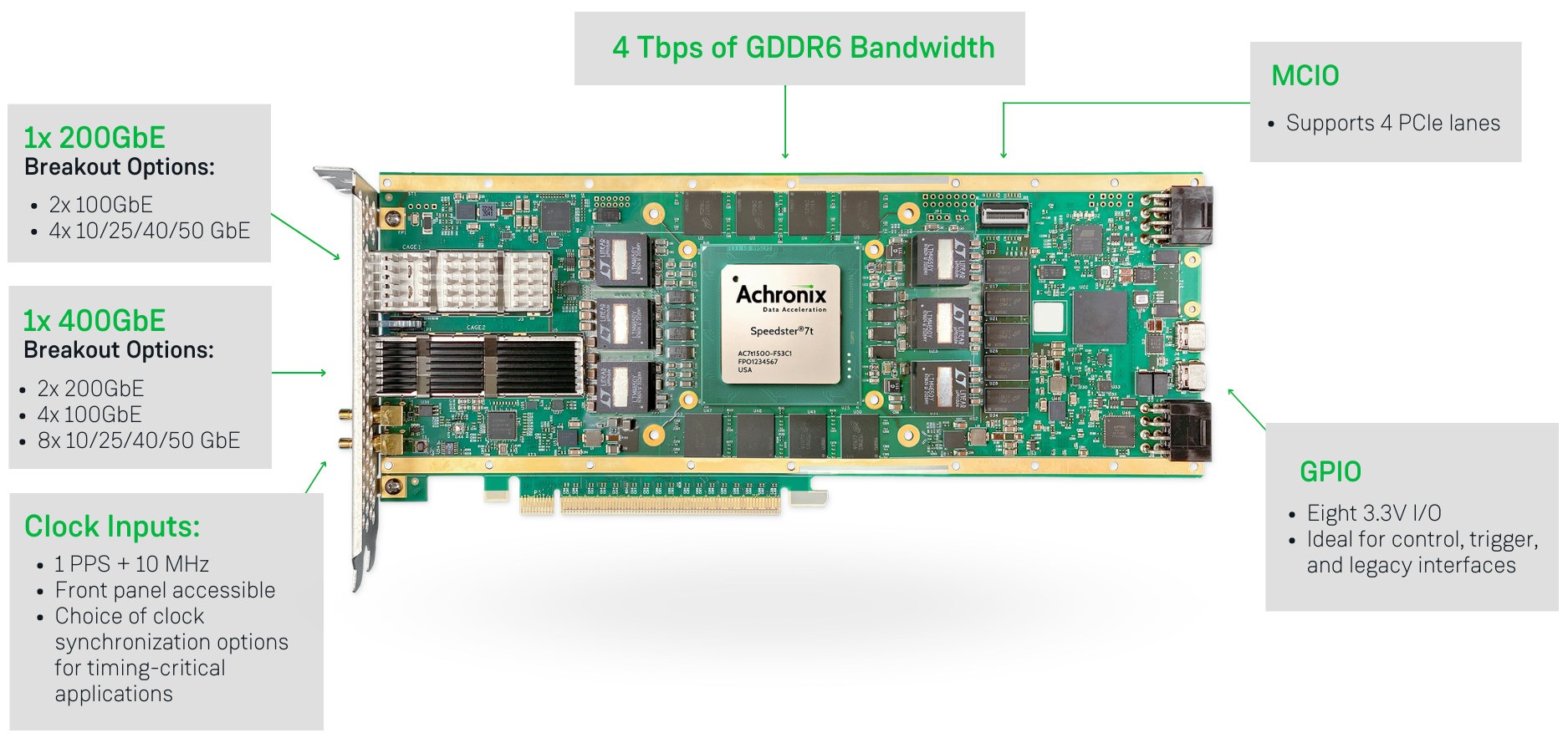

Компания Achronix Semiconductor недавно объявила об общедоступной Speedster7t AC7t1500 FPGA, предназначенной для приложений ускорения сетей, хранения и вычислений (AI/ML).

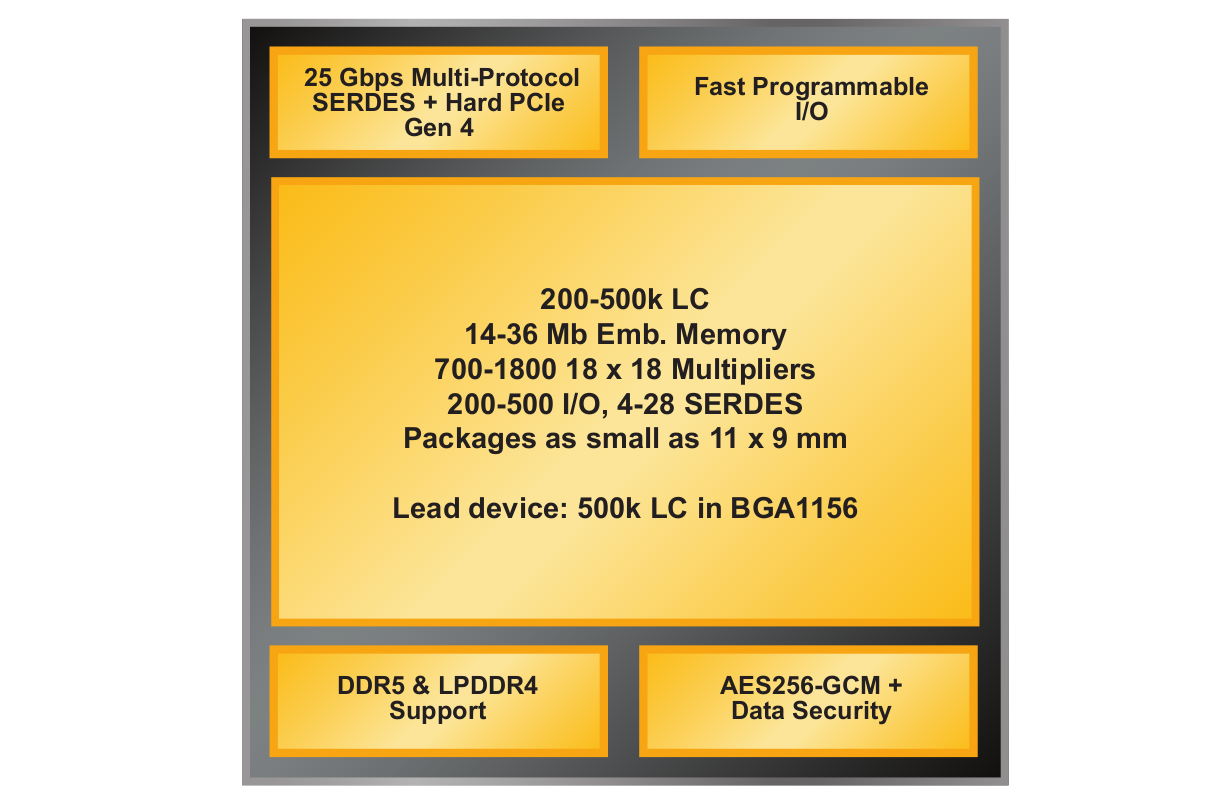

Семейство 7-нм Speedster7t FPGA предлагает порты PCIe Gen5 и интерфейсы памяти GDRR6 и DDR5/DDR4, обеспечивает скорость до 400 Гбит/с на портах Ethernet и включает в себя 2D-сеть на кристалле (2D NoC), которая может обрабатывать 20 Тбит/с общей пропускной способности.

Читать далее «Achronix Speedster7t AC7t1500 FPGA теперь доступен для приложений с высокой пропускной способностью»