Основанная около трех лет назад компания Akeana официально запустила три линейки 32- и 64-битных RISC-V процессоров и IP-блоков SoC: серия Akeana 100 для 32-битных микроконтроллеров, серия Akeana 1000 для 64-битных процессоров с MMU, а также серия Akeana 5000 с повышенной однопоточной производительностью, предназначенная для ноутбуков, центров обработки данных и облачной инфраструктуры.

Компания также представила IP-блоки Scalable Coherent Interconnect, Interrupt Controller и IOMMU для построения вычислительных подсистем на основе упомянутых ядер RISC-V, а также векторные ядра RISC-V для задач ИИ и IP-блоки матричных вычислений. Сообщается, что команда разработчиков ранее работала над серверными чипами ThunderX2 компании Marvell.

Серия Akeana 100

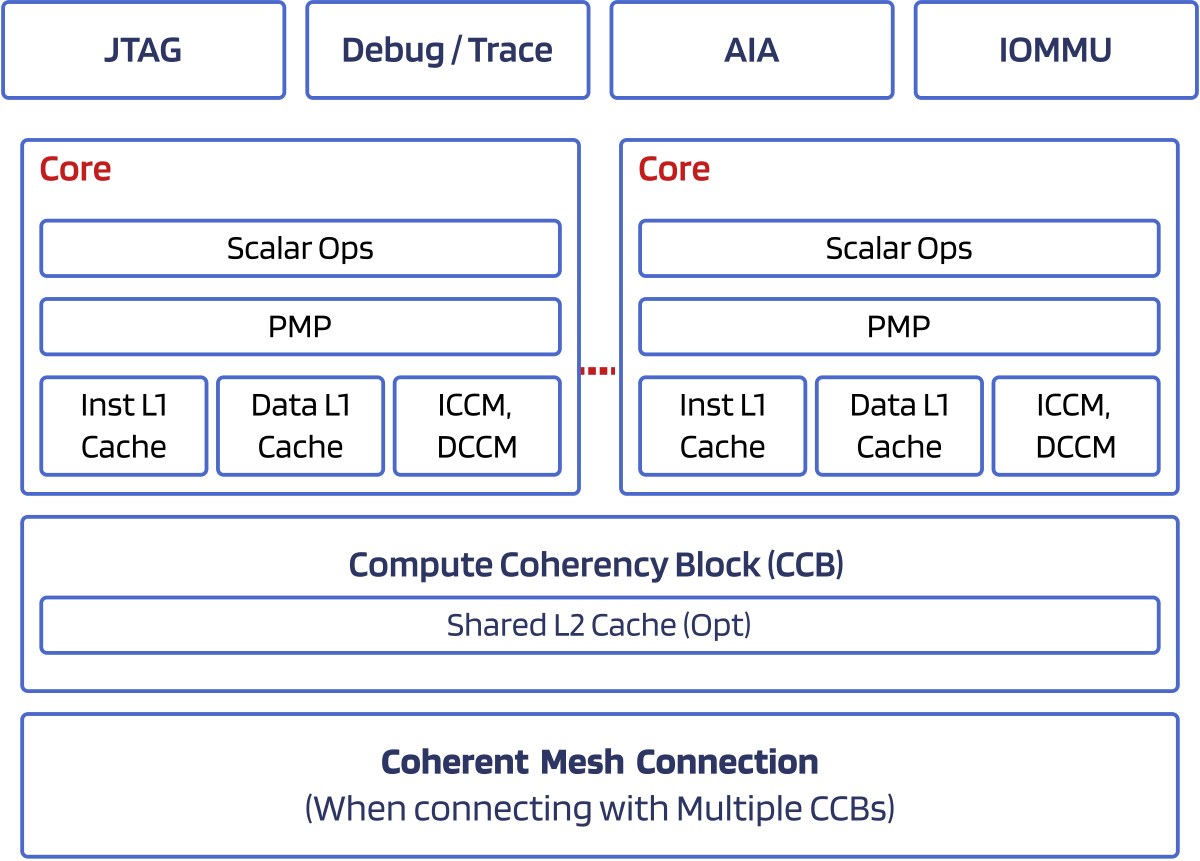

Серия Akeana 100 представляет собой линейку высоконастраиваемых процессоров с 32-битными ядрами RISC-V, поддерживающих приложения от встраиваемых микроконтроллеров до пограничных шлюзов и персональных вычислительных устройств.

Доступны четыре ядра RISC-V Akeana 100

- Akeana 110 для микроконтроллеров с ограничениями по площади и энергопотреблению

- Кэш инструкций L1: 8 КБ/ядро

- Набор инструкций RV32IMAC_Zicsr_Zifencei_Zicbo

- Диапазон физических адресов: до 32 бит

- 4-стадийный конвейер in-order

- Однократная выдача инструкций

- ICCM: 16 КБ/ядро

- DCCM: 16 КБ/ядро

- Akeana 120, 130, 140

- Общие характеристики

- Кэш инструкций L1: 16 КБ/ядро

- Набор инструкций RV32IMAC_Zicsr_Zifencei_Zicbo

- Диапазон физических адресов: до 32 бит

- Защита физической памяти (PMP) с 8 записями

- Akeana 120 для микроконтроллеров с ограничениями по площади и энергопотреблению

- 5-стадийный конвейер in-order

- Однократная выдача инструкций

- ICCM: 64 КБ/ядро

- DCCM: 64 КБ/ядро

- Akeana 130 для микроконтроллеров

- 9-стадийный конвейер in-order

- Двойная выдача инструкций

- ICCM: 64 КБ/ядро

- DCCM: 64 КБ/ядро

- Предсказатель ветвлений

- Дополнительный АЛУ для повышения производительности

- Akeana 140 для высокопроизводительных микроконтроллеров

- 9-стадийный конвейер in-order

- Двойная выдача инструкций

- Кэш данных L1: 16 КБ/ядро

- ICCM: 512 КБ/ядро

- DCCM: 512 КБ/ядро

- Предсказатель ветвлений

- Дополнительный АЛУ для повышения производительности

- Общие характеристики

Серия Akeana 1000

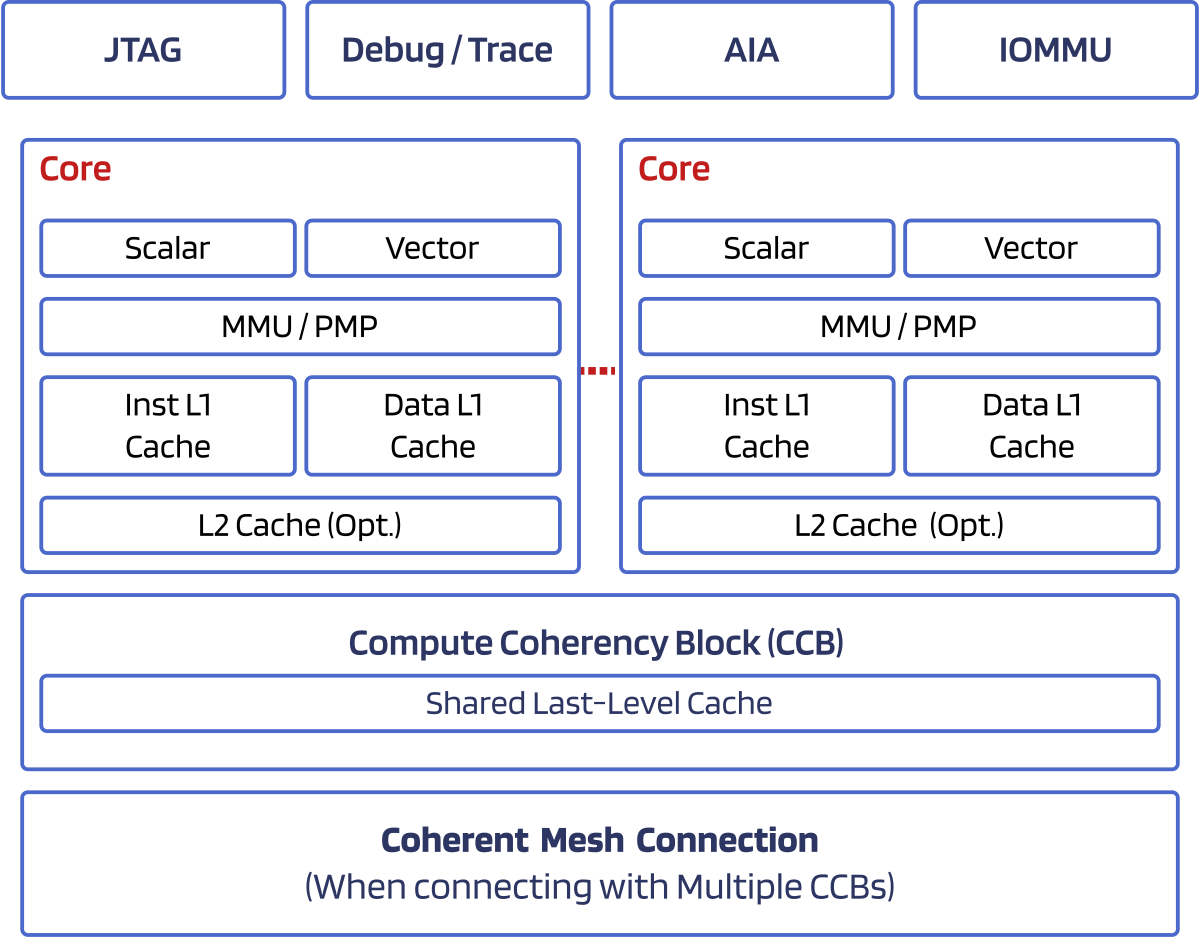

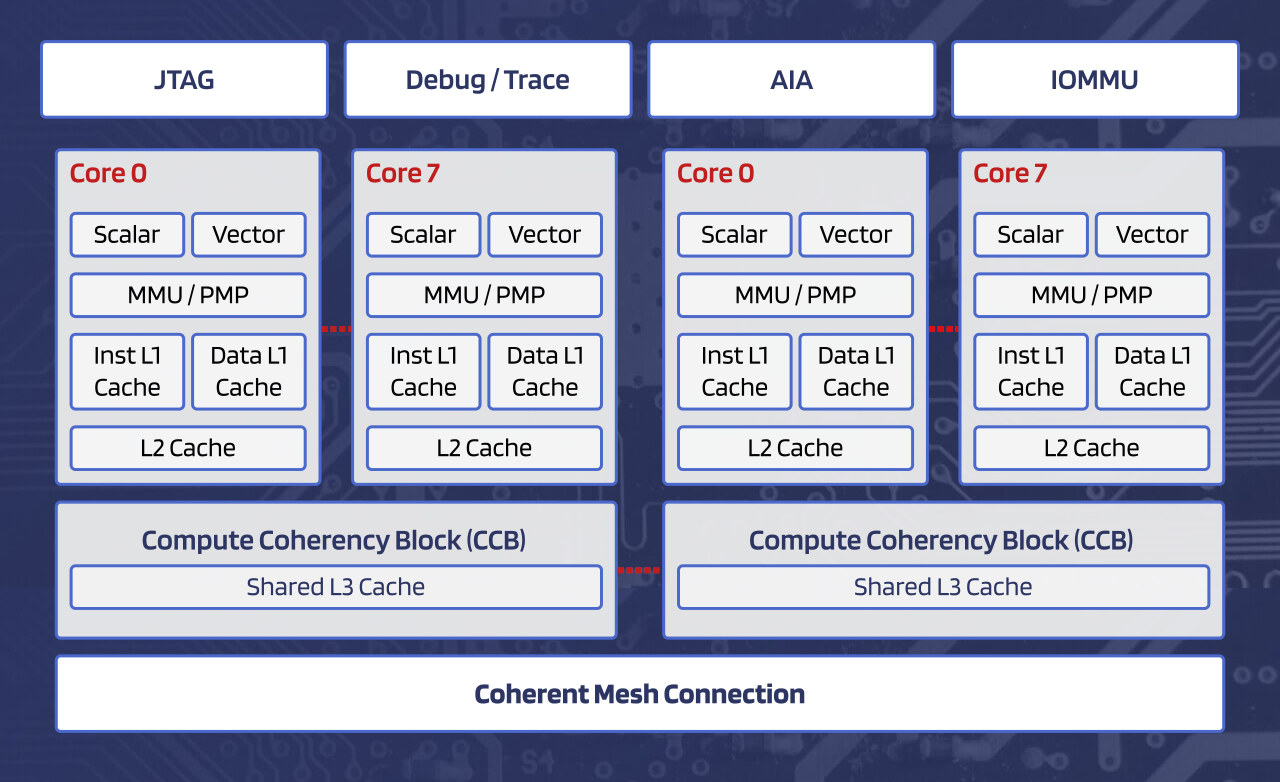

Серия Akeana 1000 включает 64-битные ядра RISC-V с MMU для поддержки полнофункциональных ОС при сохранении низкого энергопотребления и малой площади кристалла. Эти процессоры поддерживают конвейеры in-order или out-of-order, многопоточность, векторные расширения, расширения гипервизора и другие компоненты современных и перспективных профилей RISC-V (например RVA23), а также опциональные расширения для ИИ-вычислений.

В настоящее время предлагаются три ядра RISC-V Akeana 1000:

- Общие характеристики

- Набор инструкций RV64GCB_Zicbo

- Полный профиль RISC-V RVA22

- Операции с плавающей запятой одинарной и двойной точности

- Пользовательский режим

- Привилегированный режим

- Диапазон виртуальных адресов: 48 бит

- Диапазон физических адресов: 39 бит

- Масштабирование до полностью когерентных многоядерных кластеров

- Поддержка ECC

- AXI/ACE (512 бит)

- Защита физической памяти (PMP) с 16 записями MU

- Akeana 1100 для высокопроизводительных микроконтроллеров

- 9-стадийный конвейер in-order

- Двойная выдача инструкций

- Кэш инструкций L1: 16 КБ/ядро

- Кэш данных L1: 16 КБ/ядро

- MMU с TLB: 256 записей, 4-канальный

- Akeana 1200 для SoC пограничных шлюзов

- 9-стадийный конвейер in-order

- Трехкратная выдача инструкций

- Дополнительный АЛУ в конвейере

- Кэш инструкций L1: 32 КБ/ядро

- Кэш данных L1: 32 КБ/ядро

- MMU с TLB: 256 записей, 4-канальный

- Akeana 1300 для SoC пограничных шлюзов или в качестве «малого» ядра в конфигурациях Big/Little с ядрами серии Akeana 5000

- 12-стадийный конвейер out-of-order

- Четырехкратная выдача инструкций

- Кэш инструкций L1: 32 КБ/ядро

- Кэш данных L1: 32 КБ/ядро

- Кэш L2: 256 КБ

- MMU с TLB: 512 записей, 4-канальный

Серия Akeana 5000

Серия Akeana 5000 представляет собой линейку высокопроизводительных процессоров RISC-V, которые, по заявлению компании, превосходят «устоявшихся конкурентов и экосистему RISC-V». Эти 64-битные ядра RISC-V оптимизированы для требовательных приложений в устройствах нового поколения, ноутбуках, центрах обработки данных и облачной инфраструктуре. Совместимые с серией Akeana 1000 процессоры обладают значительно более высокой однопоточной производительностью.

Разработаны три ядра RISC-V серии Akeana 5000

- Общие характеристики

- Набор инструкций RV64GCVBK_Zicbo + USH

- Полный профиль RISC-V RVA23

- Операции с плавающей запятой одинарной и двойной точности

- Пользовательский режим

- Привилегированный режим

- Расширение гипервизора

- Векторное расширение (128 бит)

- Векторное криптографическое расширение

- 12-стадийный конвейер out-of-order

- Диапазон виртуальных адресов: 48 бит

- Кэш L2: 256 КБ

- Масштабирование до полностью когерентных многоядерных кластеров

- Поддержка ECC

- AXI/ACE (512 бит)

- Защита физической памяти (PMP) с 16 записями

- MMU

- Akeana 5100 для использования в качестве «большого» ядра в конфигурациях Big/Little с «малыми» ядрами серии Akeana 1000

- Четырехкратная выдача инструкций

- Кэш инструкций L1: 32 КБ/ядро

- Кэш данных L1: 32 КБ/ядро

- Пространство физических адресов: 33 бита

- MMU с TLB: 512 записей, 4-канальный

- Akeana 5200 для использования в SoC ноутбуков в качестве «большого» ядра в конфигурациях Big/Little с «малыми» ядрами серии Akeana 1000

- Шестикратная выдача инструкций

- Кэш инструкций L1: 32 КБ/ядро

- Кэш данных L1: 32 КБ/ядро

- Предвыборка кэша L2

- Пространство физических адресов: 39 бит

- MMU с TLB: 1024 записи, 4-канальный

- Akeana 5300 – вычислительное ядро для центров обработки данных/инфраструктуры

- Восьмикратная выдача инструкций

- Кэш инструкций L1: 64 КБ/ядро

- Кэш данных L1: 64 КБ/ядро

- Предвыборка кэша L2

- Пространство физических адресов: 39 бит

- MMU с TLB: 2048 записей, 8-канальный

Другие IP-блоки и программное обеспечение

Компания также представила «IP-блоки процессорных систем», необходимые для разработки SoC, включая когерентный кластерный кэш, I/O MMU и IP-блоки контроллера прерываний. Akeana также предоставляет IP-блоки Scalable Mesh и Coherence Hub (совместимые с AMBA CHI) для построения крупных когерентных вычислительных подсистем для центров обработки данных и других применений. Также доступен ИИ-ускоритель Matrix Computation Engine для выгрузки операций матричного умножения.

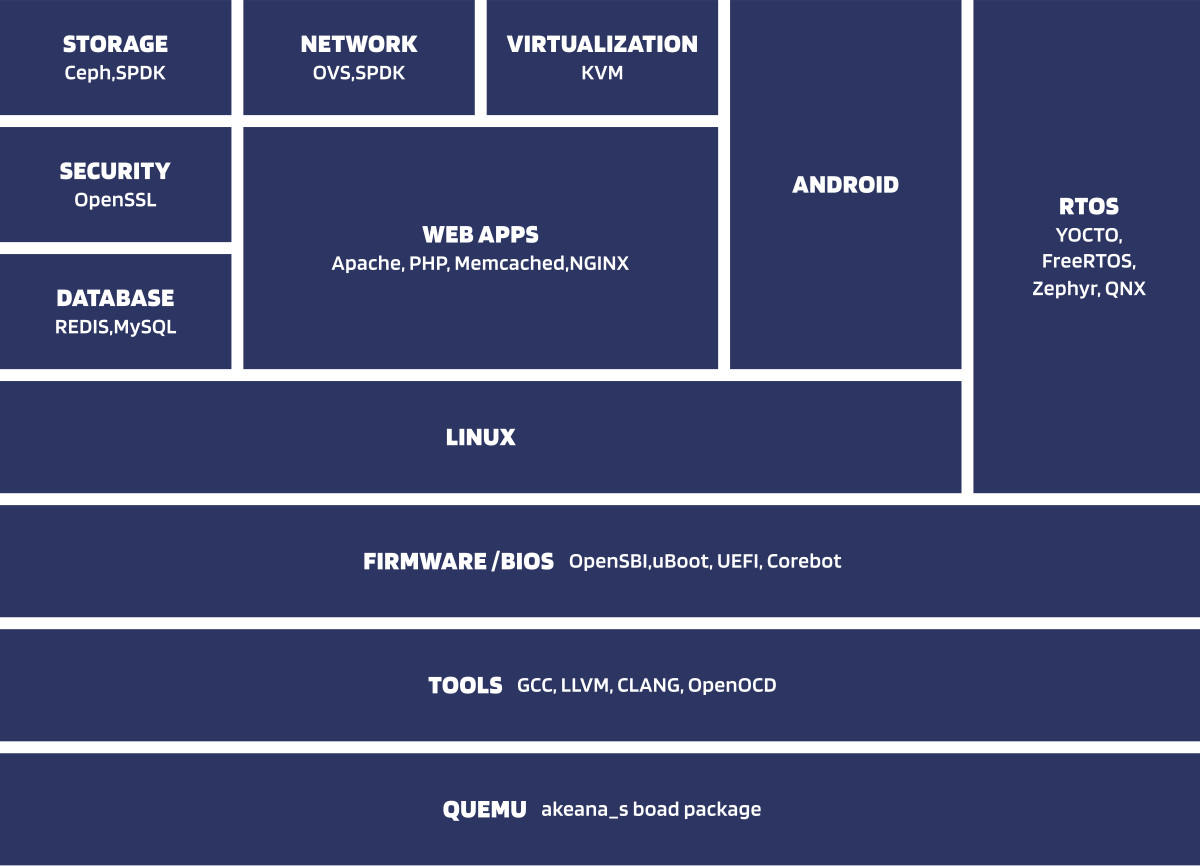

Информация о ПО ограничена, но Akeana предоставляет SDK с:

Поддерживаются Android и Linux для процессоров приложений, а также FreeRTOS, Zephyr и QNX для микроконтроллеров.Дополнительная информация доступна на веб-сайте компании и в анонсе .

Выражаем свою благодарность источнику, с которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.