Lattice Semiconductor недавно представила семейство FPGA MachXO5D-NX, которое интегрирует аппаратный корень доверия (RoT) в маломощные FPGA. Это решает проблемы безопасности, объединяя встроенную флэш-память и аппаратное шифрование для минимизации рисков захвата кода во время загрузки.

Семейство MachXO5D-NX включает три варианта с количеством логических ячеек 27k (FMXO5-25), 53k (LFMXO5-55T) и 96k (LFMXO5-100T). Эти FPGA имеют встроенное аппаратное шифрование, криптографический движок, поддерживающий AES-256, ECDSA-384/521, SHA2-256/384/512 и RSA 3072/4096, а также уникальный секретный идентификатор (USID) для защиты идентификатора устройства. Созданные на основе 28-нм полностью обедненного процесса кремний-на-изоляторе (FD-SOI), эти FPGA снижают энергопотребление на 75% и снижают частоту временных и непостоянных ошибок в 100 раз (как упоминает компания). Они поддерживают такие интерфейсы, как MIPI D-PHY (CSI-2, DSI), LVDS, Gigabit Ethernet и PCIe, что делает их пригодными для защищенных периферийных приложений.

Технические характеристики семейства Lattice MachXO5D-NX FPGA

- FPGA – семейство Lattice Semi MachXO5D-NX FPGA (27k (FMXO5-25), 53k (LFMXO5-55T) и 96k (LFMXO5-100T))

- Программируемая логика – от 27 тыс. до 96 тыс. логических ячеек, от 20 до 156 умножителей

- Память – встроенная память от 1,9 Мбит до 7,3 Мбит, поддержка DDR3/DDR3L/LPDDR4

- Интерфейсы – MIPI D-PHY, LVDS, SLVS, SGMII, PCIe Gen1/2, Ethernet

- Ввод-вывод – 200-300 программируемых вводов-выводов, высокопроизводительных (1,8 В) и широкодиапазонных (3,3 В)

- Аналоговый порт — оснащен двумя АЦП (1 МБИТ/с, 12-битный SAR), тремя компараторами непрерывного действия

- Функции безопасности – шифрование потока битов (AES-256), аутентификация (ECDSA), безопасная загрузка

- Дополнительные функции – восстановление данных тактовой частоты (CDR), блоки sysDSP с динамическим сдвигом для AI/ML, sysMEM EBR, мягкое устранение ошибок, двойной АЦП, двойной ЦАП

- Управление питанием – режимы низкого энергопотребления и высокой производительности

- Размеры – 17 x 17 мм.

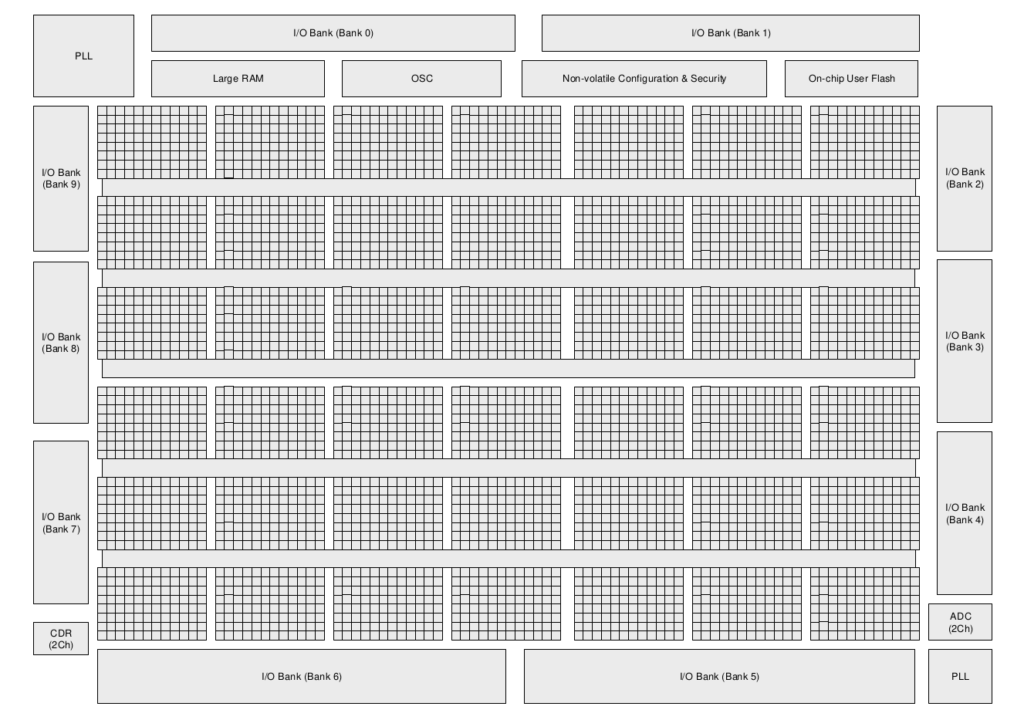

Упрощенная структурная схема устройства LFMXO5-15D

Обратите внимание, что это краткий обзор возможностей семейства MachXO5-NX FPGA. Более подробную информацию можно найти в техническом описании семейства MachXO5-NX на веб-сайте Lattice Semiconductor.

MachXO5-NX FPGA позволяют использовать искусственный интеллект и математически интенсивные приложения с умножителями и ячейками DSP. FPGA также поставляется с интерфейсами MIPI, LVDS, Ethernet, PCIe и DDR. Встроенная флэш-память поддерживает мультизагрузку и пользовательское хранилище. Кроме того, чипы совместимы с пакетом проектирования Lattice Radiant и используют готовые IP-модули.

Эта FPGA также оснащена аппаратным криптографическим движком с передовыми стандартами шифрования (AES), настоящим генератором случайных чисел и уникальным секретным идентификатором для повышенной безопасности. Устройства являются криптогибкими, что означает, что они могут переключаться между несколькими криптографическими алгоритмами или методологиями. Кроме того, они поддерживают коммерческие национальные алгоритмы безопасности (CNSA), указанные для битового потока и криптографических алгоритмов, таких как AES-256 и SHA2-512. Благодаря интеграции функций безопасности в аппаратное обеспечение, нет необходимости выделять FPGA для обеспечения безопасности, что обеспечивает эффективное использование ресурсов.

MachXO5-NX включает в себя многоуровневую архитектуру FD-SOI, которая снижает ток утечки, что приводит к снижению энергопотребления на 75% и снижению количества программных ошибок в 100 раз. Это означает, что его можно использовать в средах с высоким уровнем электрических помех и радиационного излучения.

Другая проблема, которую решает этот чип, — риск захвата кода, захват кода выполняется после сбоя чипа. Сбой — это процесс, при котором вы подаете на чип электрический импульс или колебание напряжения, что приводит к временному сбою чипа, что позволяет хакеру обойти флаги безопасности и конфигурации, а затем может быть выполнен вредоносный код или скопирован из памяти.

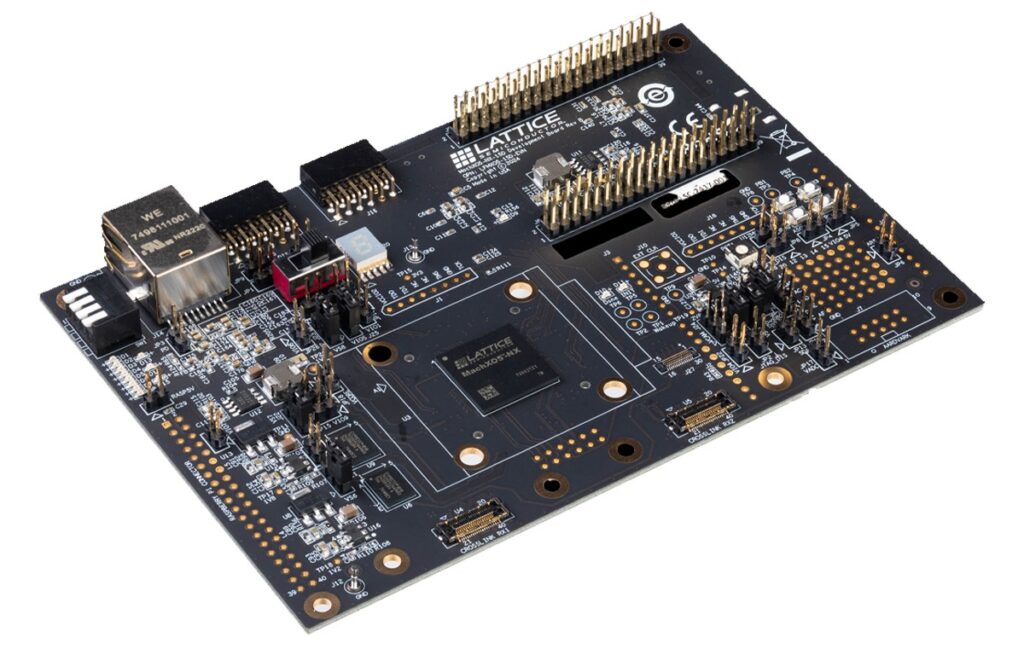

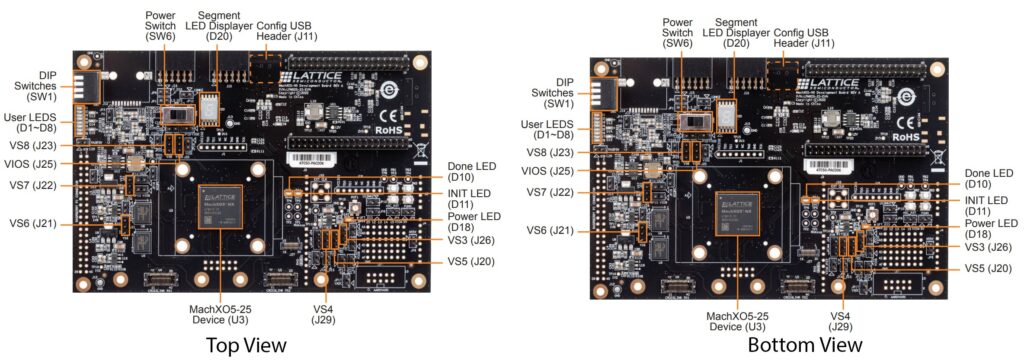

Компания также предлагает плату разработки MachXO5-NX, построенную на основе MachXO5-NX-25 FPGA, с набором функций для безопасного контроля и управления системой. Она обеспечивает гибкие возможности ввода-вывода, включая SGMII и АЦП, и, что делает ее более интересной, она совместима с различными разъемами расширения, такими как Arduino, Raspberry Pi и FX12. Кроме того, она поддерживает несколько режимов конфигурации (JTAG, I2C/I3C, SPI), встроенное программирование через USB и включает в себя такие компоненты, как HyperRAM, светодиоды, переключатели и кнопки для демонстрации и создания прототипов. Плата разработана для упрощения процесса разработки.

Нам не удалось найти ссылку на покупку самой микросхемы FPGA, но мы нашли объявление Digikey, где плату разработки можно купить за 199$. Более подробную информацию о чипе можно найти на странице продукта компании или в пресс-релизе .

Комплект разработчика Lattice MachXO5D-NX FPGA от DigiKey

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.