Arduino представила свою первую плату FPGA около двух лет назад. Это была плата MKR Vidor 4000, сочетающая в себе Intel Cyclone FPGA с микрочипом SAMD21 Cortex-M0 + MCU в форм-факторе, аналогичном Arduino Zero.

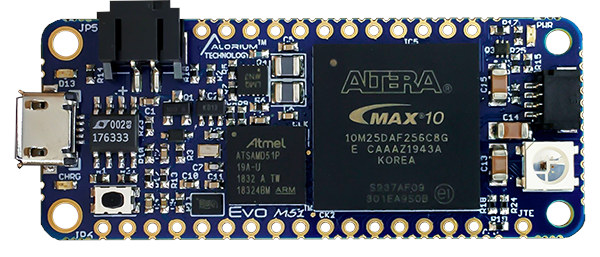

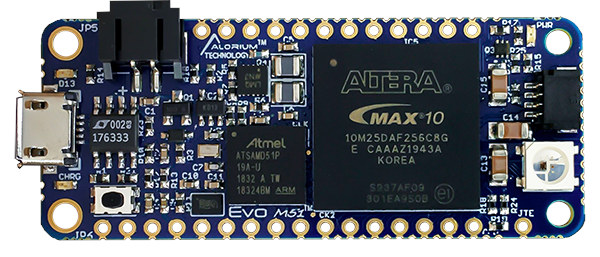

Но в случае, если вы ищете еще меньшую совместимую с Arduino плату FPGA, Evo M51 от Alorium Technology может быть именно тем, что вам нужно. Плата, в форм-факторе Adafruit Feather, оснащена микроконтроллером Atmel SAMD51 Arm Cortex-M4F в сочетании с Intel MAX 10 FPGA.

Читать далее «Плата Evo M51, в форм-факторе Feather, объединяет микроконтроллер Atmel SAMD51 с процессором Intel MAX 10 FPGA»