Правительство Индии инвестирует в стимулирование своей отрасли проектирования и производства полупроводников, по меньшей мере, с 2018/2019 годов, на примере микропроцессоров SHAKTI и AJIT . В 2022 году было принято решение сосредоточиться на архитектуре RISC-V с семейством процессоров VEGA , начав с микропроцессоров THEJAS32 (VEGA ET1031) и THEJAS64 (VEGA AS1061). Первый в итоге был использован в плате для разработки ARIES v3.0, вдохновлённой Arduino UNO .

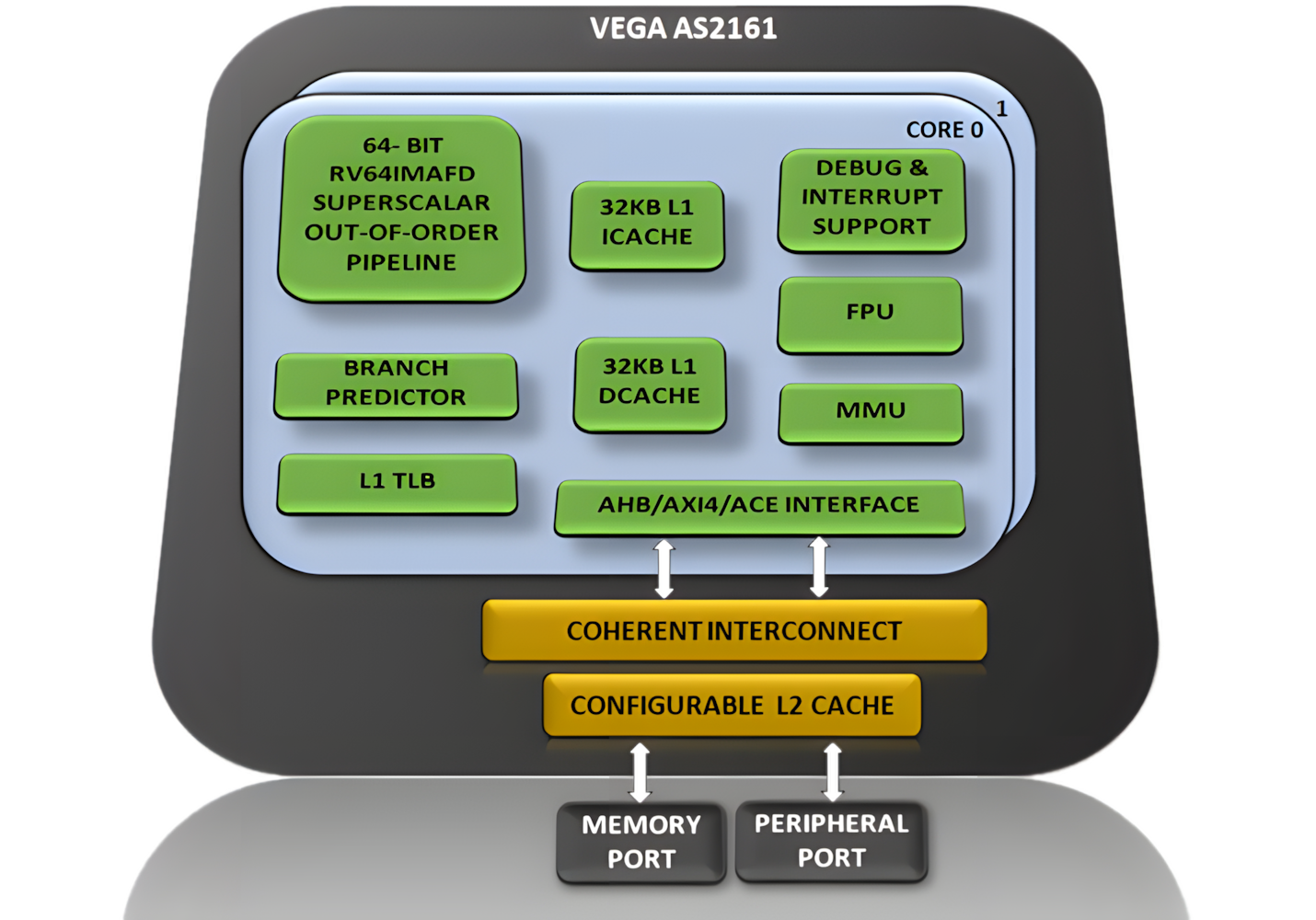

Работа продолжается успешно, хотя и медленно, и правительство объявило о запуске двухъядерного 64-разрядного RISC-V микропроцессора DHRUV64 (VEGA AS2161) с тактовой частотой 1 ГГц и поддержкой Linux, который описан как «полностью отечественный микропроцессор, разработанный Центром развития передовых вычислений (C-DAC) в рамках Программы разработки микропроцессоров (MDP)».

VEGA AS2161 (DHRUV64) основные характеристики:

- Архитектура – Набор команд RISC-V 64G (RV64IMAFD)

- 13-16-стадийная реализация внеочередного конвейера.

- Продвинутый предсказатель переходов – BTB, BHT, RAS.

- Гарвардская архитектура, раздельные память команд и данных.

- Уровни привилегий: пользовательский, супервизора и машины.

- Полнофункциональная подсистема памяти с поддержкой Linux: Блок управления памятью (MMU), страничная виртуальная память, настраиваемые кеши L1 и L2.

- Высокопроизводительное межъядерное соединение.

- Высокопроизводительный блок операций с плавающей запятой, совместимый со стандартом IEEE 754-2008.

- Внешний интерфейс, совместимый с AXI4 / ACE.

- Контроллер прерываний на уровне платформы (до 127 IRQ, низкая задержка прерываний).

- Поддержка векторизированных прерываний

- Расширенный встроенный контроллер отладки – совместимый с JTAG интерфейс, поддержка аппаратных и программных точек останова

- Расширение отладки, позволяющее отладку в Eclipse через соединение GDB >> openOCD >> JTAG

Кроме Linux, сообщается, что порты ОС Zephyr и FreeRTOS также доступны или находятся в разработке. Спецификации сосредоточены на самом процессорном IP, но фотография чипа выше подразумевает, что существует и полный SoC с вводами/выводами.

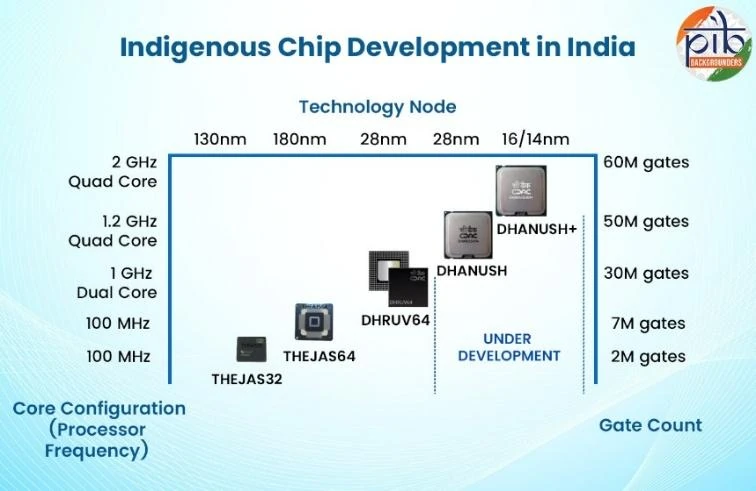

В пресс-релизе отмечается, что это третий чип, произведенный по программе Digital India RISC-V (DIR-V):

Первый чип, THEJAS32, произведен на предприятии Silterra в Малайзии.

Второй чип, THEJAS64, произведен внутри страны в Semiconductor Lab (SCL) Мохали.

Важно различать проектирование и производство процессора, поскольку это разные этапы прогресса страны в секторе полупроводников. Например, ранее рассматривался 28-нм SoC Elvees SKIF «Scythian», разработанный в России , но произведенный в другой стране, так как строительство 28-нм производственных мощностей в России займет несколько лет.

Если посмотреть на дорожную карту развития чипов в Индии (неизменную с 2022 года), можно увидеть, что THEJAS64 был произведен по 180-нм техпроцессу, и это было сделано на индийском заводе. В правительственном пресс-релизе прямо не сказано, где производится DHRUV64, но весьма вероятно, что не в Индии, хотя запуск 28-нм производственных мощностей запланирован на конец декабря 2026 года . Следующими этапами будут «проектирование, реализация и производство вариантов систем-на-кристалле (SoC) DHANUSH64 и DHANUSH64+», работа над которыми уже началась.

Чип предназначен для инфраструктуры 5G, автомобильных систем, потребительской электроники, промышленной автоматизации и Интернета вещей (IoT). Несколько дополнительных деталей можно найти на странице продукта для микропроцессора VEGA AS2161.

Выражаем свою благодарность источнику, с которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.