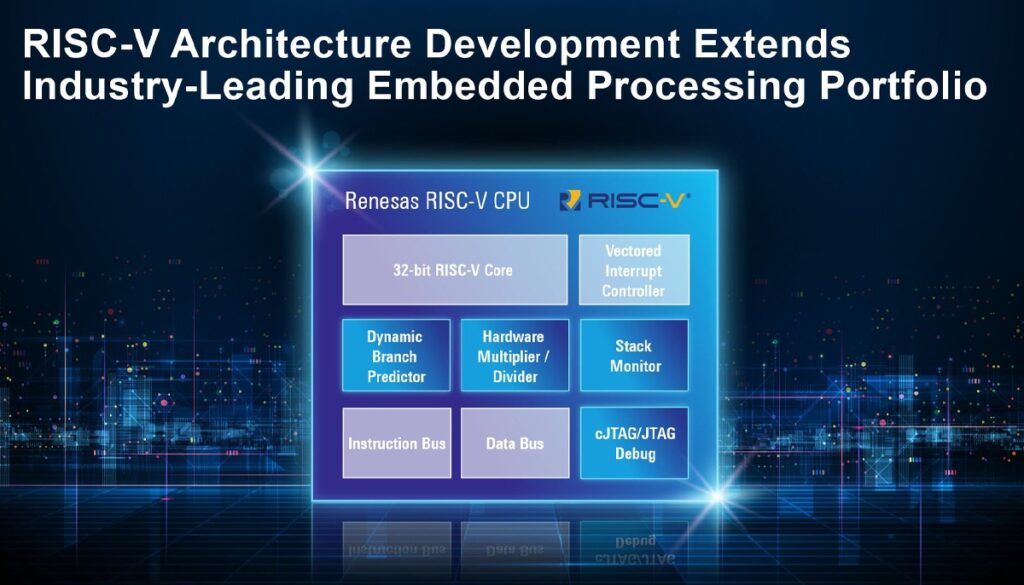

Недавно компания Renesas анонсировала свое первое 32-битное ядро ЦП RISC-V собственного производства, основанное на архитектуре набора команд открытого стандарта (ISA). Это ядро ЦП совместимо с IDE Renesas e2 studio и поддерживает другие сторонние IDE для микроконтроллеров RISC-V. По данным Renesas, процессор достиг замечательной производительности 3,27 CoreMark/МГц, превзойдя аналогичные архитектуры RISC-V в этой категории.

RISC-V, открытая ISA, быстро набирает популярность в полупроводниковой промышленности. Многие поставщики MCU сформировали совместные инвестиционные альянсы, чтобы ускорить разработку продуктов RISC-V. Ранее Renesas выпустила два процессора, разработанных Andes Technology Corp: R9A02G020 , микроконтроллер ASSP EASY для управления двигателем, и R9A06G150 , микроконтроллер ASSP EASY для голосового интерфейса, оба основаны на RISC-V. Кроме того, они представили RZ/Five, семейство 64-битных микропроцессоров RISC-V с поддержкой Linux, и RH850/U2B, автомобильную систему-на-кристалле (SoC). Однако, с выпуском нового процессора Renesas самостоятельно выходит на рынок RISC-V, подчеркивая свои усилия по расширению линейки продуктов RISC-V.

Основные технические характеристики:

- Универсальные приложения: новый ЦП является гибким, поэтому его можно настроить в качестве основного контроллера приложений, вторичного ядра в системе-на-кристалле (SoC), внутрикристальных подсистемах или в глубоко встроенных стандартных продуктах для конкретных приложений (ASSP).

- Оптимизированная производительность: ЦП обеспечивает оптимизированную производительность с опциями RV32 «I» или «E», что означает, что он может регулировать количество регистров общего назначения в соответствии с потребностями различных приложений.

- Интегрированные расширения RISC-V:

- Расширение M: расширяет возможности операций умножения и деления.

- Расширение A: поддерживает атомарный доступ, что имеет решающее значение для параллелизма в системах на базе RTOS.

- Расширение C: предлагает 16-битные сжатые инструкции для повышения эффективности использования памяти.

- Расширение B: обеспечивает расширенные возможности манипуляции битами.

- Вычислительная производительность: процессор обеспечивает 3,27 CoreMark/МГц, превосходя аналогичные архитектуры по эффективности и скорости.

Расширенные функции для надежных приложений:

- Регистр Stack Monitor: предотвращает переполнение памяти стека, повышая целостность системы.

- Модуль динамического прогнозирования ветвей: повышает производительность выполнения кода.

- Компактный интерфейс отладки JTAG: обеспечивает эффективную отладку, дополненную регистрами монитора производительности.

- Модуль трассировки инструкций: предлагает разработчикам более глубокое понимание поведения системы.

Новый процессор совместим с Renesas e2 Studio и множеством сторонних интегрированных сред разработки (IDE), предоставляя полный набор инструментов для разработки продуктов. Кроме того, функции и производительность ЦП были проверены на реальном кремниевом продукте, а более подробная информация будет опубликована на веб-сайте EEMBC после первого запуска продукта в начале 2024 года.

Дополнительную информацию по этой теме можно найти на странице анонса продукта, а на отдельной странице представлены подробности о ядре ЦП RISC-V и его функциях.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.