UPduino v3.1 — это доступная платформа разработки, демонстрирующая возможности Lattice ICE40 Ultra Plus 5K FPGA. Это устройство также полностью совместимо с инструментом графического дизайна с открытым исходным кодом IceStudio.

UPduino v3.1 построен на четырехслойной печатной плате и оснащен интеграцией Lattice UltraPlus ICE40UP 5K FPGA. Эта FPGA имеет 5,3 КБ LUT и оснащена 1 МБ SPRAM (однопортовое ОЗУ), 120 КБ DPRAM и 8 множителями, как указано на странице продукта.

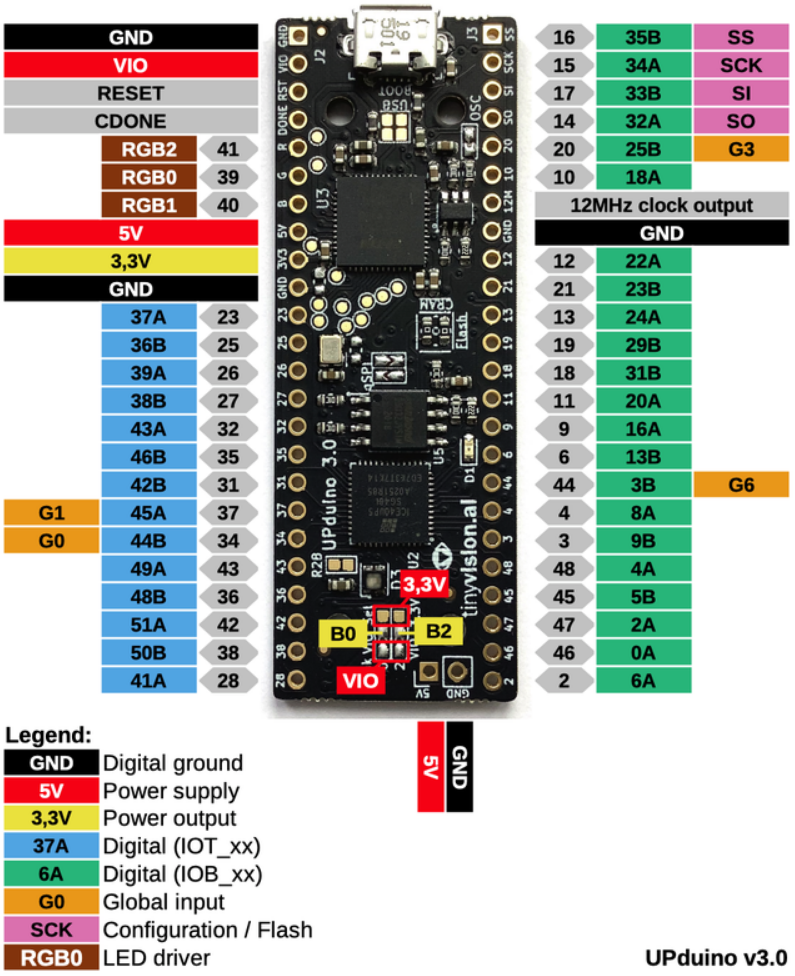

Хотя изображение распиновки, представленное ниже, иллюстрирует конфигурацию контактов для UPduino 3.0, важно отметить, что версия 3.1 включает в себя некоторые обновления, как указано на странице продукта. Эти обновления включают исправление ошибки шелкографии 12 МГц и заземления, а также замену ферритового шарика USB-фильтра на решение PTC.

Последнее изменение направлено на решение проблем, связанных с возможным повреждением ферритового шарика в случае короткого замыкания между 5 В и землей.

Для UPduino доступно несколько источников документации, например Wiki -страницы UPduino, предлагающие учебные пособия. Кроме того, вы можете найти ценные ресурсы в репозитории tinyVision. Кроме того, репозиторий XarkLabs GitHub предоставляет пример проекта для UPduino с использованием SystemVerilog.

Характеристики, перечисленные для UPduino-v3.1, включают:

- Память/Хранение:

- Флэш-память SPI 4 МБ

- Интерфейсы ввода/вывода:

- 32 порта FPGA GPIO на разъемах 0,1 дюйма

- 1x RGB-светодиод

- USB:

- Устройство FTDI FT232H USB-SPI

- Другие особенности:

- Встроенный генератор 12 МГц.

- Питание:

- Встроенные регуляторы 3,3 В и 1,2 В.

- Размеры:

- 2,2 х 6,2 х 0,5 см

Дополнительная информация

UPduino стоит 27,23 евро на Lectronz или 30 долларов на Tindie.com.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту linuxgizmos.com

Оригинал статьи вы можете прочитать здесь.