MIPS мертв, верно? Сейчас очень мало сделано по самой архитектуре, MIPS (компания) решила перейти на архитектуру RISC-V и представила линейку продуктов eVocore, в настоящее время состоящую из многопроцессорных IP-ядер eVocore P8700 и I8500.

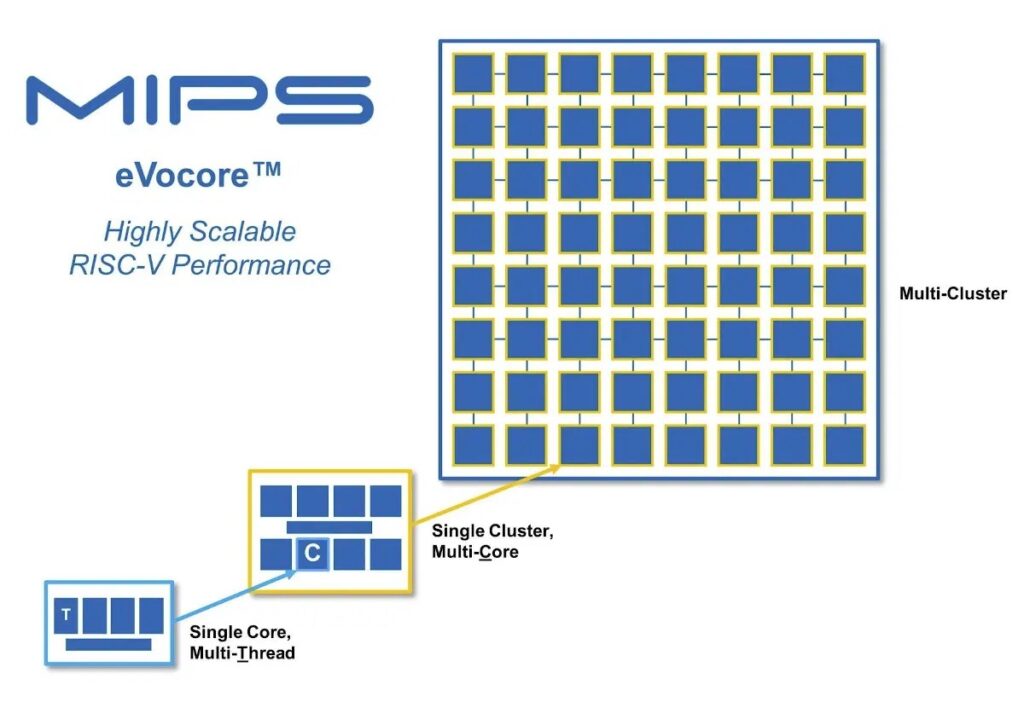

64-разрядные ядра масштабируются от одноядерного многопоточного до одного кластера с несколькими ядрами и до многокластерного и предназначены для высокопроизводительных вычислительных приложений в реальном времени, таких как сети, центры обработки данных и автомобильная промышленность.

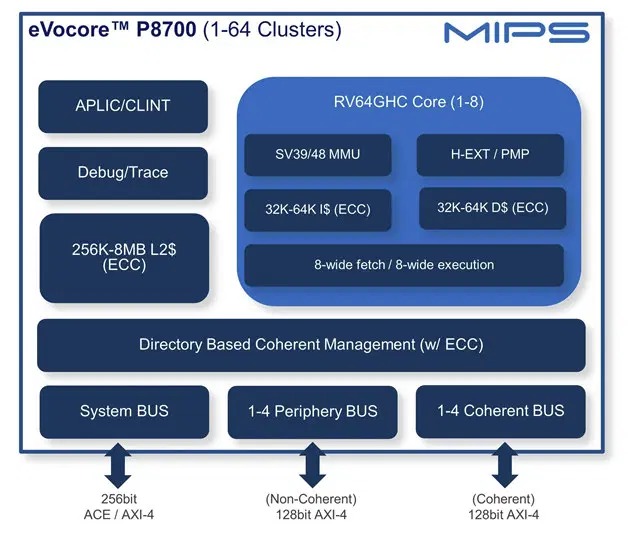

eVocore P8700 поставляется с 16-ступенчатым конвейером с многозадачным процессором с внеочередным исполнением инструкций (Out-of-Order processors, OoO) и многопоточностью. MIPS утверждает, что его однопоточная производительность выше, чем в настоящее время доступна в других IP-предложениях ЦП RISC-V, но не предоставила никаких цифр. Скорее всего, он будет использоваться в облаке и на высокопроизводительных серверах, поскольку может масштабироваться до 64 кластеров, 512 ядер и 1024 потоков.

Особенности P8700:

- Многозадачный суперскалярный процессор с внеочередным исполнением инструкций (Out-of-Order processors, OoO) с многопоточностью

- 16-ступенчатый конвейер для более высокой тактовой частоты

- 8-широкая выборка инструкций

- 8-исполнительные каналы: 2xALU, MDU, 2xFPU, 2xMemory

- Enhanced Coherence Manager с кэшем L2

- Предварительная выборка HW, расширенные шины, уменьшенная задержка

- 48-битная физическая адресация

- Поддержка 256 прерываний, APLIC/CLINT

- Системный интерфейс

- ACE или AXI: 256-битная системная шина

- Дополнительно: Coherent Bus (до 8 портов)

- Дополнительно: некогерентная периферийная шина (до 4 портов)

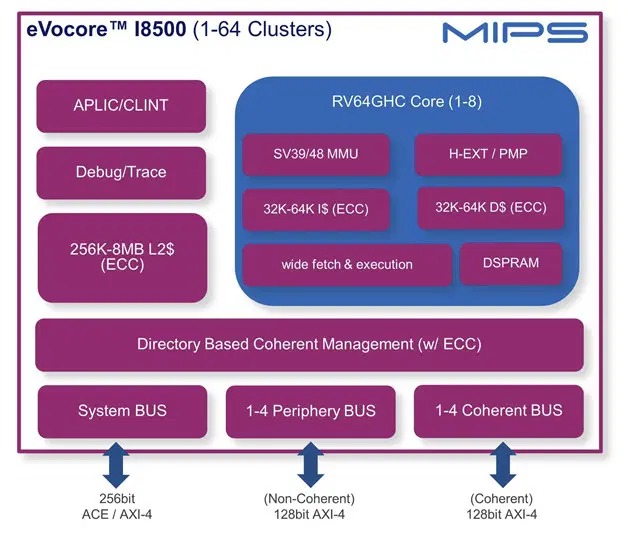

Ядро MIPS eVocore I8500 RISC-V направлено на достижение «лучшей в своем классе эффективности производительности» с многопроцессорной системой для использования в программных процессорах. Каждое ядро I8500 сочетает в себе многопоточность и эффективный конвейер с тремя задачами.

Особенности I8500:

- Поочередное выполнение инструкций с одновременной многопоточностью (SMT)

- 9-ступенчатый конвейер для эффективного выполнения

- Широкая выборка инструкций

- 7-исполнительные каналы: ALU, MDU, 2xFPU, 2xMemory

- Enhanced Coherence Manager с кэшем L2

- Предварительная выборка HW, расширенные шины, уменьшенная задержка

- 48-битная физическая адресация

- Поддержка 256 прерываний, APLIC/CLINT

- Системный интерфейс

- ACE или AXI: 256-битная системная шина

- Дополнительно: Coherent Bus (до 8 портов)

- Дополнительно: некогерентная периферийная шина (до 4 портов)

Очевидно, что MIPS планирует использовать определяемые пользователем инструкции (UDI) RISC-V для добавления дополнительных функций/ускорителей, сохраняя при этом полную совместимость с готовыми инструментами разработки RISC-V и программными библиотеками. Другие функции IP-ядер eVocore включают привилегированную аппаратную виртуализацию, многопоточность, гибридную отладку и функциональную безопасность. Компания ожидает, что они будут использоваться в автомобилях (ADAS, AV, IVI), 5G и беспроводных сетях, центрах обработки данных и хранилищах, а также в высокопроизводительных встроенных приложениях.

eVocore P8700 будет доступен в четвертом квартале 2022 года, но ETA для eVocore I8500 IP не было предоставлено. Более подробную информацию можно найти на странице продукта.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.