В прошлом месяце мы получили комплект разработчика Microchip PolarFire SoC FPGA Icicle, оснащенный PolarFire SoC FPGA, состоящим из подсистемы RISC-V CPU с пятью 64-битными ядрами и FPGA с 254K LE, и загрузили предустановленный образ операционной системы Linux на основе OpenEmbedded.

Сегодня мы покажем, как начать работу с Yocto BSP и запустить тест EEMBC CoreMark, а через пару недель мы проверим FPGA с Libero SoC Design Suite.

Операционные системы, поддерживаемые PolarFire SoC FPGA

Первоначально, идея заключалась в том, чтобы сосредоточить эту часть обзора на Linux, проверке некоторой системной информации, запуске некоторых тестов (например, SBC-Bench), компиляции ядра Linux и установке таких сервисов, как стек LEMP (Linux, Nginx (произносится как Engine-X), MySQL, PHP), который может использоваться, например, для хостинга WordPress. Но затем мы посмотрели на операционные системы, поддерживаемые Microchip PolarFire SoC FPGA.

Есть Yocto Linux BSP и Buidlroot Linux BSP, поддерживаемые Microchip, а также дистрибутивы Embedded Linux от третьих сторон, таких как Siemens Embedded и WindRiver. Говорят, что скоро появится FreeBSD, и несколько операционных систем реального времени.

Это означает, что нет менеджера пакетов и корневой файловой системы на основе Debian, за исключением некоторых инструментов, которые мы планировали использовать. Чтобы достичь того, что мы намеревались сделать, понадобится более 100 часов работы, которых у нас нет… Поэтому мы уменьшили свой пыл и вместо этого поделимся с вами нашим опытом создания образа Yocto, кросс-компиляция hello world, а также встроенной компиляции и запуске теста EEMBC. Мы не в первый раз работаем с Yocto Project, но мы все же узнали кое-что новое в процессе, и мы надеемся, что и вы тоже.

Демонстрация веб-сервера и аналитика напряжения/тока

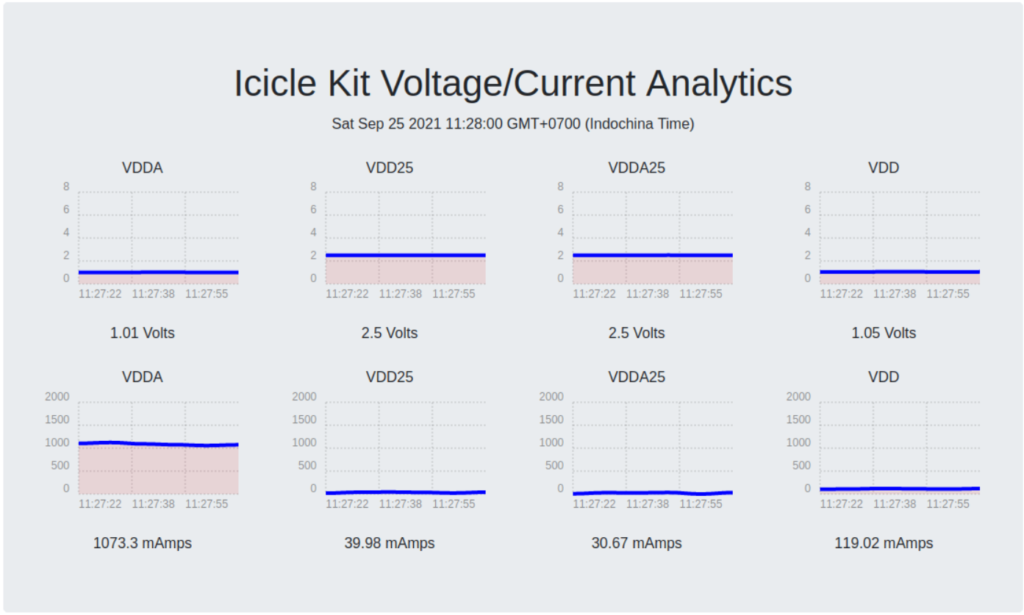

Перед тем, как приступить к работе над Yocto BSP, мы подключили плату к Ethernet, чтобы выполнить руководство по началу работы от Microchip, и запустили веб-сервер.

$ cd /opt/microchip/iiohttpserver

$ ./runМы можем получить доступ к веб-странице, на которой будут отображаться напряжение и ток для VDDA (XCVR Tx/Rx Lanes Supply), VDD25 (PLL и PNVM Supply), VDDA25 (XCVR PLL Supply) и VDD (Core Supply), перейдя по адресу http://<board_ip_address>

Будет интересно вернуться на эту страницу после того, как мы запустим тест EEMBC CoreMark.

Yocto Linux BSP

Давайте соберем Linux с помощью Yocto BSP, как описано на Github. Для справки, мы используем ноутбук под управлением Ubuntu 20.04, и нам пришлось изменить некоторые команды.

Для начала установим утилиту repo:

export REPO=$(mktemp /tmp/repo.XXXXXXXXX)

curl -o ${REPO} https://storage.googleapis.com/git-repo-downloads/repo

gpg --keyserver hkps://keyserver.ubuntu.com --recv-key 8BB9AD793E8E6153AF0F9A4416530D5E920F5C65

curl -s https://storage.googleapis.com/git-repo-downloads/repo.asc | gpg --verify - ${REPO} && install -m 755 ${REPO} ~/затем несколько зависимостей:

sudo apt install python3-distutils libyaml-dev libelf-dev chrpath diffstat

Время инициализировать repo:

~/bin/repo init -u https://github.com/polarfire-soc/meta-polarfire-soc-yocto-bsp.git -b master -m tools/manifests/riscv-yocto.xml

Теперь мы можем настроить сборку:

. ./meta-polarfire-soc-yocto-bsp/polarfire-soc_yocto_setup.sh

/home/jaufranc/edev/Microchip/yocto-dev

expect is already installed at the requested version (5.45.4-2build1)

expect is already installed at the requested version (5.45.4-2build1)

No packages will be installed, upgraded, or removed.

0 packages upgraded, 0 newly installed, 0 to remove and 9 not upgraded.

Need to get 0 B of archives. After unpacking 0 B will be used.

spawn sudo dpkg-reconfigure -freadline dash

sudo] password for jaufranc:

Configuring dash

----------------

The system shell is the default command interpreter for shell scripts.

Using dash as the system shell will improve the system's overall performance. It

does not alter the shell presented to interactive users.

Use dash as the default system shell (/bin/sh)? [yes/no] yes

Init OE

### Shell environment set up for builds. ###

You can now run 'bitbake <target>'

Common targets are:

core-image-minimal

core-image-full-cmdline

core-image-sato

core-image-weston

meta-toolchain

meta-ide-support

You can also run generated qemu images with a command like 'runqemu qemux86'.

Other commonly useful commands are:

- 'devtool' and 'recipetool' handle common recipe tasks

- 'bitbake-layers' handles common layer tasks

- 'oe-pkgdata-util' handles common target package tasks

Adding layers

NOTE: Starting bitbake server...

NOTE: Starting bitbake server...

NOTE: Starting bitbake server...

NOTE: Starting bitbake server...

NOTE: Starting bitbake server...

NOTE: Starting bitbake server...

Creating auto.conf

To build an image run

---------------------------------------------------

MACHINE=icicle-kit-es bitbake mpfs-dev-cli

---------------------------------------------------

Buildable machine info

---------------------------------------------------

Default MACHINE=icicle-kit-es

* icicle-kit-es: Microchip Polarfire SoC Icicle Kit Engineering Sample, emmc/sd boot.

* qemuriscv64: The 64-bit RISC-V machine

---------------------------------------------------

Bitbake Image

---------------------------------------------------

* mpfs-dev-cli: MPFS Linux console-only image with development packages.

* core-image-minimal-dev: OE console-only image, with some additional development packages.

* core-image-minimal: OE console-only image

* core-image-full-cmdline: OE console-only image with more full-featured Linux system functionality installed.

* qemuriscv64: The 64-bit RISC-V machine

---------------------------------------------------Чтобы начать сборку, выполните следующую команду:

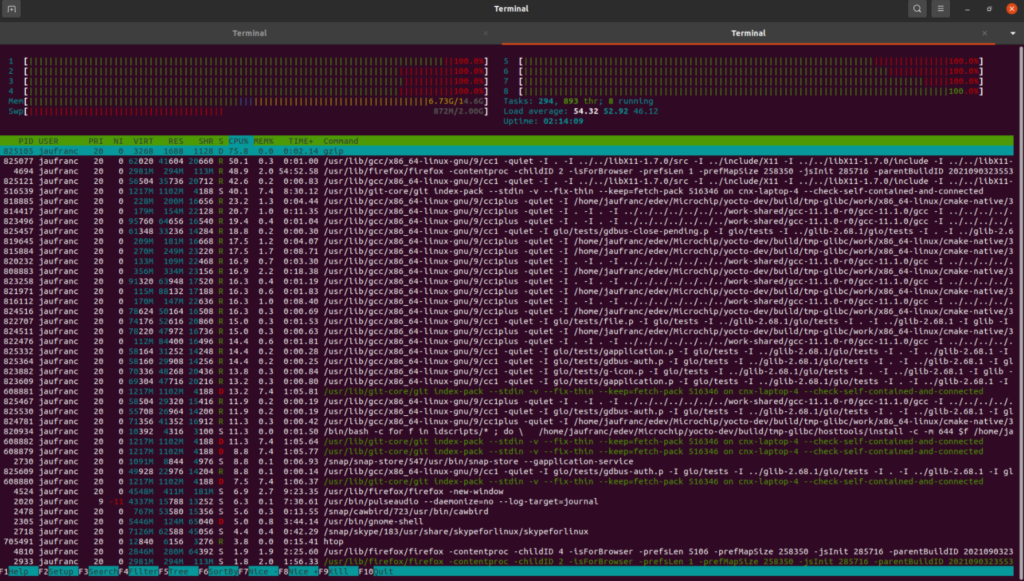

MACHINE=icicle-kit-es bitbake mpfs-dev-cliСистема сборки Yocto может занять много времени. Около 10 лет назад мы потратили более 24 часов на создание образа на недорогом ноутбуке с настройками по умолчанию. Наш ноутбук работает на 8-ядерном процессоре AMD Ryzen 7 2700U и оснащен 16 ГБ оперативной памяти, быстро становится очень медленным и почти непригодным для использования при загрузке процессора 50+:

Мы не стали торопить события. Но мы не проверили требования к хранилищу, и сборка остановилась примерно через два часа из-за того, что на нашем жестком диске заканчивается место. Как мы увидим, когда сборка будет завершена, потребуется около 100 ГБ бесплатного хранилища.

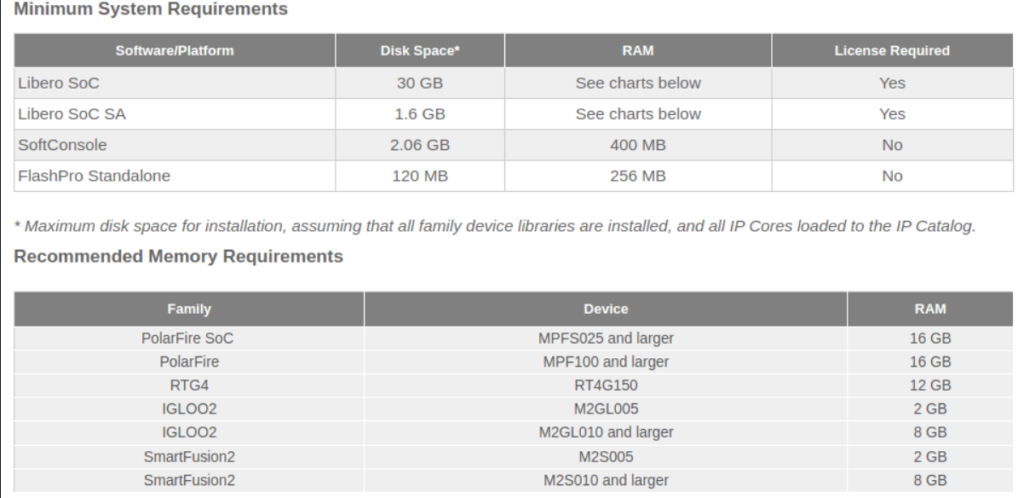

Пока мы говорим о системных требованиях, для пакета проектирования Libero SoC потребуется около 35 ГБ дополнительного места, а для разработки PolarFire SoC не менее 16 ГБ ОЗУ. Поэтому вам понадобится мощная рабочая станция для разработки приложений на комплекте разработки PolarFire SoC FPGA Icicle с большим объемом оперативной памяти и достаточным объемом памяти.

Вернемся к нашей сборке Yocto. Идеально было бы иметь выделенный сервер сборки, но если вы собираетесь использовать свой компьютер одновременно со сборкой, вы можете отредактировать [your_yocto_build_dir] /conf/local.conf

BB_NUMBER_THREADS = "4"

PARALLEL_MAKE = "-j 4"тогда

source setup-environment ./your_build_folderПеред началом сборки…

Альтернативой является приостановка сборки с помощью Ctrl-Z, который работает аналогично Ctrl-C, но использует SIGTSTP вместо SIGINT, чтобы приостановить процесс, а не завершить его.

time MACHINE=icicle-kit-es bitbake mpfs-dev-cli

Loading cache: 100% | | ETA: --:--:--

Loaded 0 entries from dependency cache.

Parsing recipes: 100% |##########################################| Time: 0:01:43

Parsing of 2381 .bb files complete (0 cached, 2381 parsed). 3667 targets, 166 skipped, 0 masked, 0 errors.

NOTE: Resolving any missing task queue dependencies

Build Configuration:

BB_VERSION = "1.51.0"

BUILD_SYS = "x86_64-linux"

NATIVELSBSTRING = "ubuntu-20.04"

TARGET_SYS = "riscv64-oe-linux"

MACHINE = "icicle-kit-es"

DISTRO = "nodistro"

DISTRO_VERSION = "nodistro.0"

TUNE_FEATURES = "riscv64"

meta = "HEAD:14795ee305f3c11fcc31cc7ca815b8ff1020e29a"

meta-oe

meta-python

meta-multimedia

meta-networking = "HEAD:dcb9ecc1e5720c9614b1cd27575e1e4886dff5c1"

meta-riscv = "HEAD:35d1d5849294ff9f2fb98b90657bbf7a1e532d0d"

meta-polarfire-soc-yocto-bsp = "HEAD:3c53ffcae8ac86686a53cd15b4541fc7eca1e36f"

NOTE: Fetching uninative binary shim http://downloads.yoctoproject.org/releases/uninative/3.1/x86_64-nativesdk-libc.tar.xz;sha256sum=5d0611df544edff6428cef7d871257a91aa6ba1bd92f5365a2df8deb54b6b31e (will check PREMIRRORS first)

Initialising tasks: 100% |#######################################| Time: 0:00:11

Sstate summary: Wanted 2529 Local 0 Network 0 Missed 2529 Current 0 (0% match, 0% complete)

NOTE: Executing Tasks

WARNING: expat-native-2.3.0-r0 do_fetch: Failed to fetch URL https://downloads.sourceforge.net/expat/expat-2.3.0.tar.bz2, attempting MIRRORS if available

WARNING: libtalloc-2.3.2-r0 do_fetch: Failed to fetch URL https://www.samba.org/ftp/talloc/talloc-2.3.2.tar.gz, attempting MIRRORS if available

WARNING: boost-1.76.0-r0 do_fetch: Failed to fetch URL https://dl.bintray.com/boostorg/release/1.76.0/source/boost_1_76_0.tar.bz2, attempting MIRRORS if available

WARNING: htop-3.0.5-r0 do_fetch: Failed to fetch URL git://github.com/htop-dev/htop.git, attempting MIRRORS if available

Currently 8 running tasks (5382 of 7084) 75% |####################### |

Currently 6 running tasks (6040 of 7084) 85% |########################## |

0: cmake-3.20.1-r0 do_compile (pid 3565535) 72% |#################### |

1: boost-1.76.0-r0 do_compile - 24m44s (pid 3578779)

2: kernel-devsrc-1.0-r0 do_install - 15m17s (pid 3619862)

3: gcc-11.1.0-r0 do_package_write_ipk - 1m23s (pid 3665048)

4: libcheck-0.15.2-r0 do_package_write_ipk - 32s (pid 3669480)

5: libsamplerate0-0.1.9-r1 do_package_write_ipk - 24s (pid 3669801)

[1]+ Stopped MACHINE=icicle-kit-es bitbake mpfs-dev-cli

real 328m42.945s

user 0m0.000s

sys 0m0.004s

jaufranc@cnx-laptop-4:~/edev/Microchip/yocto-dev/build$ Поскольку bitbake порождает так много других процессов, мы должны дождаться их завершения. Потребовалось около 10 минут, чтобы вернуться к обычному компьютеру.

Мы приостановили процесс примерно на 3 часа, а потом его можно возобновить командой «fg». Это похоже на режим гибернации для терминальных программ, и он существует всегда, но мы никогда не использовали его. Полная сборка на нашем устройстве заняла от 7 до 8 часов.

Это пространство, используемое Yocto BSP:

~/edev/Microchip/yocto-dev$ du --max-depth=1 -h

313M ./.repo

36M ./meta-openembedded

376K ./meta-polarfire-soc-yocto-bsp

6.3M ./meta-riscv

94G ./build

45M ./openembedded-core

94G .Мы можем найти образ в папке tmp-glibc/deploy/images/icicle-kit-es/:

ls -lh tmp-glibc/deploy/images/icicle-kit-es/

total 9.8G

-rwxr-xr-x 1 jaufranc jaufranc 1.3K Sep 26 18:06 boot.scr.uimg

lrwxrwxrwx 2 jaufranc jaufranc 68 Sep 26 18:07 fitImage -> fitImage--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.bin

-rw-r--r-- 2 jaufranc jaufranc 4.6M Sep 26 18:07 fitImage--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.bin

lrwxrwxrwx 2 jaufranc jaufranc 68 Sep 26 18:07 fitImage-icicle-kit-es.bin -> fitImage--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.bin

-rw-r--r-- 2 jaufranc jaufranc 1.7K Sep 26 18:08 fitImage-its--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.its

lrwxrwxrwx 2 jaufranc jaufranc 72 Sep 26 18:08 fitImage-its-icicle-kit-es -> fitImage-its--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.its

-rw-r--r-- 2 jaufranc jaufranc 4.6M Sep 26 18:08 fitImage-linux.bin--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.bin

lrwxrwxrwx 2 jaufranc jaufranc 78 Sep 26 18:08 fitImage-linux.bin-icicle-kit-es -> fitImage-linux.bin--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.bin

-rw-r--r-- 2 jaufranc jaufranc 11K Sep 26 18:08 microchip-mpfs-icicle-kit--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.dtb

lrwxrwxrwx 2 jaufranc jaufranc 85 Sep 26 18:08 microchip-mpfs-icicle-kit.dtb -> microchip-mpfs-icicle-kit--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.dtb

lrwxrwxrwx 2 jaufranc jaufranc 85 Sep 26 18:08 microchip-mpfs-icicle-kit-icicle-kit-es.dtb -> microchip-mpfs-icicle-kit--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.dtb

lrwxrwxrwx 2 jaufranc jaufranc 38 Sep 26 18:06 mmc-tftp-icicle-kit-es.txt -> mmc-tftp-icicle-kit-es-v2021.04-r0.txt

-rw-r--r-- 2 jaufranc jaufranc 1.2K Sep 26 18:06 mmc-tftp-icicle-kit-es-v2021.04-r0.txt

lrwxrwxrwx 2 jaufranc jaufranc 38 Sep 26 18:06 mmc-tftp.txt -> mmc-tftp-icicle-kit-es-v2021.04-r0.txt

-rw-r--r-- 2 jaufranc jaufranc 1.6M Sep 26 18:08 modules--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.tgz

lrwxrwxrwx 2 jaufranc jaufranc 67 Sep 26 18:08 modules-icicle-kit-es.tgz -> modules--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.tgz

-rw-r--r-- 2 jaufranc jaufranc 5.1K Sep 27 09:29 mpfs-dev-cli.env

-rw-r--r-- 2 jaufranc jaufranc 5.4G Sep 27 09:46 mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.ext4

-rw-r--r-- 2 jaufranc jaufranc 103K Sep 27 09:27 mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.manifest

-rw-r--r-- 2 jaufranc jaufranc 5.5G Sep 27 09:50 mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.wic

-rw-r--r-- 2 jaufranc jaufranc 1.4G Sep 27 09:58 mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.wic.gz

-rw-r--r-- 2 jaufranc jaufranc 225K Sep 27 09:27 mpfs-dev-cli-icicle-kit-es-20210927021251.testdata.json

lrwxrwxrwx 2 jaufranc jaufranc 53 Sep 27 09:46 mpfs-dev-cli-icicle-kit-es.ext4 -> mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.ext4

lrwxrwxrwx 2 jaufranc jaufranc 57 Sep 27 09:27 mpfs-dev-cli-icicle-kit-es.manifest -> mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.manifest

lrwxrwxrwx 2 jaufranc jaufranc 55 Sep 27 09:27 mpfs-dev-cli-icicle-kit-es.testdata.json -> mpfs-dev-cli-icicle-kit-es-20210927021251.testdata.json

lrwxrwxrwx 2 jaufranc jaufranc 52 Sep 27 09:58 mpfs-dev-cli-icicle-kit-es.wic -> mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.wic

lrwxrwxrwx 2 jaufranc jaufranc 55 Sep 27 09:58 mpfs-dev-cli-icicle-kit-es.wic.gz -> mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.wic.gz

-rwxr-xr-x 1 jaufranc jaufranc 477K Sep 26 22:30 payload.bin

lrwxrwxrwx 2 jaufranc jaufranc 36 Sep 26 18:06 u-boot.bin -> u-boot-icicle-kit-es-v2021.04-r0.bin

lrwxrwxrwx 2 jaufranc jaufranc 36 Sep 26 18:06 u-boot-icicle-kit-es.bin -> u-boot-icicle-kit-es-v2021.04-r0.bin

-rw-r--r-- 2 jaufranc jaufranc 476K Sep 26 18:06 u-boot-icicle-kit-es-v2021.04-r0.bin

lrwxrwxrwx 2 jaufranc jaufranc 49 Sep 26 18:06 u-boot-mpfs-initial-env -> u-boot-mpfs-initial-env-icicle-kit-es-v2021.04-r0

lrwxrwxrwx 2 jaufranc jaufranc 49 Sep 26 18:06 u-boot-mpfs-initial-env-icicle-kit-es -> u-boot-mpfs-initial-env-icicle-kit-es-v2021.04-r0

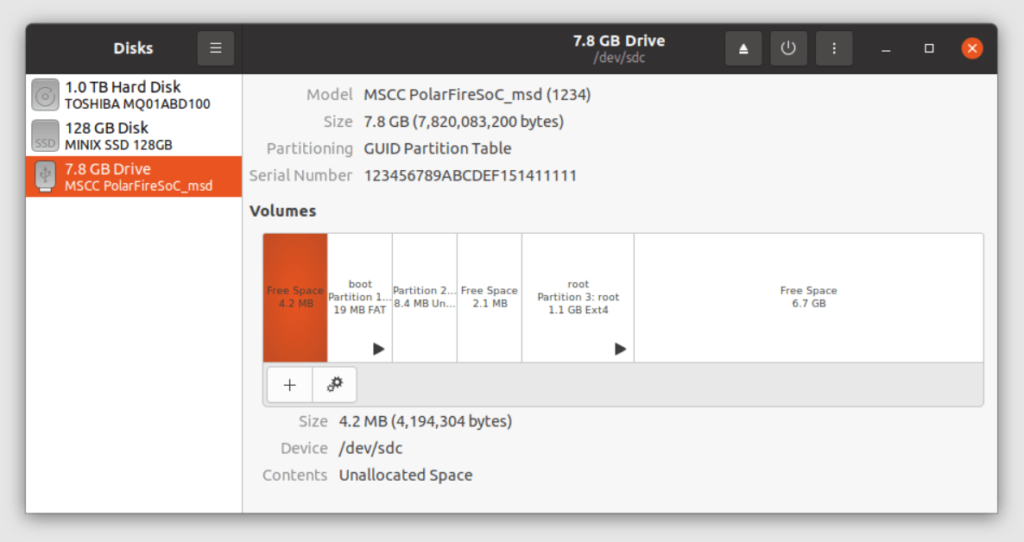

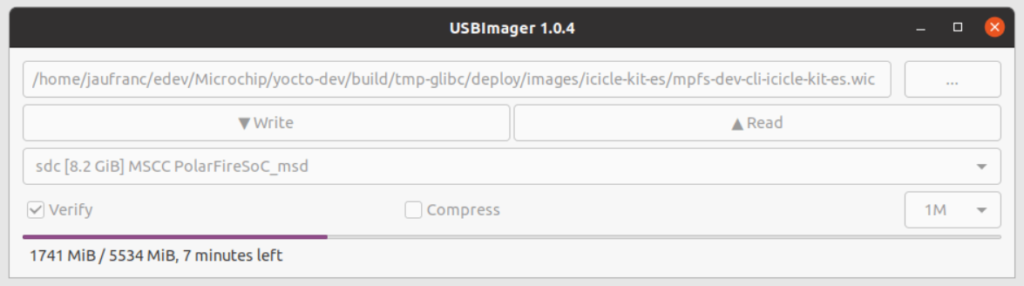

-rw-r--r-- 2 jaufranc jaufranc 3.2K Sep 26 18:06 u-boot-mpfs-initial-env-icicle-kit-es-v2021.04-r0Несжатый образ имеет размер 5,5 ГБ, поэтому его можно разместить на SD-карте 8 ГБ, но рекомендуются карты 16 ГБ или 32 ГБ. Это команда Microchip для прошивки на SD-карту:

zcat tmp-glibc/deploy/images/icicle-kit-es/mpfs-dev-cli-icicle-kit-es.wic.gz | sudo dd of=/dev/sdX bs=4096 iflag=fullblock oflag=direct conv=fsync status=progress

Но если вам нужна проверка образа, предпочтительнее использовать такие утилиты, как USBImager. Это то, что мы использовали для прошивки образа на SD-карту емкостью 32 ГБ, которую затем вставили в слот для SD-карты.

Прервем загрузку, чтобы проверить, обнаружена ли SD-карта:

U-Boot 2021.04 (Sep 26 2021 - 09:16:21 +0000)

CPU: rv64imafdc

Model: Microchip MPFS Icicle Kit

DRAM: 2 GiB

MMC: mmc@20008000: 0

In: serial@20100000

Out: serial@20100000

Err: serial@20100000

Net: eth0: ethernet@20112000

Hit any key to stop autoboot: 0

RISC-V # mmcinfo

Device: mmc@20008000

Manufacturer ID: 0

OEM: 3432

Name: SD16G

Bus Speed: 50000000

Mode: SD High Speed (50MHz)

Rd Block Len: 512

SD version 3.0

High Capacity: Yes

Capacity: 29.1 GiB

Bus Width: 4-bit

Erase Group Size: 512 BytesВсе хорошо, идем дальше… но не получается переключиться на ядро. В конце концов мы пересохранили образ, используя несжатый двоичный файл, и смогли войти в терминал:

root@icicle-kit-es:~# uname -a

Linux icicle-kit-es 5.12.1 #1 SMP Sun Sep 26 08:45:19 UTC 2021 riscv64 riscv64 riscv64 GNU/Linux

root@icicle-kit-es:~# df -g

df: invalid option -- 'g'

Try 'df --help' for more information.

root@icicle-kit-es:~# df -f

df: invalid option -- 'f'

Try 'df --help' for more information.

root@icicle-kit-es:~# df -h

Filesystem Size Used Avail Use% Mounted on

/dev/root 5.2G 4.2G 733M 86% /

devtmpfs 817M 0 817M 0% /dev

tmpfs 818M 0 818M 0% /dev/shm

tmpfs 327M 9.5M 318M 3% /run

tmpfs 4.0M 0 4.0M 0% /sys/fs/cgroup

tmpfs 818M 0 818M 0% /tmp

tmpfs 818M 100K 818M 1% /var/volatile

tmpfs 164M 0 164M 0% /run/user/0

root@icicle-kit-es:~# fdisk -l

GPT PMBR size mismatch (11334293 != 61067263) will be corrected by write.

The backup GPT table is not on the end of the device.

Disk /dev/mmcblk0: 29.12 GiB, 31266439168 bytes, 61067264 sectors

Units: sectors of 1 * 512 = 512 bytes

Sector size (logical/physical): 512 bytes / 512 bytes

I/O size (minimum/optimal): 512 bytes / 512 bytes

Disklabel type: gpt

Disk identifier: 707A61C6-0BE8-405E-BF47-9E8071F3EEC9

Device Start End Sectors Size Type

/dev/mmcblk0p1 8192 47009 38818 19M Microsoft basic data

/dev/mmcblk0p2 47010 63393 16384 8M BIOS boot

/dev/mmcblk0p3 65536 11334259 11268724 5.4G Linux filesystemРазмер rootfs не был изменен автоматически, и, похоже, возникла проблема с таблицей GPT… Мы не совсем понимаем, что произошло. Но поскольку наш самодельный образ работает, и у нас есть флеш-память eMMC, давайте сохраним его во внутреннее хранилище.

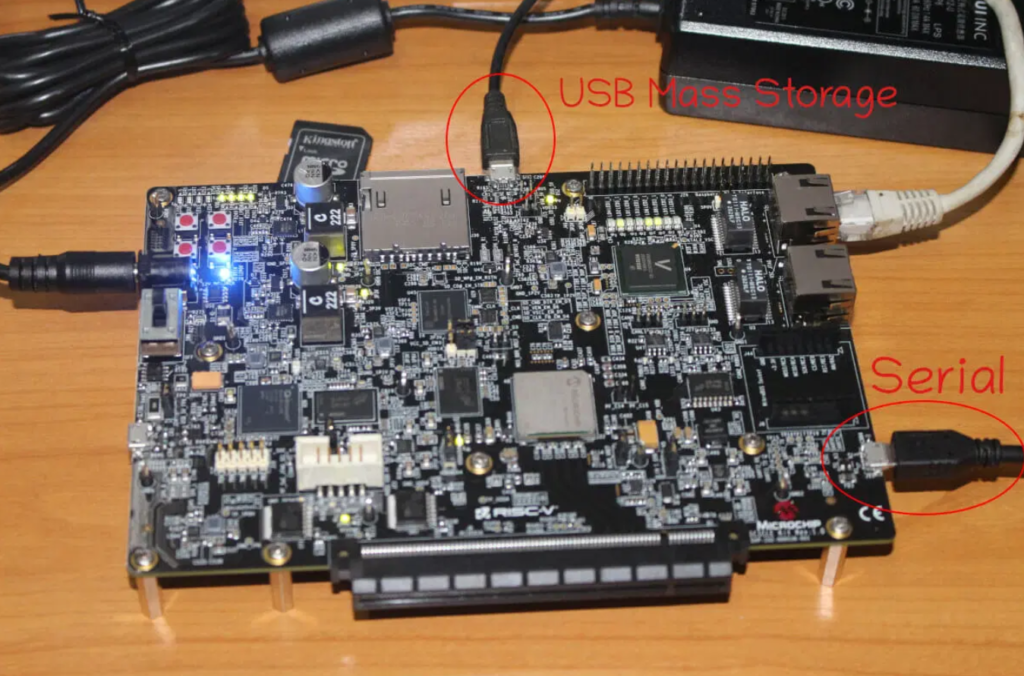

Выключите плату, извлеките SD-карту и подключитесь к ttyUSB0 с помощью Bootterm, чтобы получить доступ к терминалу HSS:

bt ttyUSB0

Перед перезапуском платы, прервав загрузку, введите «usbdmsc», чтобы открыть флэш-память eMMC в качестве USB-накопителя для ноутбука с Ubuntu.

[5.623947] HSS_MMCInit(): Attempting to select eMMC ... Passed

Press a key to enter CLI, ESC to skip

Timeout in 5 seconds

.[6.915522] HSS_ShowTimeout(): Character 32 pressed

[6.921945] HSS_TinyCLI_Parser(): Type HELP for list of commands

[6.929236] HSS_TinyCLI_Parser(): >> usbdmsc

[27.703151] HSS_TinyCLI_Execute(): Unknown command >><<.

[27.710094] HSS_TinyCLI_Parser(): >> usbdmsc

[37.207116] HSS_MMCInit(): Attempting to select SDCARD ... [38.215220] mmc_init_common(): MSS_MMC_init() returned unexpected 0

Failed

[38.223900] HSS_MMCInit(): Attempting to select eMMC ... Passed

Waiting for USB Host to connect... (CTRL-C to quit)

USB Host connected. Waiting for disconnect... (CTRL-C to quit)

664064 bytes written, 21166080 bytes read

Нам понадобится еще один кабель Micro USB, подключенный к порту Micro USB J16, чтобы увидеть флешку в Ubuntu.

Мы можем отключить загрузочный и корневой разделы перед прошивкой образа, как мы это сделали для SD-карты. Сначала мы попытались использовать образ gz, но у нас возникла та же проблема, что и с SD-картой. Корневой раздел не удалось смонтировать даже на ПК, поэтому мы выбрали несжатый образ, и все прошло гладко.

После завершения мы можем отсоединить кабель micro USB, подключенный к J16, и получить доступ к нашему образу Linux …

jaufranc@cnx-laptop-4:~/edev/Microchip/yocto-dev/build$ bt ttyUSB1

Trying port ttyUSB1... Connected to ttyUSB1 at 115200 bps.

Escape character is 'Ctrl-]'. Use escape followed by '?' for help.

icicle-kit-es login: root

root@icicle-kit-es:~# uname -a

Linux icicle-kit-es 5.12.1 #1 SMP Sun Sep 26 08:45:19 UTC 2021 riscv64 riscv64 riscv64 GNU/Linux

root@icicle-kit-es:~# df -h

Filesystem Size Used Avail Use% Mounted on

/dev/root 5.2G 4.2G 733M 86% /

devtmpfs 817M 0 817M 0% /dev

tmpfs 818M 0 818M 0% /dev/shm

tmpfs 327M 9.6M 318M 3% /run

tmpfs 4.0M 0 4.0M 0% /sys/fs/cgroup

tmpfs 818M 0 818M 0% /tmp

tmpfs 818M 100K 818M 1% /var/volatile

tmpfs 164M 0 164M 0% /run/user/0

root@icicle-kit-es:~# Кросс-компиляция «Hello World»

Попробуем кросс-скомпилировать программу «Hello World»

#include <stdio.h>

int main() {

printf("Hello, World!\n");

return 0;

}для RISC-V с помощью набора инструментов Yocto, который мы сначала добавим к нашему пути:

export PATH=$PATH:~/edev/Microchip/yocto-dev/build/tmp-glibc/sysroots-components/x86_64/gcc-cross-riscv64/usr/bin/riscv64-oe-linuxи используем инструмент RISCV GCC для его создания:

riscv64-oe-linux-gcc hello.c -o hello

hello.c:1:10: fatal error: stdio.h: No such file or directory

1 | #include <stdio.h>

| ^~~~~~~~~

compilation terminated.К сожалению, это не работает должным образом. Похоже, что набор инструментов установлен неправильно, или мы использовали не тот инструмент. Мы пытались поработать с CFLAGS, но не повезло … Может, он должен работать только в рамках Yocto/Bitbake … У нас есть опыт работы с buildroot, и обычно инструментальная цепочка кросс-компиляции работает из коробки.

Тест EEMBC CoreMark

Построим EEMBC CoreMark прямо на плате. Созданный нами образ поставляется с git и набором инструментов GNU GCC, поэтому он должен быть простым.

https://github.com/eembc/coremark

cd coremark/

make -j4Это и создает, и запускает CoreMark с двумя сгенерированными файлами.

- run1.log

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 14935

Total time (secs): 14.935000

Iterations/Sec : 1339.136257

Iterations : 20000

Compiler version : GCC11.1.0

Compiler flags : -O2 -DPERFORMANCE_RUN=1 -lrt

Memory location : Please put data memory location here

(e.g. code in flash, data on heap etc)

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0x382f

Correct operation validated. See README.md for run and reporting rules.

CoreMark 1.0 : 1339.136257 / GCC11.1.0 -O2 -DPERFORMANCE_RUN=1 -lrt / Heap- run2.log

2K validation run parameters for coremark.

CoreMark Size : 666

Total ticks : 14907

Total time (secs): 14.907000

Iterations/Sec : 1341.651573

Iterations : 20000

Compiler version : GCC11.1.0

Compiler flags : -O2 -DPERFORMANCE_RUN=1 -lrt

Memory location : Please put data memory location here

(e.g. code in flash, data on heap etc)

seedcrc : 0x18f2

[0]crclist : 0xe3c1

[0]crcmatrix : 0x0747

[0]crcstate : 0x8d84

[0]crcfinal : 0xd304

Correct operation validated. See README.md for run and reporting rules.Плата набрала 1339,136257 баллов, или около 2,23 CoreMark/МГц, поскольку ядра RISC-V работают на частоте 600 МГц. Но Microchip сообщает на плате 3,25 CoreMark/МГц. Давайте попробуем еще раз с теми же флагами, которые использует компания:

make clean

make XCFLAGS="-O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=0 -mtune=sifive-7-series"

Это содержимое run1.log:

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 12874295

Total time (secs): 12

Iterations/Sec : 1666

Iterations : 20000

Compiler version : GCC11.1.0

Compiler flags : -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=0 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt

Memory location : Please put data memory location here

(e.g. code in flash, data on heap etc)

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0x382f

Correct operation validated. See README.md for run and reporting rules.Почему-то результат CoreMark нигде нельзя найти, но у нас все еще есть количество итераций в секунду, которое увеличилось с 1341,651573 до 1666. Так что оно улучшилось. Взглянув на код, легко понять, почему рейтинг не отображается:

ee_printf(

"Correct operation validated. See README.md for run and reporting "

"rules.\n");

#if HAS_FLOAT

if (known_id == 3)

{

ee_printf("CoreMark 1.0 : %f / %s %s",

default_num_contexts * results[0].iterations

/ time_in_secs(total_time),

COMPILER_VERSION,

COMPILER_FLAGS);Давайте повторим это с -DHAS_FLOAT = 1…

make clean make XCFLAGS="-O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=1 -mtune=sifive-7-series"

На этот раз все выглядит правильно:

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 12842191

Total time (secs): 12.842191

Iterations/Sec : 1557.366652

Iterations : 20000

Compiler version : GCC11.1.0

Compiler flags : -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=1 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt

Memory location : Please put data memory location here

(e.g. code in flash, data on heap etc)

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0x382f

Correct operation validated. See README.md for run and reporting rules.

CoreMark 1.0 : 1557.366652 / GCC11.1.0 -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=1 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt / Heap

Но это всего лишь 2,59 CoreMark/МГц, все еще не до 3,125 CoreMark/МГц. Фактически, он соответствует результатам Microchip с использованием беззнакового индекса. Кто-то пытался сделать то же самое, и ему посоветовали изменить код в posix/core_portme.h, чтобы использовать индекс со знаком:

typedef signed int ee_u32;После повторного запуска теста результат стал еще выше:

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 16767651

Total time (secs): 16.767651

Iterations/Sec : 1789.159376

Iterations : 30000

Compiler version : GCC11.1.0

Compiler flags : -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=1 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt

Memory location : Please put data memory location here

(e.g. code in flash, data on heap etc)

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0x5275

Correct operation validated. See README.md for run and reporting rules.

CoreMark 1.0 : 1789.159376 / GCC11.1.0 -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=1 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt / Heap

1789,159376 CoreMark соответствует примерно 2,98 CoreMark МГц. Мы можем окончательно взломать устройство, определив HAS_FLOAT = 0 в командной строке make. Результат будет следующим:

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 16694339

Total time (secs): 16

Iterations/Sec : 1875

Iterations : 30000

Compiler version : GCC11.1.0

Compiler flags : -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=0 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt

Memory location : Please put data memory location here

(e.g. code in flash, data on heap etc)

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0x5275

Correct operation validated. See README.md for run and reporting rules.Если использовать результат Iterations/Sec: 1875 в качестве значения CoreMark 1.0, и в этом случае мы действительно можем достичь точно 3,125 CoreMark/MHz, как это сделал Microchip для использования индекса со знаком. У нас нет уверенности в том, почему signed намного быстрее, чем unsigned … и нам нужно будет посмотреть на сборку и проверить количество циклов для каждой инструкции, чтобы узнать.

Но все это показывает, как можно настраивать/манипулировать тестами для достижения лучших результатов, а также важность флагов компиляции для оптимизации кода. Веб-страница аналитики напряжения/тока не показала каких-либо значительных изменений во время тестирования.

На сегодня это все, а через несколько недель мы, надеемся, опубликуем что-нибудь о FPGA. Кто-то попросил нас оценить стандартизированный интерфейс virt-io по шине PCI-e, но из-за нехватки времени мы не смогли этого сделать. Мы задали это вопрос представителям компании Microchip и нам ответили, что все должно работать, но они не тестировали его …

Если вас интересует плата, ее можно приобрести у различных дистрибьюторов, таких как Mouser, по цене менее 500 долларов.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.