В прошлом году компания Andes представила ядра RISC-V AndesCore 27-серии, поддерживающие Linux, с блоком векторной обработки для ускорения ИИ, в частности 32-битными ядрами A27 и 64-битными AX27. Примерно в то же время компания представила более дорогую серию AndesCore 45 (A45 и AX45), но мы почему-то пропустили анонс.

Теперь компания Andes добавила больше RISC-V AndesCore с поддержкой Linux к вышеупомянутым семействам с высокопроизводительными суперскалярными многоядерными процессорами A45MP и AX45MP, а также процессорами A27L2 и AX27L2 с контроллером кэш-памяти второго уровня.

Ядра Andes A27L2 и AX27L2

Основываясь на основных характеристиках, можно сказать, что новые ядра выглядят идентично ядрам A27 и AX27L2, анонсированным в прошлом году, за исключением дополнительного кэша L2, который поставляется с опциональным ECC.

Основные характеристики и спецификации AndesCores A27L2 и AX27L2:

- AX27L2 — 64-разрядная 5-ступенчатая конвейерная архитектура ЦП (RV64GCPN), позволяющая программному обеспечению использовать пространства памяти, превышающие 4 ГБ

- A27L2 – 32-битная 5-ступенчатая конвейерная архитектура ЦП (RV32GCPN)

- Архитектура набора команд AndeStar V5 (ISA), совместимая с технологией RISC-V

- Расширения с плавающей точкой

- DSP/SIMD ISA для повышения производительности обработки голоса, звука, изображения и сигналов

- Расширения Andes, спроектированные для повышения производительности и функциональности

- Отдельно лицензируемое расширение Andes Custom Extension (ACE) для индивидуального ускорения

- 16/32-битный смешиваемый формат инструкций для уплотнения плотности кода

- Прогнозирование ветвления для ускорения управляющего кода

- Стек обратных адресов (RAS) для ускорения процедуры возврата

- Блок управления памятью (MMU), защита физической памяти (PMP) и

- Программируемые атрибуты физической памяти (PMA)

- Контроллеры кэша 1 и 2 уровней с размером строки кэша 64 байта

- MemBoost для тяжелых транзакций с памятью

- Гибко настраиваемый контроллер прерываний на уровне платформы (PLIC) для поддержки широкого спектра сценариев системных событий

- Улучшение обработки векторных прерываний для работы в реальном времени

- Усовершенствованная технология CoDense для дальнейшего уменьшения размера кода поверх расширения «C»

Кэш L2 позволяет удвоить пропускную способность памяти и снижает задержку памяти на 70%.

Многоядерные процессоры RISC-V Andes A45MP и AX45MP

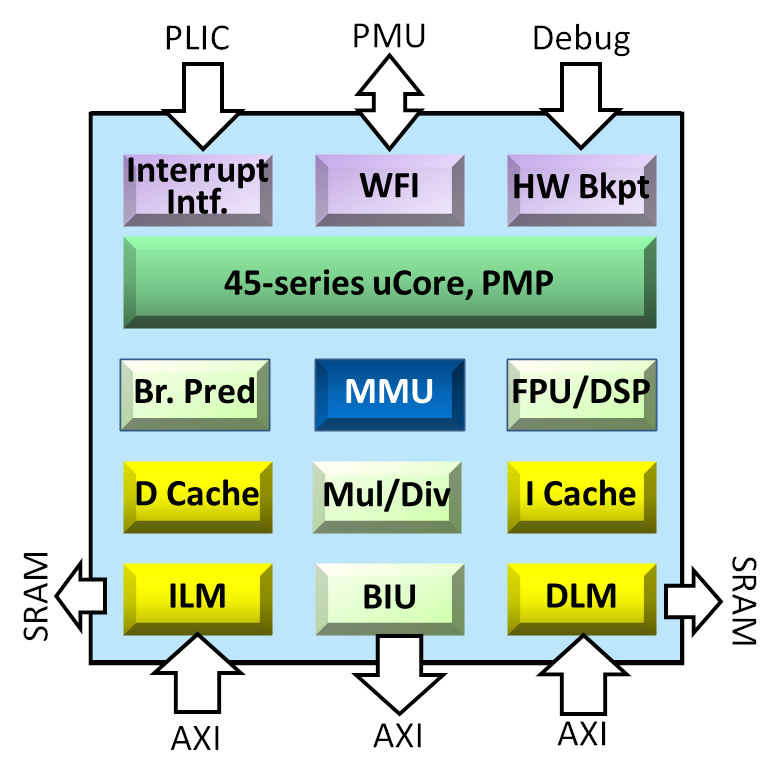

Компания Andes не добавляла страницы продуктов для новых ядер A45MP и AX45MP, но, исходя из информации, известной из более раннего пресс-релиза ядер A45 и AX45, ядра A45MP и AX45MP должны иметь следующие ключевые особенности:

- AX45MP – 64-разрядная восьмиступенчатая конвейерная архитектура ЦП с двумя последовательными выпусками (RV64GCPN), поддерживающая кластеры до 4 ядер

- A45MP – 32-разрядная 8-ступенчатая конвейерная архитектура ЦП с двумя последовательными выпусками (RV32GCPN), поддерживающая кластеры до 4 ядер

- Архитектура набора команд AndeStar V5 (ISA), совместимая с технологией RISC-V

- Расширения DSP / SIMD

- Расширения с плавающей точкой

- Расширения Andes, спроектированные для повышения производительности и функциональности

- 16/32-битный смешиваемый формат инструкций для уплотнения плотности кода

- Расширенное предсказание переходов с низким энергопотреблением для ускорения управляющего кода

- Стек обратных адресов (RAS) для ускорения возврата из процедуры

- Блок управления памятью (MMU), защита физической памяти (PMP) и программируемый атрибут физической памяти (PMA)

- Дополнительный контроллер кеш-памяти L2

- MemBoost для тяжелых транзакций с памятью

- Гибко настраиваемый контроллер прерываний на уровне платформы (PLIC) для поддержки широкого спектра сценариев системных событий

- Улучшение обработки векторных прерываний для работы в реальном времени

- Передовая технология CoDense для уменьшения размера программного кода

Это означает, что новые ядра A45MP и AX45MP получат поддержку многоядерных процессоров и опционального кэша L2 и, как ожидается, будут использоваться в SoC в «тяжелых» приложениях, таких как AR/VR,AI/машинное обучение, 5G, In -Vehicle Infotainment (IVI), Advanced Driver Assistance Systems (ADAS), обработка видео/изображений, запоминающее устройство корпоративного уровня и сеть.

Более подробную информацию вы найдете на странице процессоров AndesCore компании Andes. Прямо сейчас открыты только страницы A27L2 и AX27L2, но вскоре компания должна добавить больше деталей о новых многоядерных ядрах 45-й серии.

Выражаем свою благодарность источнику их которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.