Открытая архитектура RISC-V попала в недорогие универсальные микроконтроллеры общего назначения, такие как Gigadevices GD32V или WCH CH32V103, жесткие диски Western Digital, некоторые процессоры AI, в частности Kendryte K210, и даже платы с поддержкой Linux, включая комплект Microsemi PolarFire SoC Icicle.

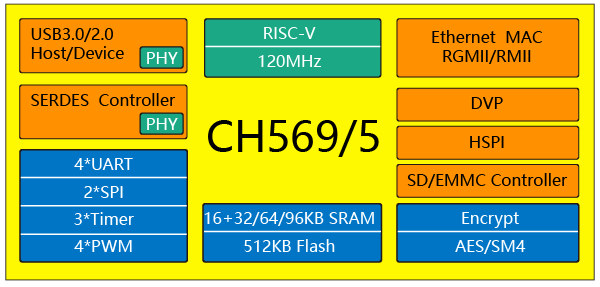

Но все больше приложений с архитектурой RISC-V поставляются, например, с процессором WCH CH569 RISC-V с USB 3.0, Gigabit Ethernet, DVP-камерой и блоком 1,25 SERDES, управляемые ядром RISC-V с тактовой частотой 120 МГц.

Основные характеристики и спецификации процессора CH569 (и CH565):

- CPU — ядро RISC-V (RISC-V3A) @ 120 МГц с аппаратным умножением и делением, программируемый контроллер прерываний, двухступенчатый конвейер с низким энергопотреблением

- Память – 32-битная SRAM 16 КБ, конфигурируемая 128-битная SRAM 32/64/96 КБ

- Хранилище

- Внутреннее — 448 КБ флэш-память, флэш-память 32 КБ

- Внешнее — контроллер SD/eMMC с однопроводным, 4-проводным, 8-проводным режимом передачи данных. Соответствует спецификациям карт eMMC 4.4 и 4.5.1 и совместим со спецификациями 5.0

- Сеть — Gigabit Ethernet контроллер с интерфейсами RGMII и RMII PHY

- USB

- Сверхскоростной USB3.0 хост/устройство PHY с поддержкой OTG

- Высокоскоростной USB 2.0 хост/устройство PHY

- Другие высокоскоростные интерфейсы

- 8/16/32-битный HSPI высокоскоростной параллельный интерфейс со встроенным FIFO, поддержкой DMA для скорости передачи до 3,8 Гбит / с

- SERDES PHY (например, для оптического волокна) до 1,25 Гбит / с

- Камера — 8/10/12-битный цифровой видеоинтерфейс (DVP) со сжатыми данными YUV, RGB или JPEG

- Другие входы / выходы и периферийные устройства

- 4x UART до 6 Мбит/с

- 2x интерфейс SPI ведущий / ведомый

- 4x PWM

- 49x GPIO, у 8 из них можно установить уровень прерываний

- Активный параллельный порт с 8-битными данными, 15-битная адресная шина

- 3x 26-битных таймера с поддержкой вывода PWM-модуляции

- Встроенный сторожевой таймер

- Безопасность — шифрование и дешифрование AES/SM4, шифрование и дешифрование данных периферийного интерфейса SRAM/EMMC/HSPI

- Разное — уникальный 64-битный идентификационный номер (Chip ID)

- Корпус — QFN68, QFN40

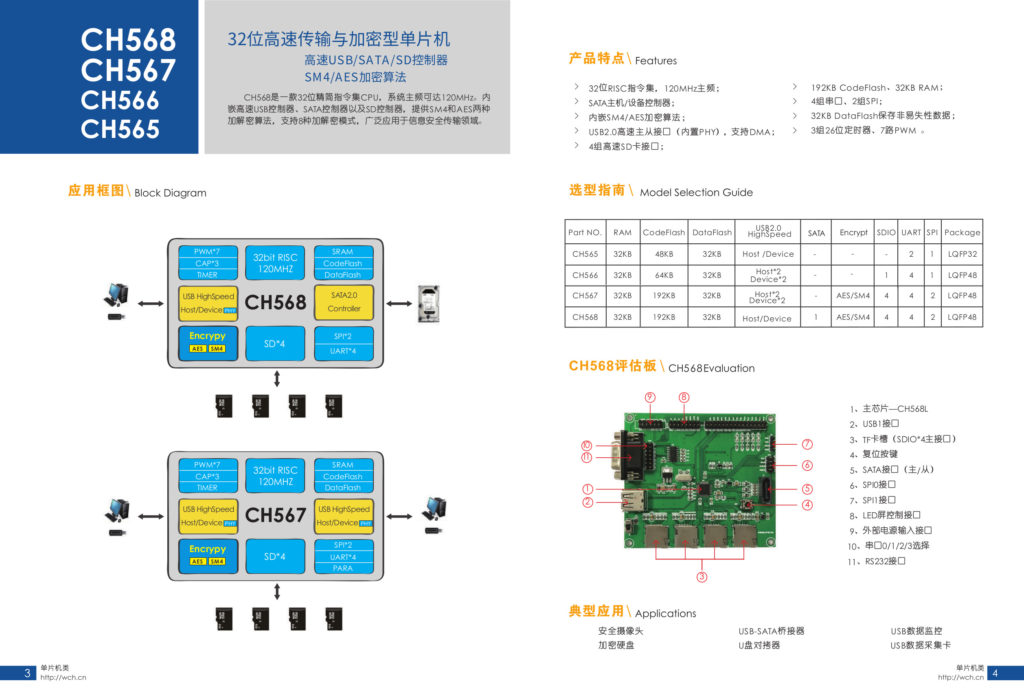

CH569, по-видимому, является первой процессорной частью RISC-V семейства WCH CH56x процессоров RISC (примечание: здесь без V) для приложений сетевого хранения с CH565, CH566, CH567 и CH568, предлагающими сочетание Ethernet, SATA, USB 2.0 и другими интерфейсами. Все чипы поставляются с тем же процессором RISC 120 МГц и только 32 КБ ОЗУ (128-битная), но компания утверждает, что 128-битный процессор DMA может передавать большой объем данных.

Что немного сбивает с толку, так это то, что первая блок-схема в обзоре выглядит как для CH569, так и для CH565, поэтому можно подумать, что все CH56x основаны на одном и том же ядре RISC-V на частоте 120 МГц, но есть информация, что CH568 основан на ядре Andes NDS32. Типичные сферы применения CH569, перечисленные компанией, включают потоковую передачу мультимедиа, сетевое хранилище, сверхскоростной USB3.0 FIFO, расширение связи, мониторинг безопасности и многое другое.

На данный момент доступно очень мало информации, и все на китайском языке на странице продукта, но, вы можете запросить дополнительную информацию и образцы.

Выражаем свою благодарность источнику их которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.