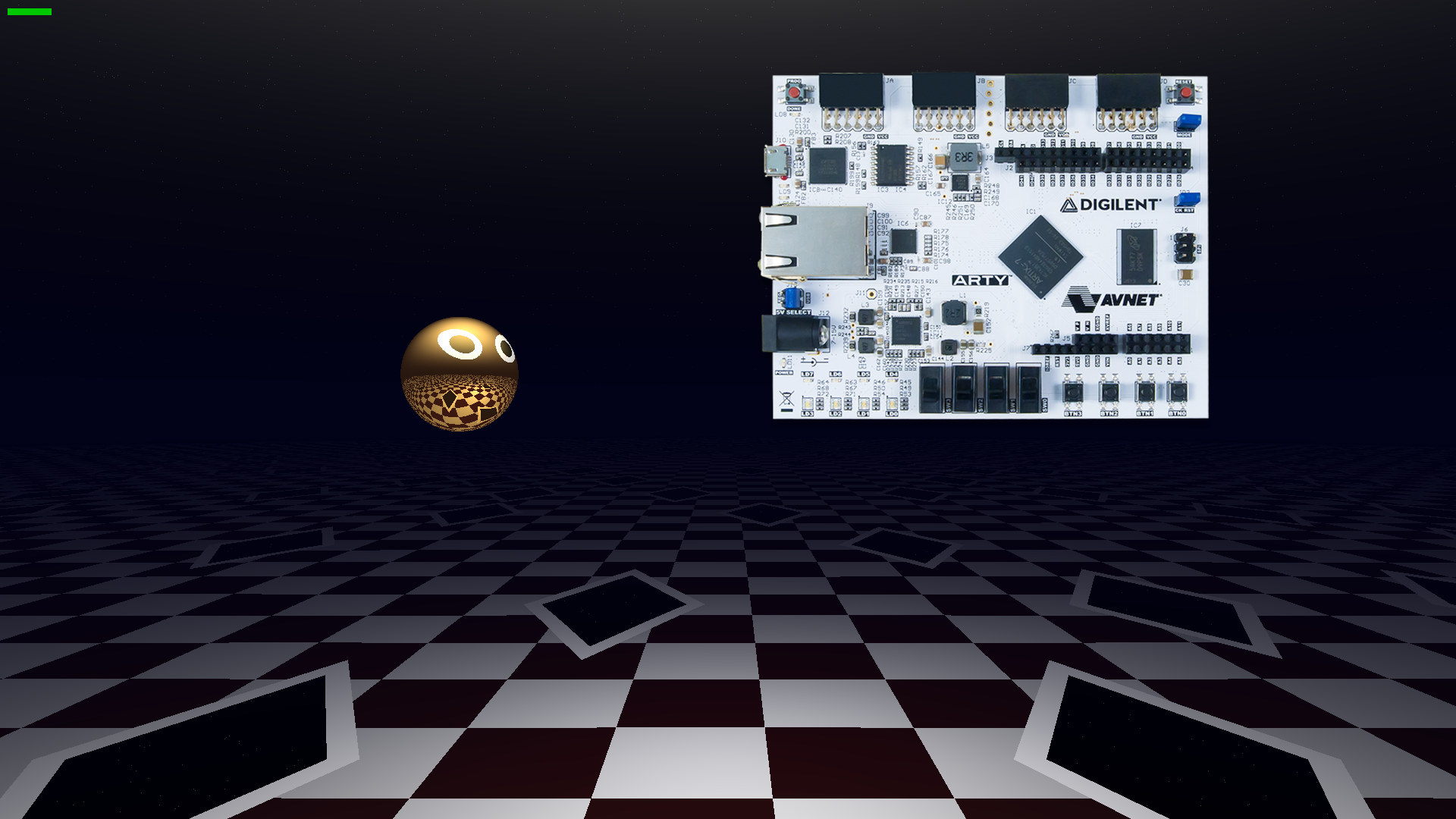

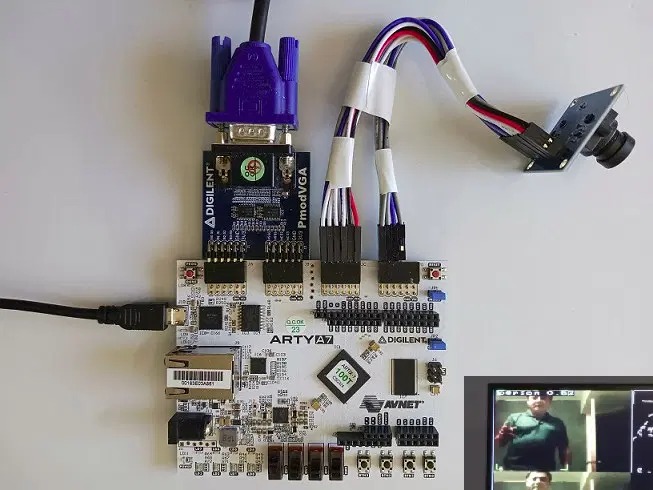

Sphery vs. shapes — это открытая 3D-игра с трассировкой лучей, написанная на C и преобразованная в битстрим для FPGA, которая работает в 50 раз эффективнее на FPGA, чем на процессоре AMD Ryzen.

Языки Verilog и VHDL, традиционно используемые для FPGA, плохо подходят для разработки игр или других сложных приложений, поэтому Victor Suarez Rovere и Julian Kemmerer использовали язык описания аппаратуры (HDL), похожий на C, под названием PipelineC от Julian, а также инструмент CflexHDL от Victor, включающий парсер/генератор и библиотеку математических типов. Это позволило запускать один и тот же код на ПК с помощью стандартной компиляции и на FPGA через пользовательский транслятор C в VHDL.