Leopard Imaging LI-IMX530-10GigE-NL представляет собой высококачественную 25-мегапиксельную камеру с глобальным затвором, разработанную специально для периферийной ИИ-платформы NVIDIA Holoscan. Камера использует интерфейс 10GbE для передачи данных с высокой пропускной способностью и низкой задержкой, что делает её подходящей для распознавания жестов, сканирования радужной оболочки, определения наклона головы и отслеживания взгляда.

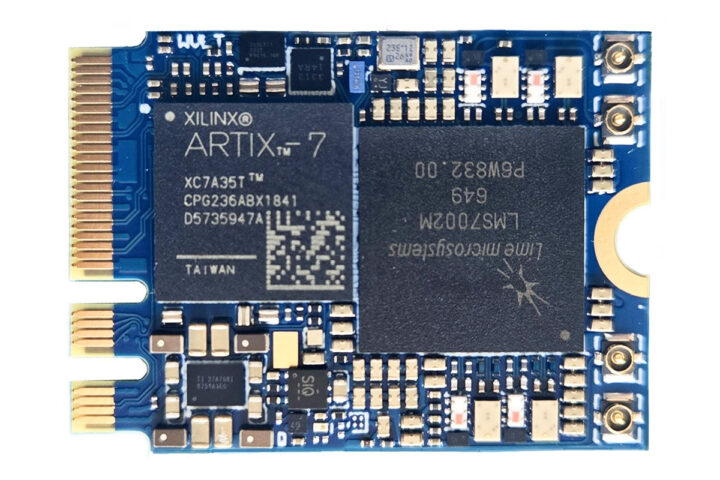

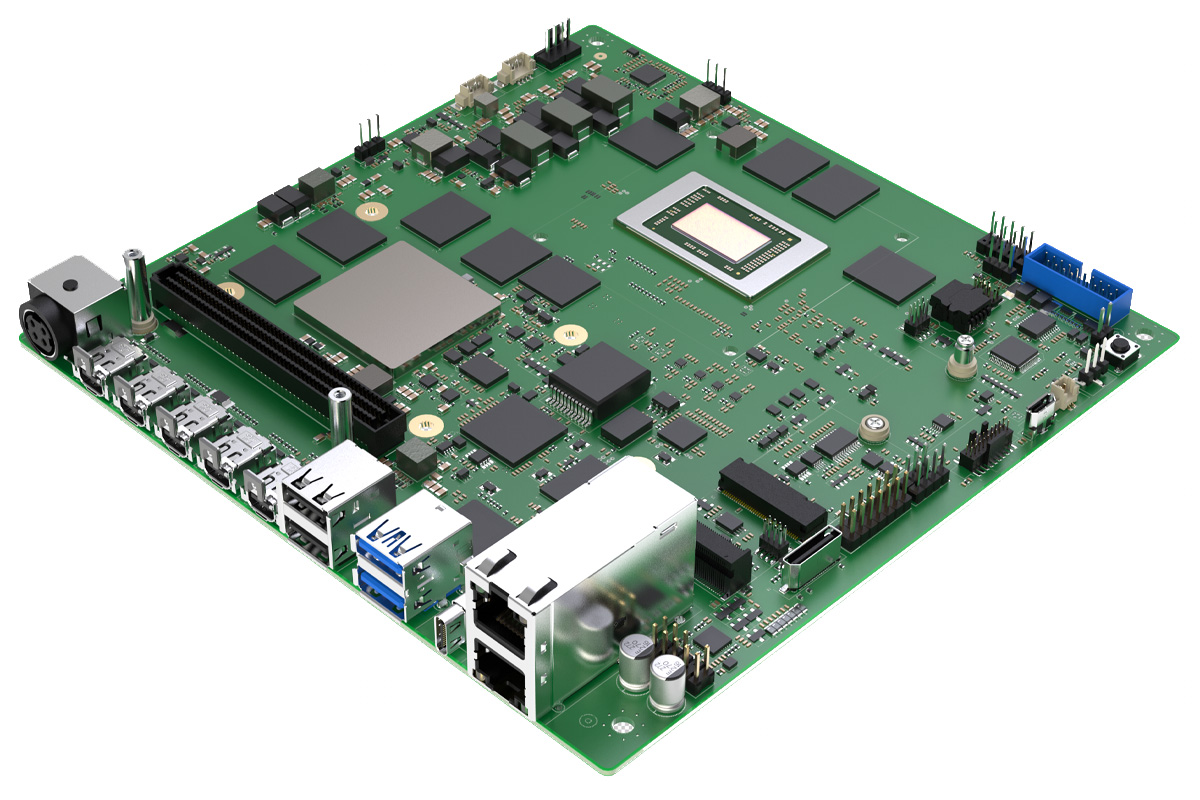

В основе модуля камеры лежит сенсор Sony IMX530 — КМОП-матрица формата 1,2 дюйма с разрешением 5328 × 4608 и размером пикселя 2,74 мкм. Данные с сенсора обрабатываются ПЛИС Lattice CertusPro-NX, а за передачу данных с высокой пропускной способностью на системы с GPU отвечает PHY Marvell 10GbE. Камера поддерживает платформы NVIDIA Jetson AGX Orin , IGX Orin и Thor .