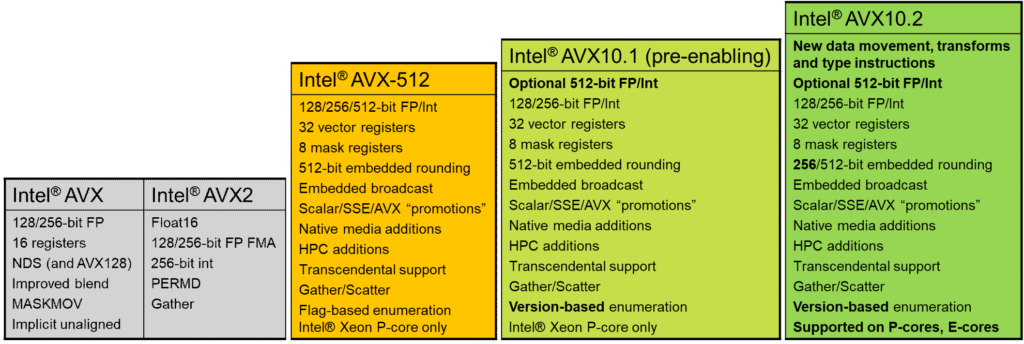

Инструкции Intel AVX10 SIMD заменят инструкции AVX-512, а AVX10.2 добавит поддержку процессоров Intel с E-ядром, чтобы обеспечить ускорение мультимедиа и искусственного интеллекта для ядер с низким энергопотреблением, в то время как более ранняя версия AVX10.1 добавит перечисление на основе версий и сделает 512-битные инструкции необязательны, но работают только с процессорами Intel (Xeon) с P- ядром.

Новая архитектура Intel Advanced Vector Extensions 10 (AVX10) была представлена в обновлении Advanced Performance Extensions (Intel APX), обеспечивая поддержку, подобную AVR-512, для новых гибридных процессоров с P-ядрами и E-ядрами, а также потенциально их версии начального уровня только с E-ядрами.

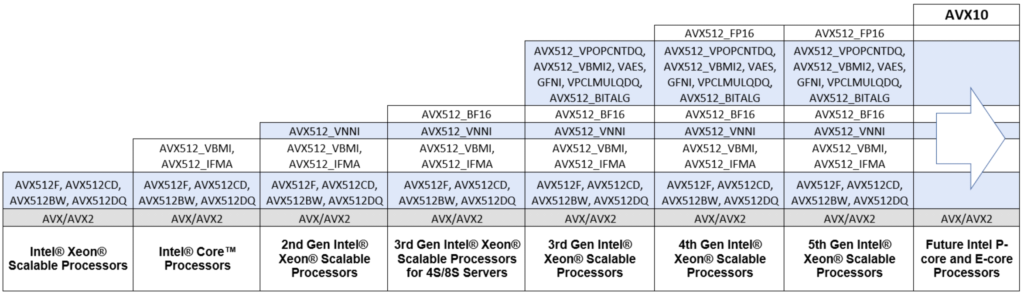

Intel объясняет, что новая архитектура SIMD включает в себя все возможности и функции Intel AVX-512 ISA, как для процессоров с максимальным размером векторных регистров 256 бит, так и для процессоров с 512-битными векторными регистрами. AVX10 ISA добавляет новую схему перечисления на основе версий, которая уменьшает количество флагов функций CPUID, которые необходимо проверять для поддержки функций. Как упоминалось выше, AVX10 работает как с процессорами P-core, так и с процессорами E-core, в то время как AVX-512 может быть реализован только на ядрах Performance.

Как указано в техническом документе, сопровождающем объявление, Intel решила работать над новой SIMD ISA по трем основным причинам:

- Чтобы продолжать поддерживать высокую производительность, вектор ISA со всеми функциями существующей Intel AVX-512 ISA.

- Создать конвергентную векторную ISA на основе Intel AVX-512, которая будет поддерживаться всеми будущими процессорами Intel.

- Чтобы упростить задачу разработчика по проверке поддержки функции CPUID.

Если я правильно понимаю, AVX10 будет реализован на всех будущих процессорах Intel, и это может быть необязательно, как AVX-512 ISA, но это должно быть подтверждено.

Intel дополнительно разъясняет, что конвергентная версия векторной Intel AVX10 ISA будет включать векторные инструкции Intel AVX-512 с флагом функции AVX512VL, максимальную длину векторного регистра в 256 бит, а также восемь 32-разрядных регистров масок и новые версии 256-разрядных инструкций, поддерживающих встроенное округление. Дополнительное использование 512-разрядного вектора возможно на поддерживаемых P-ядрах, но не на E-ядрах, и будущие процессоры Xeon на базе Core будут продолжать поддерживать все инструкции Intel AVX-512 для обеспечения обратной совместимости.

Новая векторная ISA также принесет некоторые преимущества в производительности:

- Приложения, скомпилированные в Intel AVX2, повторно скомпилированные в Intel AVX10, должны обеспечить прирост производительности без необходимости дополнительной настройки программного обеспечения.

- Приложения Intel AVX2, чувствительные к давлению на векторные регистры, получат наибольшую производительность благодаря 16х дополнительным векторным регистрам и новым инструкциям.

- Многопоточные векторизуемые приложения, скорее всего, будут достигать более высокой совокупной пропускной способности при работе на процессорах Intel Xeon с E-ядром или на продуктах Intel с высокопроизводительной гибридной архитектурой.

Существующие приложения Intel AVX-512, многие из которых уже используют максимальные 256-битные векторы, должны показывать ту же производительность при компиляции в Intel AVX10/256 с длиной изо-вектора, в то время как приложения, которые могут использовать большие длины векторов, будут поддерживаться на Intel P. -только ядра.

Intel заявляет, что версия 1 векторной ISA AVX10 (AVX10.1) сначала будет реализована на процессорах Intel Xeon «Granite Rapids», запуск которых, согласно некоторым сообщениям в СМИ, ожидается к 2024 или 2025 году, поэтому, скорее всего, это займет некоторое время. задолго до того, как AVX10.2 будет реализован на процессорах с E-ядрами.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.