Одно из основных преимуществ архитектуры RISC-V заключается в том, что она открыта, поэтому любая организация с нужными навыками может разрабатывать свои собственные ядра, и правительство Индии воспользовалось этой возможностью, разработав Программу развития микропроцессоров (MDP), которая помогает разрабатывать ядра VEGA RISC-V на местном уровне.

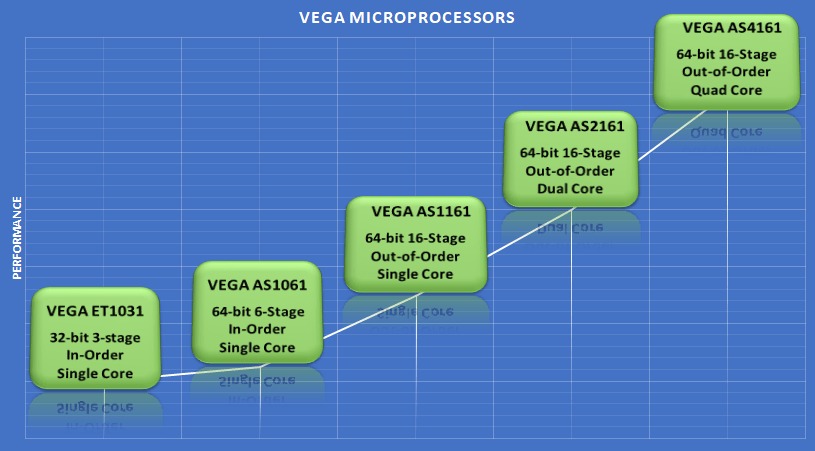

Благодаря финансированию Министерства электроники и информационных технологий (MeitY) Центру развития перспективных вычислений (C-DAC) удалось разработать пять процессоров RISC-V, начиная от одноядерного 32-разрядного микроконтроллера класса RISC-V процессора на четырехъядерный 64-разрядный неупорядоченный процессор с поддержкой Linux.

Основные характеристики пяти ядер VEGA, разработанных C-DAC:

- VEGA ET1031 – 32-разрядный одноядерный 3-ступенчатый встроенный процессор RV32IM с шиной AHB/AXI4., дополнительный MMU, дополнительная отладка

- VEGA AS1061 – 64-разрядный одноядерный 6-ступенчатый процессор RV64IMAFDC с 8 КБ D-кэша, 8 КБ I-кэша, FPU, шиной AHB/AXI4

- VEGA AS1161 – 64-разрядный одноядерный 16-ступенчатый конвейерный процессор RV64IMAFDC с 32 КБ D-кэшем, 32 КБ I-кэшем, FPU, шиной AHB/AXI4/ACE

- VEGA AS2161 – 64-разрядный двухъядерный 16-ступенчатый конвейерный процессор RV64IMAFDC с 32 КБ D-кэша, 32 КБ I-кэша, 512 КБ кэша L2, FPU, шины AHB / AXI4 / ACE

- VEGA AS4161 – 64-битный четырехъядерный 16-ступенчатый конвейерный процессор RV64IMAFDC с 32 КБ D-кэша, 32 КБ I-кэша, 1024 КБ кэш-памяти L2, FPU, шины AHB / AXI4 / ACE

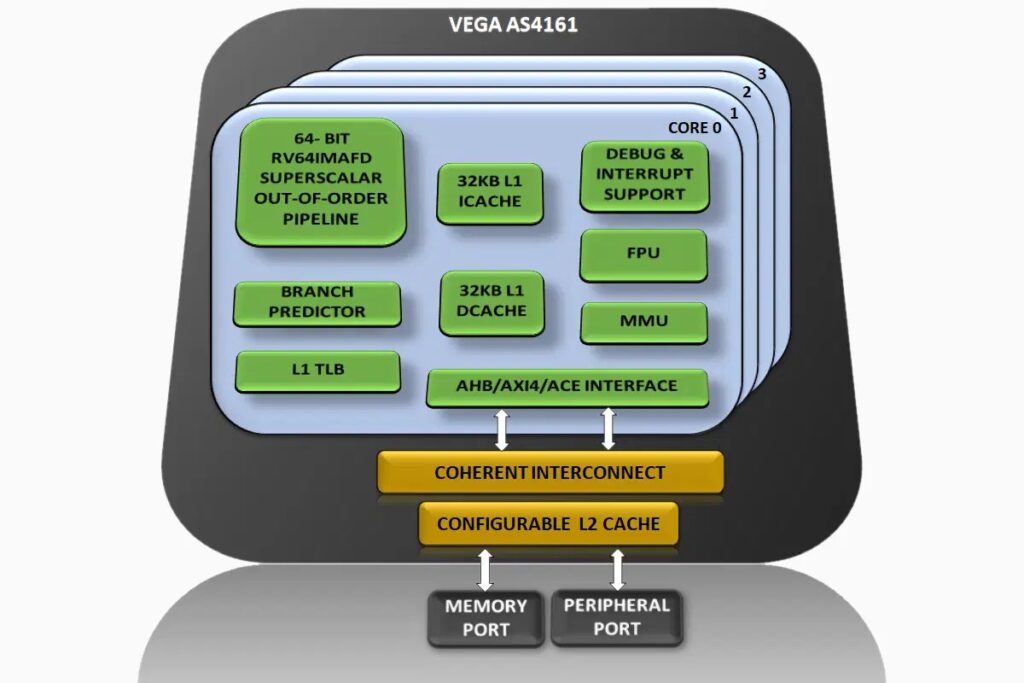

Подробнее об основных характеристиках высокопроизводительного VEGA AS4161:

- Архитектура набора инструкций RISC-V 64G (RV64IMAFD)

- Реализация 13-16 стадий аварийного конвейера

- Расширенный предсказатель ветвлений: BTB, BHT, RAS

- Архитектура Harvard, отдельные инструкции и память данных

- Уровни привилегий пользовательского, супервизорного и машинного режимов

- Полнофункциональная подсистема памяти с поддержкой Linux

- Блок управления памятью

- Виртуальная память на основе страниц

- Настраиваемый кэш L1

- Настраиваемый кэш L2

- Высокопроизводительное многоядерное соединение

- Высокопроизводительный блок операций с плавающей запятой, совместимый со стандартом IEEE 754-2008

- AXI4-/ACE, совместимый внешний интерфейс

- Контроллер прерываний на уровне платформы

- до 127 IRQ

- Низкая задержка прерывания

- Поддержка векторных прерываний

- Расширенный встроенный контроллер отладки

- JTAG-совместимый интерфейс

- Поддержка точек останова HW/SW

- Расширение отладки, позволяющее отлаживать Eclipse через соединение GDB >> openOCD >> JTAG.

- Совместимость с Linux

В ближайшее время не следует ожидать появления процессора для настольных Linux, поскольку AS4161 в основном предназначен для хранения данных и сетевых приложений.

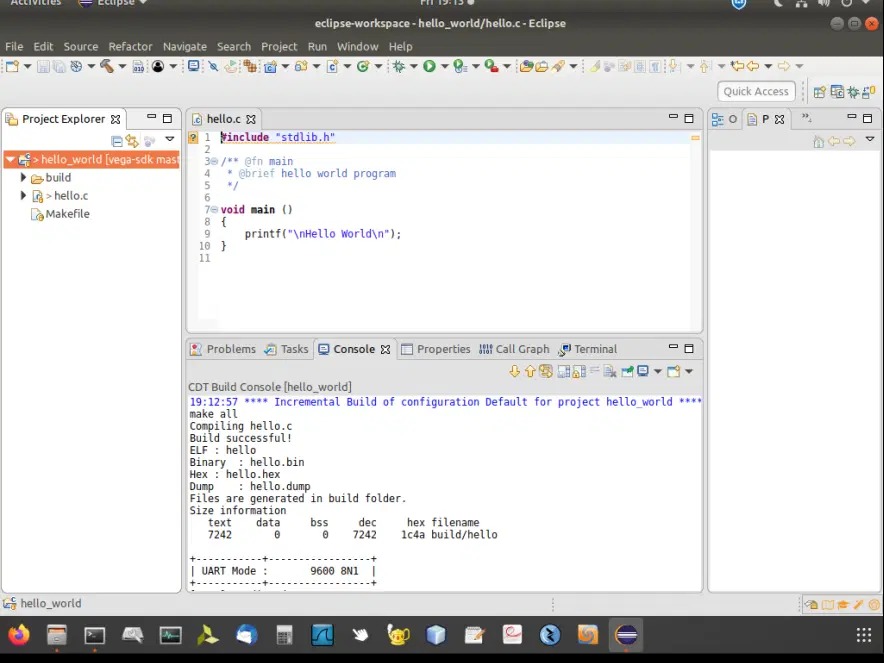

Что еще лучше, так это общедоступная документация для двух SoC — THEJAS32 и THEJAS64 — на базе ядер VEGA ET1031 и VEGA AS1061 соответственно, с кодом HDL, работающим на плате ARTY A7 FPGA (A7-35T может запускать THEJAS32, но A7-100T необходим для THEJAS64). C/C++ VEGA SDK с Eclipse IDE позволяет инженерам разрабатывать программы для платформы, а также предоставляется исходный код Linux для 64-разрядных процессоров VEGA. Код размещен на Gitlab , но вам нужно запросить доступ, прежде чем получить код… Это немного разочаровывает.

Правительство Индии также планирует проводить учебные курсы для процессоров VEGA, но эта страница в настоящее время пуста. Нам не удалось найти никакой информации о графике выпуска кремния VEGA и о том, будет ли производство в Индии осуществляться по плану. Блог проекта не обновлялся несколько месяцев, но 31 января 2022 года на YouTube-аккаунт «VEGA Processor» было загружено видео с обзором пяти процессоров VEGA RISC-V.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.