Если вы работали с процессорными ядрами ISA с открытым стандартом RISC-V, высока вероятность, что вы столкнулись с WARP-V. Для новичков WARP-V — это генератор ядра процессора RISC-V, написанный на TL-Verilog (Transaction-Level Verilog), который поддерживает не только RISC-V, но и MIPS ISA. WARP-V уже давно обсуждается из-за его беспрецедентной архитектурной масштабируемости при небольшом объеме кода.

Знаменитая пословица «Голь на выдумки хитра» применима к изобретению TL-Verilog, а вместе с тем и к генератору ядра процессора WARP-V. На протяжении десятилетий сотни инженеров работали над проектированием одного ядра процессора, которое было более сложным в гонке за достижение более высокой одноядерной производительности. Но с последними разработками в полупроводниковой промышленности разработчик и инженер Стив Гувер, обладающий десятилетним опытом проектирования процессорных ядер, выдвинул идею разработки ядра WARP-V всего за 1,5 недели без использования передовых микроархитектурных технологий процессора.

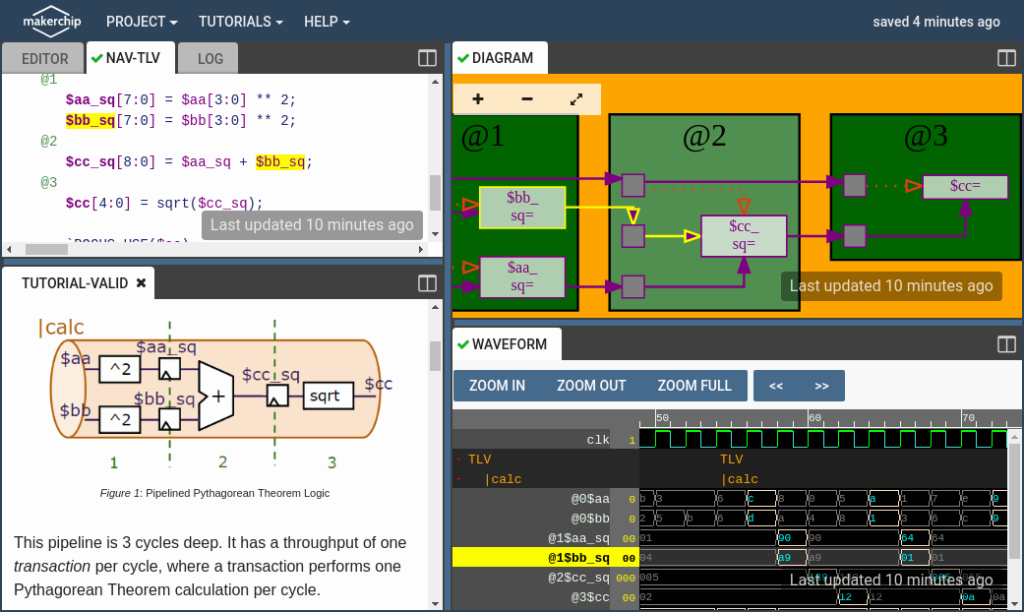

Нам приходит в голову один важный вопрос: зачем нужен еще один HDL, TL-Verilog, когда у нас есть Verilog и VHDL. (Спойлер: TL-Verilog не является языком описания оборудования). Для этого есть несколько причин, например, разработка процессора должна быть краткой, гибкой и ясной. С TL-Verilog размер кода уменьшается почти вдвое для глубины конвейера от 1 до 7 циклов по сравнению с SystemVerilog. Это происходит потому, что модели TL-Verilog вдвое меньше их эквивалента Verilog. Когда мы смотрим на другие HDL, они больше работают с описанием статических проектов, но это не было концепцией TL-Verilog, поскольку он создан для процесса проектирования, следовательно, это язык проектирования оборудования.

Что такое генератор ядер процессора WARP-V?

Возвращаясь к ядру WARP-V, с точки зрения гибкости ядра, оно позволяет реализовать одноступенчатый процессор, такой как микроконтроллер, или даже семиступенчатый процессор общего назначения. Поскольку это проект с открытым исходным кодом, теперь вы можете использовать небольшой исходный код, чтобы сделать его подходящим для вашего приложения. Процессорное ядро WARP-V включает только реализации ядра без виртуальной памяти, кеша и операций ввода-вывода. Благодаря настраиваемому ISA теперь вы можете добавлять дополнительные расширения RISC-V, такие как базовый набор целочисленных инструкций (E), стандартное расширение для целочисленного умножения и деления (M), числа с плавающей запятой одинарной точности (F) и манипуляции с битами (B).

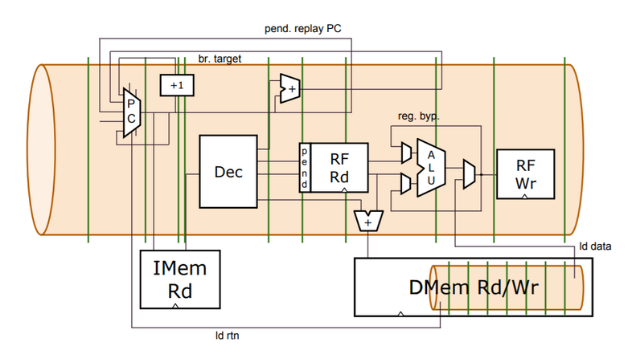

Когда мы смотрим на микроархитектуру дизайна процессора WARP-V, мы можем заметить, что каждая вертикальная зеленая линия разделяет этапы виртуального конвейера. Все эти этапы виртуального конвейера можно сопоставить с одним физическим этапом или с разными физическими этапами. Поскольку это реализация RISC-V, декодирование, расчет цели перехода и регистр отображаются на один и тот же физический этап. Код разработан с использованием макропроцессора M4, с помощью которого вы можете взять сгенерированный код в качестве исходного кода и настроить микроархитектуру.

Но когда мы говорим о гибкости ядра, чтобы удовлетворить это, также должно быть гибкое верификационное моделирование. Как проект с открытым исходным кодом, он дает возможность многим участникам поработать и понять уровень интеграции при разработке ядра. На GSoC (Google Summer of Code) 2018 студент магистратуры Делфтского технического университета Акос Хаднаги вместе со Стивом Гувером представили преимущества использования и гибкость TL-Verilog для верификационного моделирования.

Что дальше с WARP-V?

Прежде чем говорить о будущих разработках с WARP-V, давайте сначала разберемся, как начать работу с этим генератором ядра процессора. Чтобы настроить WARP-V, вы можете изменить параметр в командной строке во время компиляции и отладки с помощью IDE в Makerchip. Предполагая, что вы ознакомились с учебными пособиями по TL-Verilog и Makerchip, вы выбираете, компилируете и работаете с моделью в окне “NAV-TLV». Более подробную информацию о начале работы можно найти в официальном репозитории GitHub .

Даже если WARP-V не лучший вариант, это способ демократизации процессоров. Возможно, вокруг WARP-V мало что можно сделать, но вы, безусловно, можете работать с другими связанными рабочими нагрузками, например, сделать его многоядерным для отображения потока транзакций, или, возможно, даже работать с TL-Chisel. Разработчик, Стив Гувер цитирует: «RISC-V освободил ISA. Пришло время освободить процессоры и другие компоненты. Прибереги патенты для более важных вещей».

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.