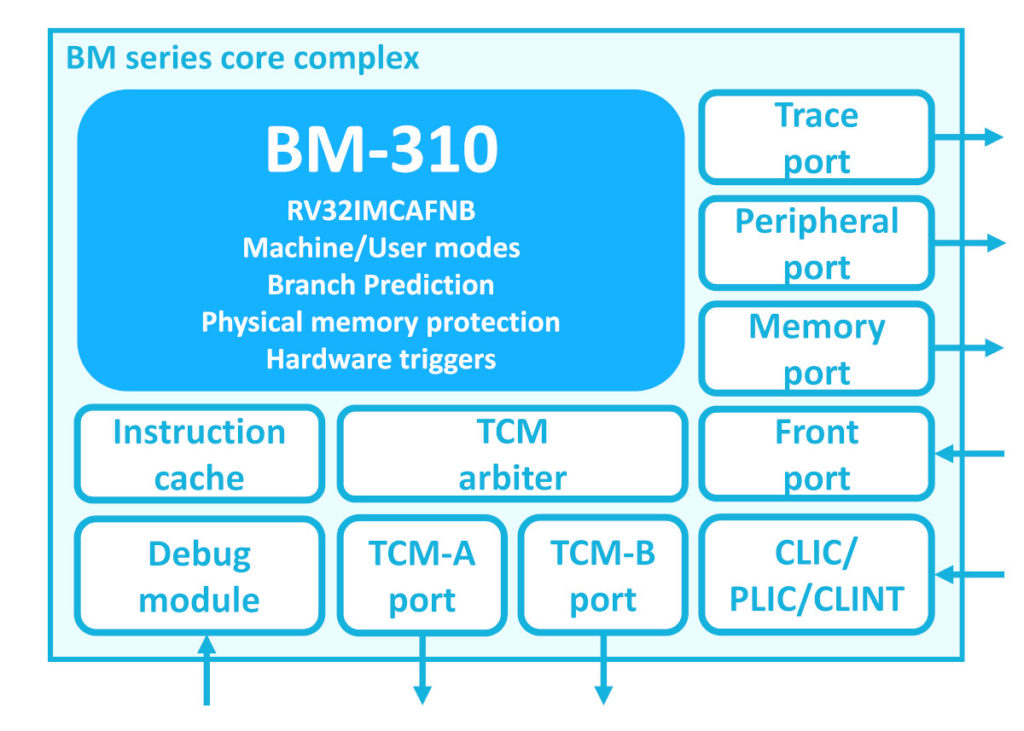

Во всем множестве микроконтроллеров RISC-V с 32-битным ядром (E20 от SiFive, VEGA ET1031 от C-DAC), на GLOBAL FORUM 2020 CloudBEAR продемонстрировала свой микроконтроллер с небольшим и эффективным 32-битным ядром — BM-310, совместимый со спецификацией RISC-V. CloudBEAR работает по предоставлению таких услуг, как настройка IP процессора, поддержка расширений RISC-V ISA, интеграция продукта в систему-на-кристалле, а также настраиваемый кэш инструкций и данных.

Давайте сначала посмотрим на процессоры CloudBEAR. Имеется три различных линейки продуктов — серия BM, серия BR и серия BI. Серия BM — небольшие и эффективные ядра микроконтроллеров. Серия BR — быстрые и компактные встраиваемые ядра. Третья и самая важная серия BI — ядрам приложений, поддерживающих Linux. В этом обзоре мы подробно рассмотрим BM-310, который является ядром микроконтроллера RISC-V для встраиваемых решений и IoT-решений.

Архитектура BM-310

Поскольку RISC-V представляет собой модульный набор команд, расширения не являются обязательными для разработчика. Архитектура BM-310 (RV32IMCAFNB) включает множество расширений ISA. Он имеет RV32I в качестве базового набора команд (32-битный RISC-V с 32 целочисленными регистрами). Другие расширения — это целочисленное умножение и деление (RV32M), сжатый режим для лучшей плотности кода (RV32C), поддержка атомарных операций (RV32A), совместимые с IEEE 754-2008 числа с плавающей запятой одинарной точности (RV32F), поддержка прерываний на уровне пользователя ( RV32N), поддержка инструкций битовой манипуляции (RV32B).

Варианты конвейера

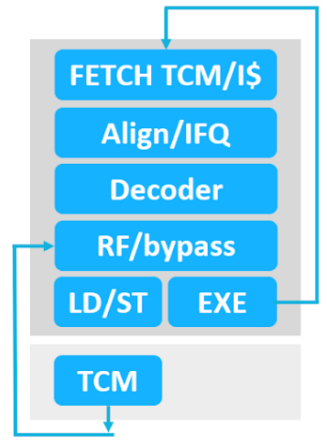

BM-310 имеет несколько вариантов конвейеров, которые позволяют клиентам настраивать свое ядро с точки зрения компромисса с производительностью. Первая конфигурация обеспечивает максимальную эффективность, тогда как четвертая конфигурация обеспечивает максимальную общую производительность.

Идеальной конфигурацией для случаев использования, требующих небольшой площади, малой мощности, а также низкой частоты, является первая конфигурация, показанная на рисунке 2. Она имеет двухступенчатый конвейер с нулевым циклом потери ветвления. Следовательно, инструкция обрабатывается в тактовом цикле, что не приводит к остановкам во время операций ветвления в конвейерном процессоре. Эта конфигурация имеет низкую частоту и максимальную эффективность без необходимости прогнозирования ветвлений.

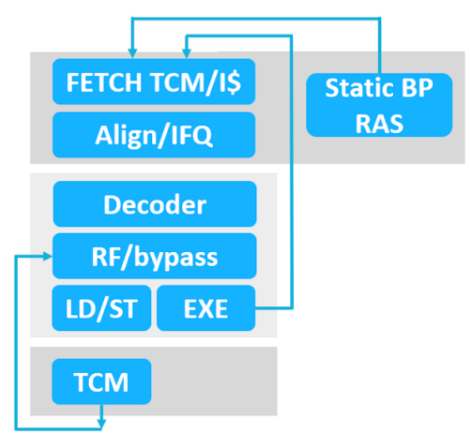

Теперь, если есть потребность в более высокой частоте и общей производительности, мы можем выбрать вторую конфигурацию (рисунок 3). В этом случае существует одна задержка за переход, что означает одну задержку при неверном прогнозе перехода. Таким образом, предсказание переходов становится необходимым для компенсации потерь за переход.

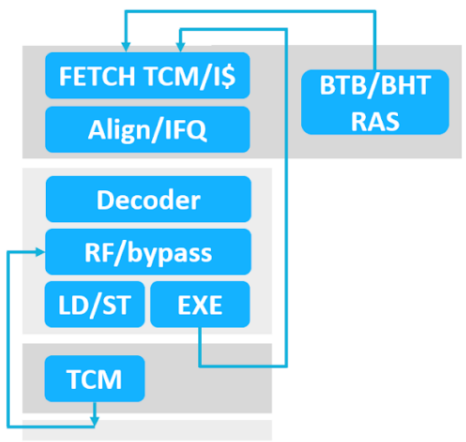

Если наблюдается дальнейшее увеличение частоты, мы выбираем третью конфигурацию (рис. 4), которая имеет трехступенчатый конвейер. Из-за увеличения частоты, нагрузка на использование задержки увеличилась до двух циклов.

Четвертая конфигурация (рис. 5) становится идеальной для достижения максимальной общей производительности. Он имеет два штрафных цикла за переход и двухцикловую нагрузку.

Дополнительные возможности

Он имеет множество дополнительных функций, таких как подсистема памяти, управление питанием, контроль прерываний, безопасность и поддержка многоядерных процессоров. Лицензирование BM-310 включает простой процесс оценки и гибкие модели лицензирования. Вариант конвейера (1) на 19% быстрее, чем эталонная машина Cortex-M4. Разработчики могут разрабатывать свои приложения для BM-310 с помощью FreeRTOS, Apache Mynewt, Zephyr Project. Наконец, BM-310 имеет низкое энергопотребление и небольшую площадь с лучшей производительностью в классе микроконтроллеров, что делает его наиболее подходящим для IoT-приложений и встраиваемых приложений. Посетите страницу процессора для получения более подробной информации.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.