В прошлом году Alibaba представила 16-ядерный процессор RISC-V XuanTie 910, заявив, что он нацелен на высокопроизводительные приложения 5G, AI и автономное вождение.

Во время виртуальной конференции Hot Chips 2020 компания предоставила более подробную информацию о процессоре Alibaba XuanTie 910 (он же XT910), сравнив ядро RV64GCV, обнаруженное в процессоре, с ядром Arm Cortex-A73.

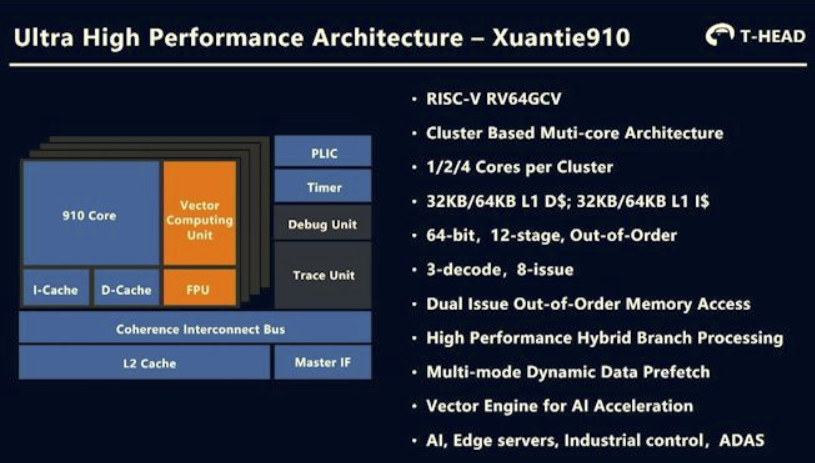

Основные характеристики и спецификации Alibaba XT910:

- CPU – до 16х64-битных ядер RISC-V (RV64GCV) с векторным расширением RISC-V и настраиваемым расширением Turbo в четырех кластерах по четыре ядра; 12-ступенчатый выход из строя; Coremark: 7,1 на МГц

- Кэш-память — 32 КБ или 64 КБ кеш-памяти ввода-вывода на ядро, до 8 МБ кэш-памяти L2 на кластер

- FP16-FP64 модуль с плавающей запятой

- Блок векторных вычислений (он же Vector Engine) для ускорения ИИ

- Управление памятью — Sv39 MMU + 8/16 PMP

- Контроллер прерываний — Clint + PLIC

- Процесс — окончательный: 12 нм FinFET; инженерные образцы: TSMC 28 нм HPC

Инструкции Alibaba RISC-V Turbo обеспечивают ускорение битовых операций, доступ к памяти, синхронизацию ядра и т. д. и показывают некоторые улучшения в тестах OpenSSL и Nbench. Их можно отключить, чтобы сохранить совместимость со «стандартным» RISC-V.

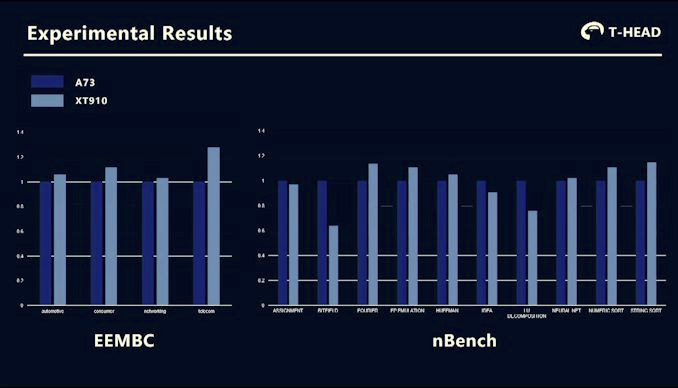

T-Head semiconductor, организация Alibaba, разработавшая микросхемы, сравнила производительность XT910 и Cortex-A73 (Kirin 970) с той же емкостью кеш-памяти L1 и показала, что они очень близки. Неясно, включали ли тесты расширение RISC-V Turbo. Будет интересно посмотреть, как пользовательские инструкции RISC-V будут осуществляться в ядре Linux, и будут ли они включены во время выполнения или/и во время компиляции.

В интервью Anandtech компания подтвердила, что KT910 — это высокопроизводительное ядро для встроенных SoC, которые можно найти в облаке и периферийных устройствах, и они работают с компаниями с открытым исходным кодом, чтобы сделать исходный код доступным, но, по-видимому, существуют юридические проблемы для высокопроизводительного ядра.

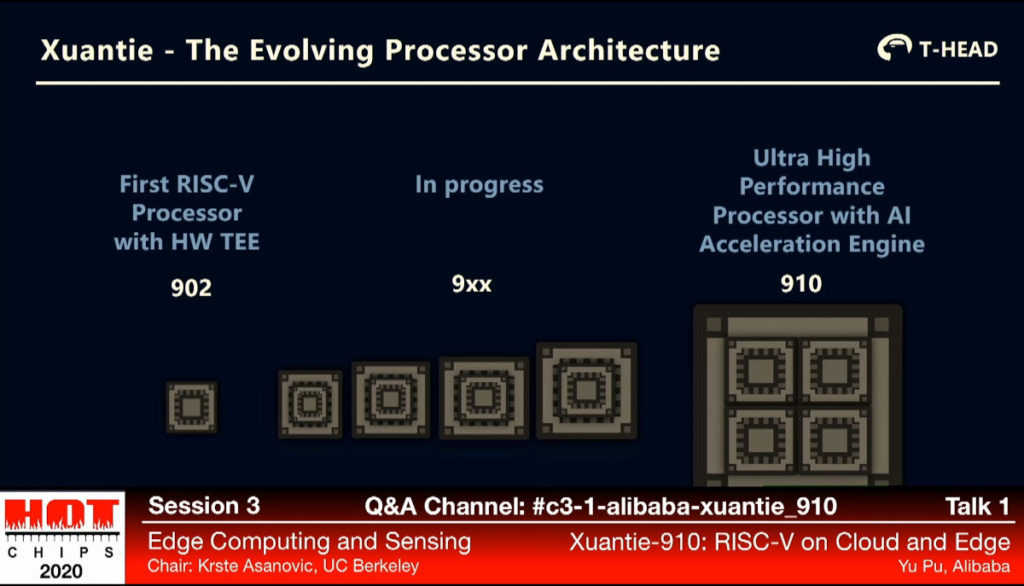

Компания работает не только над высокопроизводительными ядрами, они уже разработали ядро микроконтроллера XT902 (класс Cortex-M0 +) с аппаратным TEE, и есть планы по созданию ядер XT903, XT907, XT908, которые заполнят пробел между XT902 и XT910.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.